July 1995

ZORAN Corporation

s

1705 Wyatt Drive

s

Santa Clara, CA 95054

s

(408) 986-1314

s

FAX (408) 986-1240

PRELMINARY

s

Raster-to-block and block-to-raster conversions with strip

buffer of external SRAMs.

s

Color space conversions of RGB to/from YCbCr or YeMaCy.

s

Supports Fast Preview expansion and Lossless Compres-

sion/Expansion modes of the ZR36050.

s

Exclusive dual pixel buses. Separate format and color space

conversions on the ZR36050 data and output data during

compression and expansion.

s

Supports 4:4:4, 4:4:4:4, 4:2:2, 4:1:1 and 1:0:0 I/O formats.

s

Supports many format conversions between pixel input bus

and pixel output bus, pixel input bus and ZR36050, and

ZR36050 and pixel output bus.

s

Supports filtering for image format conversions.

s

Horizontal decimation/interpolation with optional filtering and

vertical decimation/interpolation by line dropping or

replication.

s

Enable function of pixel I/O buses for asynchronous

applications.

s

Sequential processing mode simplifies motion JPEG

implementation.

s

Provides windowing function to select processing area.

s

TTL levels for Input/Output.

s

160 pin PQFP.

The ZR36016 is a pre- and post-processor for use with a

ZR36050 JPEG Image Codec, performing raster-to-block reor-

dering and color space conversion.

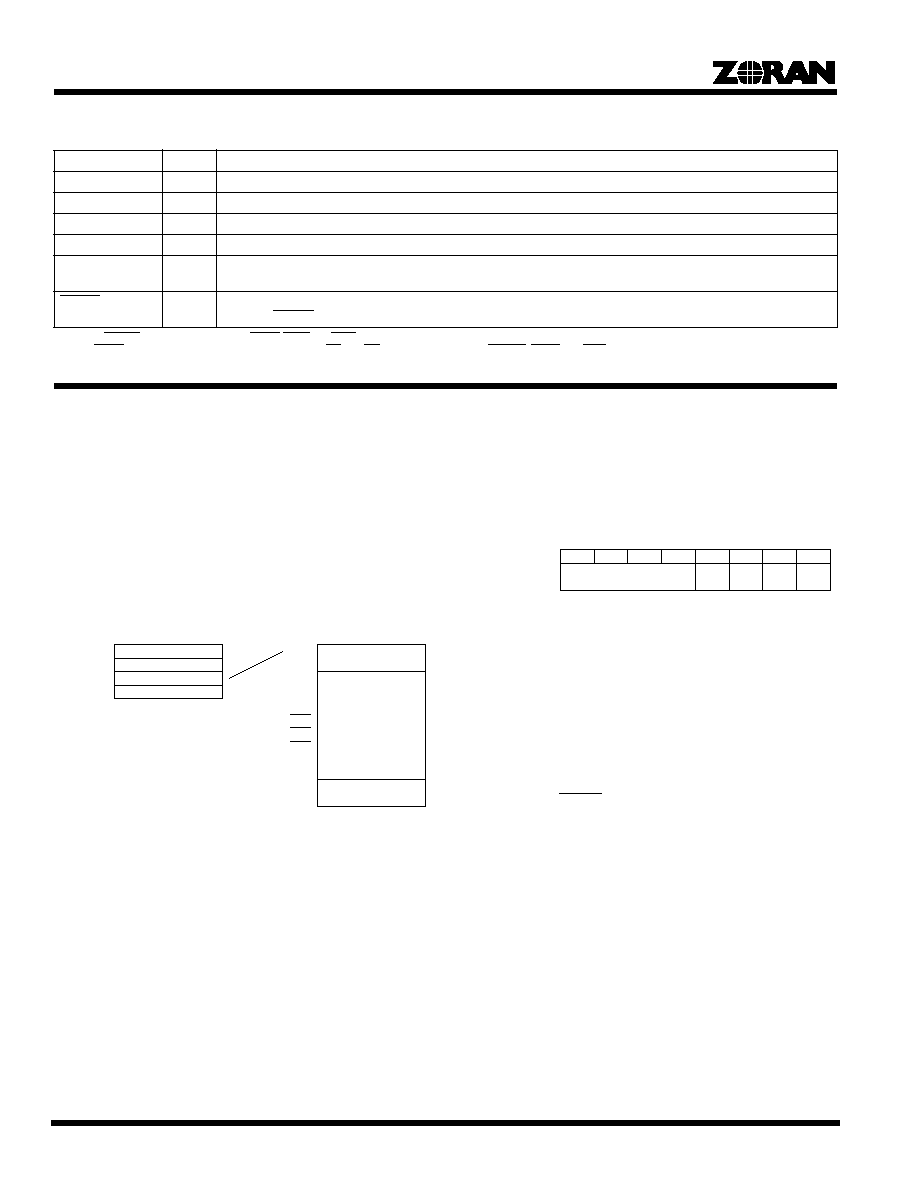

The ZR36016 accepts input pixels in a variety of common color

spaces. The pixel data can undergo format and color space con-

version, with converted data available on the pixel output bus

(Figure 1). When compressing, the data fed to the ZR36050 can

be cropped within a selected window area, and its format can be

different from that of the pixel output bus. For instance, it is

possible to output an RGB(4:4:4) input onto the pixel output bus

and to feed the ZR36050 with a YbCr(4:2:2) format. It is also

possible to output a YCbCr(4:2:2) format input as RGB(4:4:4)

and to feed the ZR36050 with a YCbCr(4:1:1) format. During

expansion, for instance, the ZR36016 can output an RGB(4:4:4)

input directly onto the output pixel bus, and after converting YCb-

Cr(4:2:2) format coming from the ZR36050 into RGB(4:4:4), it

overlays it in a window on the pixel input data.

The ZR36016 uses an external SRAM double-strip buffer for

raster-block conversions and block interleaving. The Fast

Preview and Lossless modes of operation of the ZR36050 are

also supported, in which case the SRAM is used only for raster-

to-raster buffering and pixel interleaving. Depending on the

SRAM size and the mode of operation, the maximum line length

can be up to 64K pixels. The number of lines per image can be

up to 64K.

Processing of data on the pixel buses can be continuous as

required for live frame capture or Motion JPEG, or it can be dis-

continuous, with pixels transferred only when enabled by an

enable signal.

The data transfer rate with the ZR36050 is at a maximum of

30 MHz, the system clock rate. The pixel buses transfer at a

maximum of 30 MHz for 4:0:0, or at a frequency ratio of 1, 1/2 or

1/4 of the system clock for the other formats, depending on the

format conversions that are selected.

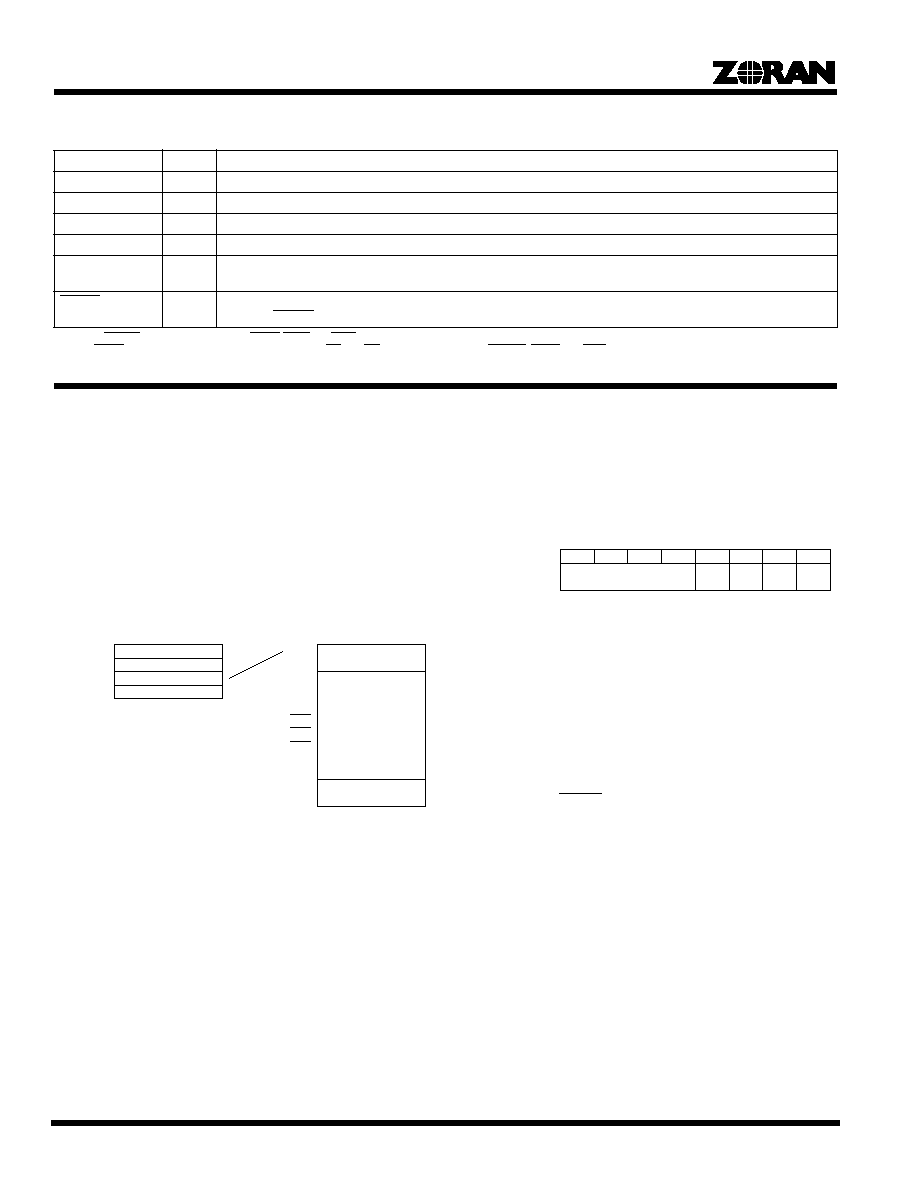

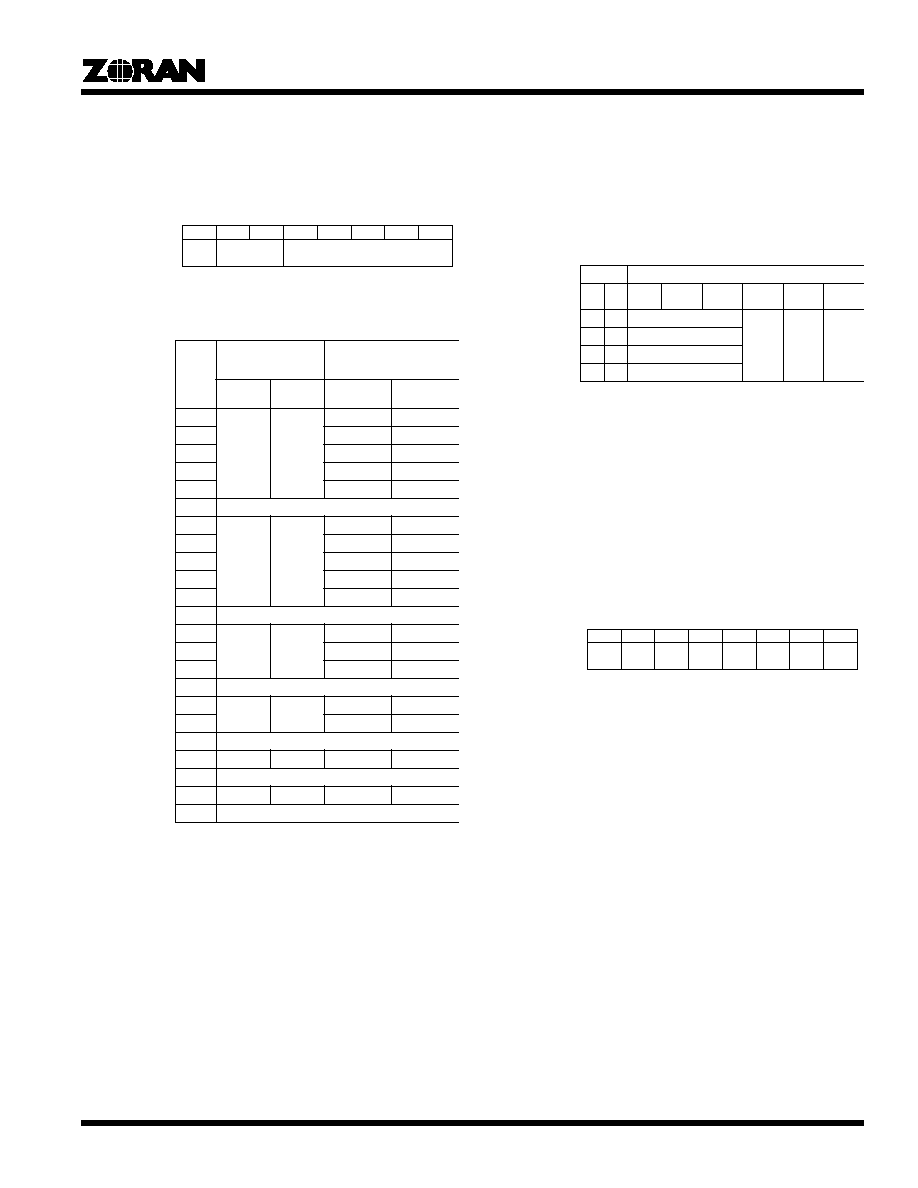

As shown in Figure 2, the input pixel data pass through a multi-

plexer, to the color space convertor. In compression, this

multiplexer always passes the pixel data (the top input). The

output of the color space convertor takes two paths in compres-

sion, one to the pixel output bus and the other to the raster to

block convertor. The data on each path can independently

undergo format conversion, which in this context means a reso-

lution transformation by decimation or interpolation, of the

chrominance components; for example, decimation from

FEATURES

DESCRIPTION

Color Space Conversion

Format Conversion

PXIN

Figure 1. ZR36016 Operations with a ZR36050

PXOUT

Window Management

Raster-to-Block

ZR36050

Compression

Color Space Conversion

Format Conversion

PXIN

PXOUT

Window Management

Block-to-Raster

ZR36050

Expansion

ZR36016

INTEGRATED COLOR SPACE / RASTER-TO-BLOCK CONVERTER

This document was created with FrameMaker 4.0.4

2

Integrated Color Space / Raster-To-Block Converter

YCrCb(4:4:4) to YCrCb(4:2;2). Format convertor #2 can perform

decimation or interpolation of chrominance, while format conver-

tor #1 can perform decimation in compression. In addition, data

passing through format convertor #1 to the raster to block con-

vertor can be decimated globally by 2, vertically and/or

horizontally, to implement half-screen or quarter-screen

compression.

In expansion, format convertor #2 can perform global horizontal

and/or vertical interpolation, as well as interpolation of chromi-

nance components. Its output is multiplexed with the pixel input

bus, so that the pixel output bus contains the expanded data

within a window on the input data. The color space convertor is

switched in or out as required, simultaneously with the multiplex-

ing of its input, so that the color space of the expanded data is

independent of that of the input.

By means of the delay element shown, the processing pipeline

delay from pixel input to output is kept constant even when color

space conversion is bypassed. The input horizontal and vertical

synchronization signals are output after undergoing an identical

delay.

The mode of operation of the ZR36016 and operating parame-

ters are determined by the control registers, which are

programmed from the host interface. There are two modes of

controlling compressions and expansions: single frame mode

and sequential mode. In the single frame mode, the ZR36016

performs the desired process on a single frame (or field in case

of interlaced motion video) and goes idle until explicitly com-

manded to perform another process. In sequential mode, a new

process starts automatically every frame or field if enabled. The

sequential mode is most suitable for motion JPEG.

VIN

Figure 2. ZR36016 Block Diagrams

HIN

PXIN

MUX

Delay

VOUT

HOUT

PXOUT

PXOE

Format

Converter #2

MUX

Delay

Color Space

Converter

MUX

Format

Converter #1

Sub-Buffer

MDATA

Raster/Block Converter

PXEN

PXCLK

MADD

MWE

MOE

SYSCLK

START

RESET

FBSY

WINDOW

CBSY

COMP

DSYNC

STOP

EOS

BDATA

Control

Registers

DATA

ADD

RD

WR

CS

3

Integrated Color Space / Raster-To-Block Converter

SIGNAL DESCRIPTIONS

1. The state of the COMP pin determines the direction of the bidirectional pins BDATA, DSYNC, STOP, and EOS. When COMP is high (the ZR36050 is in compression

mode), BDATA, DSYNC and EOS are outputs and STOP is an input. When COMP is low (the ZR36050 is in expansion mode), BDATA, DSYNC and EOS are inputs

and STOP is an output.

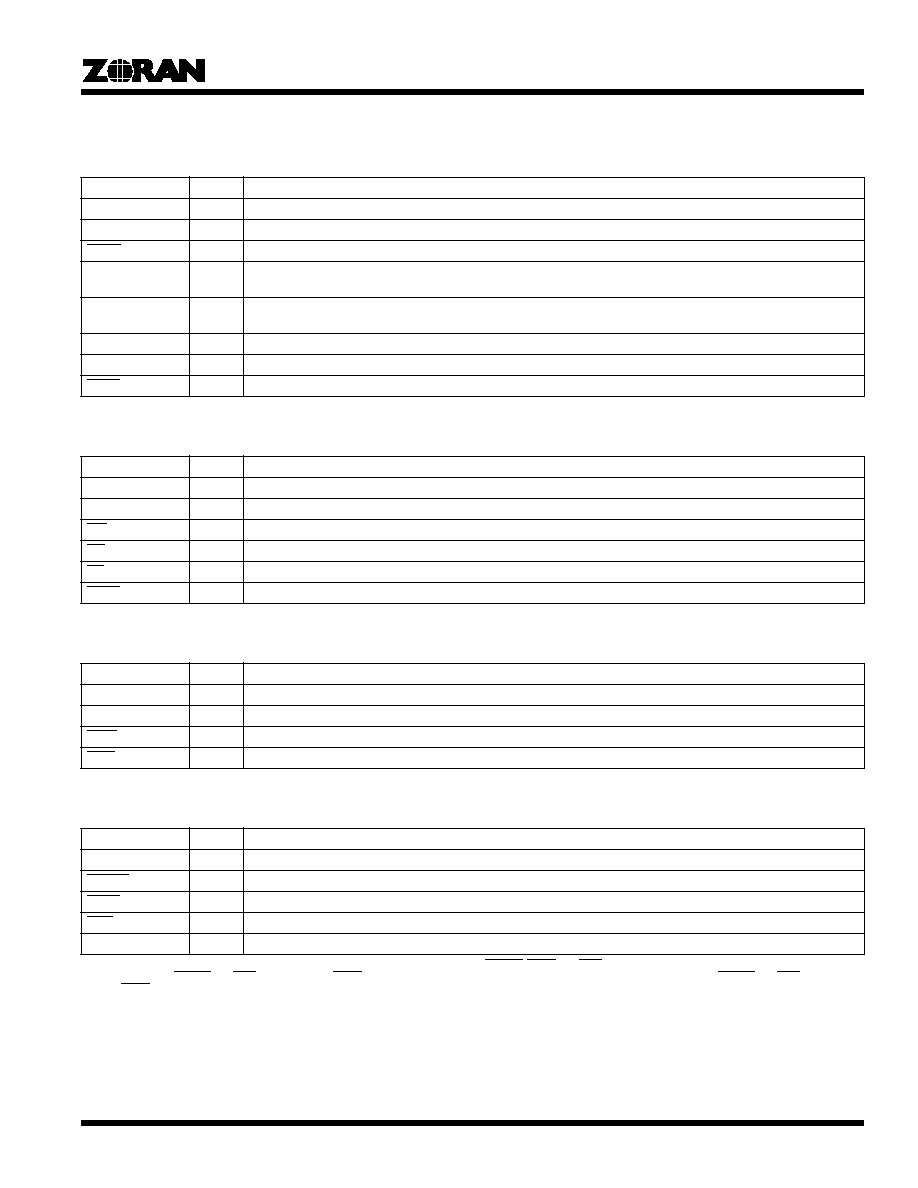

Table 1: PIXEL Input/Output

Signal

I/O

Description

PXIN[23:0]

I

Pixel data input bus.

PXOUT[23:0]

O

Pixel data output bus.

PXOE

I

PXOUT bus output enable.

HIN

I

Horizontal input data enable. Rising edge indicates beginning of scan line and start of NAX and PAX counts. For

synchronization of PXIN.

VIN

I

Vertical input data enable. Rising edge indicates beginning of picture and start of NAY and PAY counts. For synchro-

nization of PXIN.

HOUT

O

Horizontal output data enable. Follows HIN by internal processing delay. For synchronization of PXOUT.

VOUT

O

Vertical output data enable. Follows VIN by internal processing delay. For synchronization of PXOUT.

PXEN

I

Pixel enable for PXIN and PXOUT. For discontinuous transfers.

Table 2: Host Interface

Signal

I/O

Description

ADD[1:0]

I

Internal registers address input.

DATA[7:0]

I/O

Internal registers data bus.

WR

I

Write enable to internal registers. Written to on rising edge.

RD

I

Read enable for internal registers.

CS

I

Chip select for host interface.

CBSY

I

CODEC busy. Indicates that the pixel side is ready to exchange strip buffers, but the ZR36050 side is not ready yet.

Table 3: Strip Buffer Memory Interface

Signal

I/O

Description

MDATA[15:0]

I/O

Memory data bus for strip buffer.

MADD[15:0]

O

Memory address for strip buffer.

MWE

O

Memory write enable for strip buffer.

MOE

O

Memory output enable for reading strip buffer.

Table 4: ZR36050 Interface

Signal

I/O

Description

BDATA[7:0]

I/O

Block data bus, connected to ZR36050 PIXEL bus.

DSYNC

I/O

Block data synchronization with ZR36050.

STOP

I/O

Data flow control with ZR36050.

EOS

I/O

End of scan control with ZR36050.

COMP

[1]

I

Compression/expansion mode indicator from ZR36050.

4

Integrated Color Space / Raster-To-Block Converter

1. When RESET is active, HOUT, VOUT, CBSY, MWE and MOE are driven high, WINDOW, FBSY and MADD are driven low, PXOUT is unaffected (depends on PXIN

and PXOE as usual), DATA is unaffected (depends on CS and RD as usual), and BDATA, DSYNC, STOP, and EOS depend on COMP as usual.

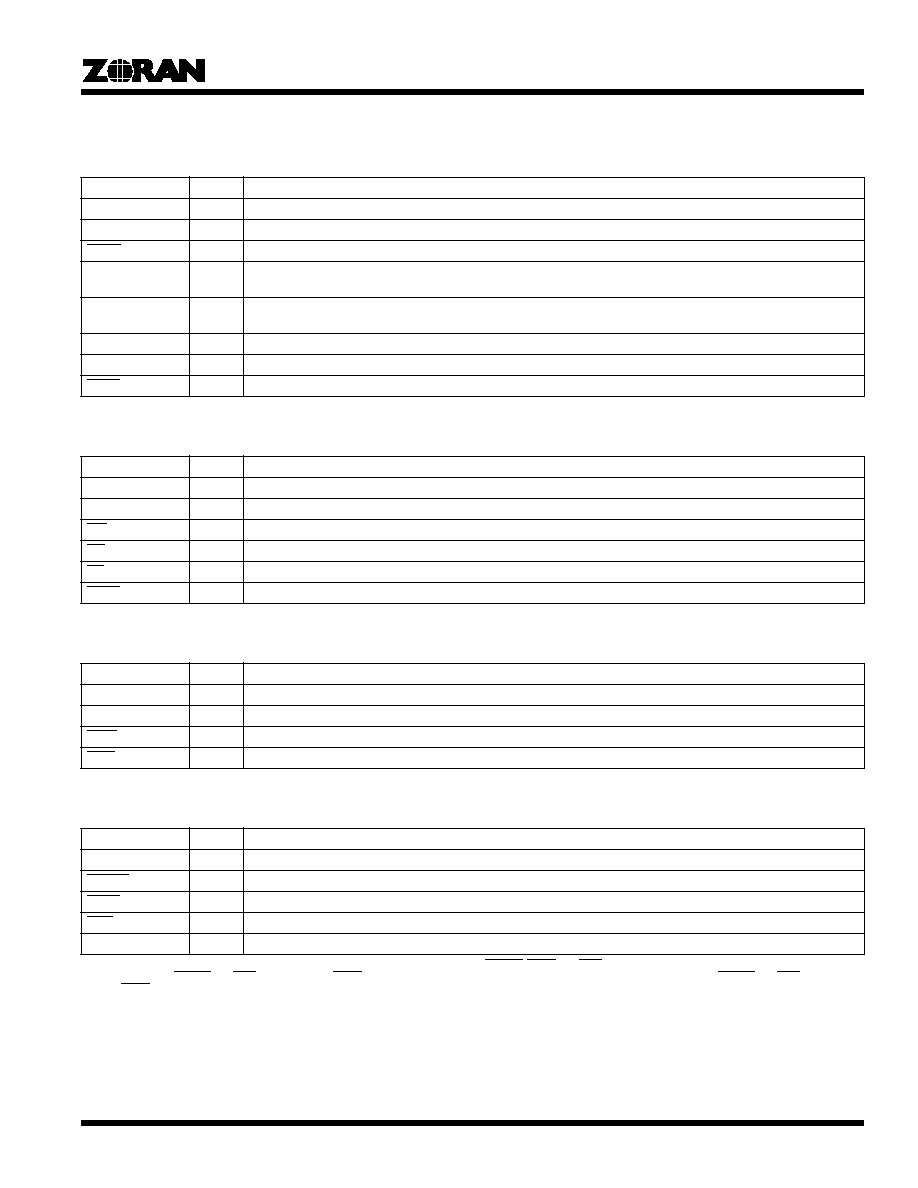

Table 5: System Interface

Signal

I/O

Description

WINDOW

O

Indicates data is within window area.

FBSY

O

Frame busy. Indicates processing of frame.

START

I

Starts processing with the rising edge in single frame mode, or enables sequential mode.

SYSCLK

I

System clock. ZR36050 bus is synchronous with this clock.

PXCLK

I

Pixel clock. HIN, VIN and PXIN are synchronous with this clock on input. HOUT, VOUT, PXOUT and WINDOW are

synchronous with this clock on output.

RESET

[1]

I

Initial hard reset. Must be held low for 8 SYSCLK cycles. Internal state remains reset for two sysclk cycles after

releasing RESET.

FUNCTIONAL DESCRIPTION

Control Registers

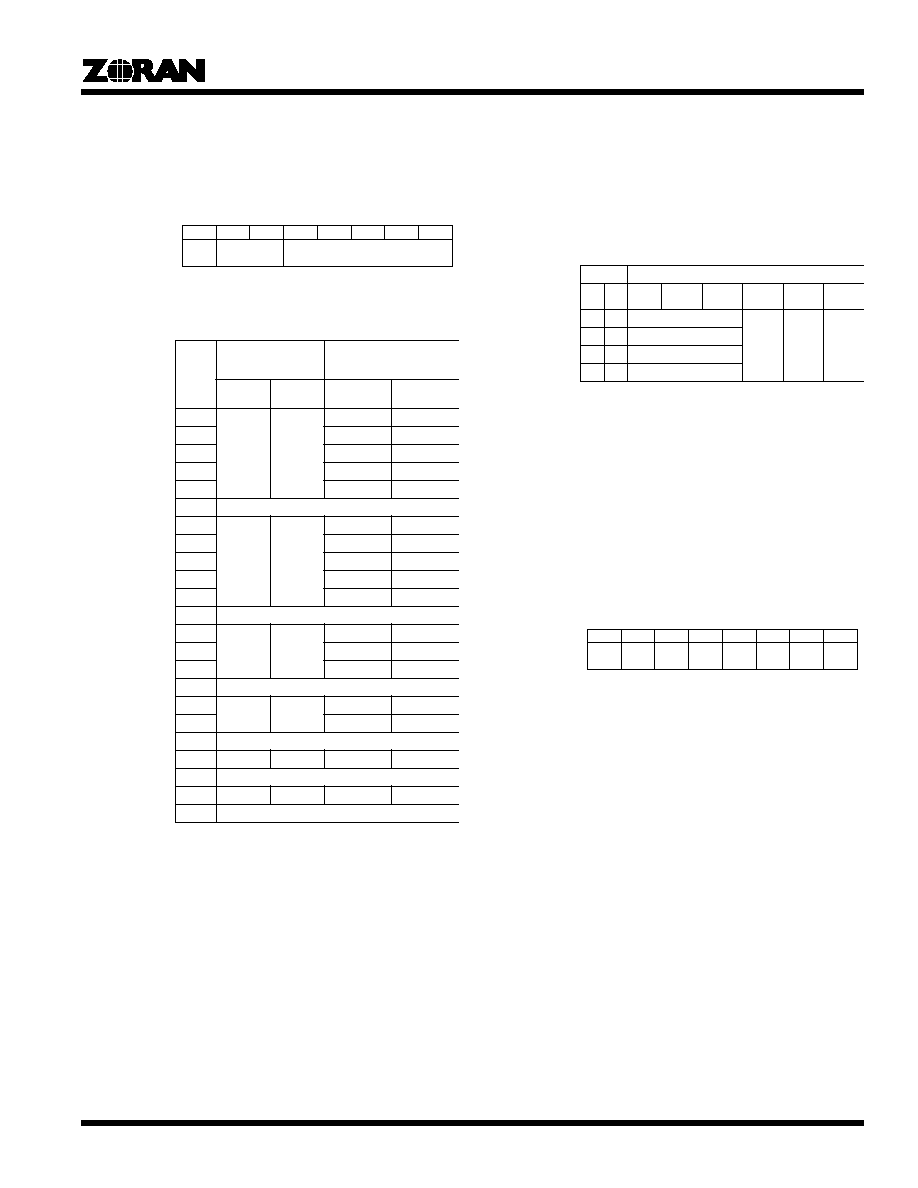

The internal control registers of the ZR36016 are shown in

Figure 3. The access to these registers is through the host inter-

face. Access to the Mode, Address Pointer and Configuration

Tables is possible only when the ZR36016 is idle or when FBSY

is not asserted.

However, it is always possible to access the GO/

STOP register.

There are four byte-wide direct access registers and twelve

byte-wide indirect access registers.

Access to the indirect registers uses the Address Pointer direct

register. Its loaded value is used to point to the location from

which accesses start in the indirect registers. For example, to

write starting from the top of the Window Area Registers section,

write 0x02 in the Address Pointer register and after that write the

data in the Indirect Data register. After the first write to the

Address Pointer register, the address pointer is incremented

automatically after each access of the Indirect Data register. The

Address Pointer register stops incrementing at 0x0B, even if the

host continues to access the Indirect Data register.

0x00

Figure 3. Control Registers

0x01

0x02

Set Registers 1 & 2

(Read/Write)

0x03

0x04

0x05

0x06

0x07

0x08

0x09

0x0A

0x0B

Window Area Registers

(Read/Write)

Number of Lines Register

(Read Only)

00

01

10

11

GO/STOP

Mode

Address Pointer

Indirect Data

(Read/Write)

ADD[1:0]

Address Pointer

Direct Access Registers

Indirect Access Registers

GO/STOP Register

Read/Write

Direct address: 0x00

Initial Value

0x00

Function

Register to enable and stop processing by the

ZR36016.

Bit 0

GO/STOP

: Processing enable and stop bit.

Initial value = 0.

0= Terminates the processing.

1= Enables processing.

A 1 in the GO/STOP bit, in concert with the START

signal, enables processing by the ZR36016. Once

the GO/STOP bit has been set, processing will be

enabled when START is high. For compression the

actual processing period starts with the following

rising edge of VIN and for expansion with the first

DSYNC. Clearing the GO/STOP bit at any time

prevents the start of any future processing.

In the single frame mode the GO/STOP bit is

cleared automatically after the single frame has

been processed, and it must be set again to process

a new frame.

In the sequential mode, when GO is set it remains

set but the processing period can be controlled with

the START signal.

Bits 1-3

Reserved.

Bits 4-7

Version Number:

The version number of the

ZR36016.

These bits contain the version number. Values start

at 0 and increment for each silicon step. Read only.

GO/

STOP

7

6

5

4

3

2

1

0

�

�

�

Version Number

5

Integrated Color Space / Raster-To-Block Converter

Mode Register

Read/Write

Direct address: 0x01

Initial Value

0x91

Function

Determines the basic operating modes and formats

of the ZR36016.

Bit 0-4

MODE

: Determines the PXIN input and ZR36050

image formats and color spaces. Initial Value =

0x11.

7

6

5

4

3

2

1

0

CMPR

DSPY

MODE

1. For Compression Only. If programmed for expansion,

then MODE = 0x16 is assumed.

2. RGB becomes YeMaCy when selected by the YMCS

bit in Setup Register 2.

3. MODE = 0x16 and 0x17 are the Philips 4:1:1 format.

Input and output pixel data use the upper 12 bits of

PXIN and PXOUT buses.

4. 4:1:1(H4V1) refers to a format in which the Cb and Cr

are decimated by 4 horizontally. 4:1:1(H2V2) refers to

a format in which the Cb and Cr are decimated by 2

horizontally and 2 vertically (sometimes known as

4:2:0 format).

5. The image format conversions implied by this table

are performed by Format Converter #1 in the block

diagram.

MODE

(HEX)

PXBIN Bus

ZR36050 Image Format

Input (Compression)

Output (Expansion)

Image

Format

Color

Space

Image

Format

Color Space

00

4:4:4

RGB

4:4:4

YCbCr

01

4:2:2

YCbCr

02

4:1:1 (H2V2)

YCbCr

03

[1]

4:0:0

Y Only

04

4:4:4

RGB

05~07

Reserved

08

4:4:4

YCbCr

4:4:4

YCbCr

09

4:2:2

YCbCr

0A

4:1:1 (H2V2)

YCbCr

0B

[1]

4:0:0

Y Only

0C

4:4:4

RGB

0D~10

Reserved

11

4:2:2

YCbCr

4:2:2

YCbCr

12

4:1:1 (H2V2)

YCbCr

13

[1]

4:0:0

Y Only

14, 15

Reserved

16

4:1:1

(PHILIPS)

YCbCr

4:1:1 (H4V1)

YCbCr

17

[1]

4:0:0

Y Only

18

Reserved

19

4:4:4:4

�

4:4:4:4

�

1A

Reserved

1B

1:0:0

�

1:0:0

�

1C~1F

Reserved

Bits 5-6

DSPY: Determines the PXOUT bus output formats.

Initial Value = 0x00.

Setting this field of the Mode register selects the

output data format of the PXOUT bus, for each

format of the PXIN bus as selected by the MODE

field of the register, as shown in the table below.

Bit 7

CMPR: Selects compression or expansion

Initial Value = 1

0 = Expansion Mode.

1 = Compression Mode.

Setup Register 1

Read/Write

Indirect address: 0x00

Initial Value

0x01

Bit 0

CNTI

: Single-Frame/Sequential processing

selection.

Initial value = 1.

0= Single Frame Mode. Processes the image enabled

by VIN and then enters an idle state. For process-

ing still images.

1= Sequential Mode. Processes sequential images in-

definitely, each VIN. For Motion JPEG.

Bit 1

RSTR:

Transparent mode selection, for raster/

raster conversion.

Initial Value = 0.

0= Selects the raster-to-block or block-to-raster con-

version mode.

1= Selects the transparent raster-to-raster mode.

For the Fast Preview lossless compression/expan-

sion functions of the ZR36050. The image formats

supported, as set by the MODE field, are 4:4:4:4,

4:4:4, 4:2:2, or 4:1:1 (H4V1) (with pixel interleave).

As the ZR36050 performs 1-D lossless only, the

setting of RSTR = 1 in 4:1:1(H2V2) format is not

permitted.

Note: The strip buffer processing delay is the same

for both modes.

Mode Register (Continued)

1. The image format conversions implied by this table

are performed by Format Converter #2 in the block

diagram.

DSPY

PXIN Bus Image Format

[1]

Bit

6

Bit

5

4:4:4

(RGB)

4:4:4

(YCbCr)

4:2:2

(YCbCr)

4:1:1

(Philips)

1:0:0

4:4:4:4

0

0

PXOUT is 4:4:4 (RGB)

PXOUT

is 4:1:1

(Philips)

PXOUT

is 1:0:0

PXOUT

is 4:4:4

0

1

PXOUT is 4:4:4 (YCbCr)

1

0

PXOUT is 4:2:2 (YCbCr)

1

1

Reserved

7

6

5

4

3

2

1

0

CKRT

VERT

HORZ

HRFL

DSFL

SBFL

RSTR

CNTI