### **SmartSwitch™**

### **General Description**

The AAT4670 SmartSwitch is a member of AnalogicTech's Application Specific Power MOS-FET™ (ASPM™) product family. The AAT4670 consists of dual, independent, 1A current limited, slew rate controlled P-channel MOSFET power switches with a dedicated source and drain pin assigned to each switch. The internal circuitry automatically derives power from the higher of the two input power source pins with a low operating guiescent current of 18µA. In shutdown mode, the supply current decreases to less than 1µA. The switches operate with inputs ranging from 2.2V to 5.5V, making them ideal for 2.5V, 3V, and 5V systems. The dual configuration permits integration of the load switch function for systems with two different power busses. Independent under-voltage lockout circuits will shut down the corresponding switch if its input voltage falls below the under-voltage lockout threshold. If the die temperature reaches the thermal limit, both switches thermal cycle off and on indefinitely without damage until the thermal condition is removed. An open drain FAULT output signals an over-current or over-temperature condition for each channel. Input logic levels are TTL compatible.

The AAT4670 is available in a Pb-free, space-saving, thermally-enhanced TDFN 3x3x0.8mm 12-lead package. The device is also available in a Pb-free 8-pin SOP, TSSOP, or MSOP package and is specified over the -40°C to +85°C temperature range.

### **Features**

- 2.2V to 5.5V Input Voltage Range

- 1A Current Limit Per Channel

- 95mΩ Typical R<sub>DS(ON)</sub>

- Fast Transient Response:

- <1µs Response to Short Circuit</p>

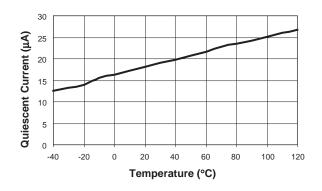

- Low 18µA Quiescent Current

- 1µA Max with Switches Off

- Slew Rate Controlled

- Thermal Shutdown

- Fault Flags with 3ms Blanking

- Under-Voltage Lockout

- Temperature Range: -40°C to +85°C

- Available in TDFN33-12, SOP-8, TSSOP-8, or MSOP-8 Package

## **Applications**

- Hot Swap Supplies

- Media Bay

- Notebook Computer

- PDA, Subnotebook

- Peripheral Ports

- USB Ports

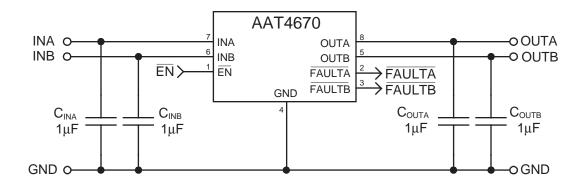

### **Typical Application**

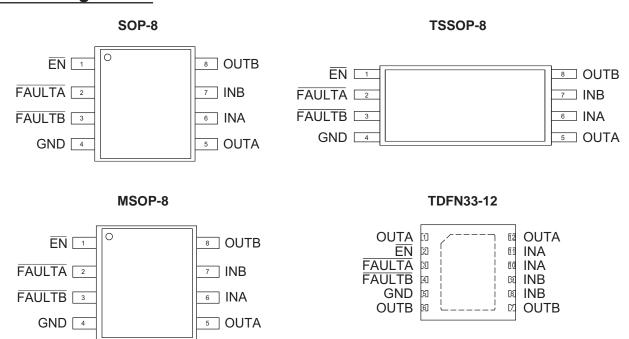

# **Pin Descriptions**

| Pin #  |            |        |                                                                                  |  |

|--------|------------|--------|----------------------------------------------------------------------------------|--|

| TDFN   | Other Pkgs | Symbol | Function                                                                         |  |

| 2      | 1          | EN     | Active-low enable input (logic low turns the switches on).                       |  |

| 3      | 2          | FAULTA | Open drain output; signals over-current for OUTA and over-temperature condition. |  |

| 4      | 3          | FAULTB | Open drain output; signals over-current for OUTB and over-temperature condition. |  |

| 5      | 4          | GND    | Ground connection.                                                               |  |

| 1, 12  | 5          | OUTA   | P-channel MOSFET drain channel A.                                                |  |

| 10, 11 | 6          | INA    | P-channel MOSFET source channel A.                                               |  |

| 8, 9   | 7          | INB    | P-channel MOSFET source channel B.                                               |  |

| 6, 7   | 8          | OUTB   | P-channel MOSFET drain channel B.                                                |  |

# **Pin Configuration**

# Absolute Maximum Ratings<sup>1</sup>

$T_A = 25$ °C, unless otherwise noted.

| Symbol                | Description                              | Value              | Units |

|-----------------------|------------------------------------------|--------------------|-------|

| $V_{INA,B}$           | INA or INB to GND                        | -0.3 to 6          | V     |

| V <sub>OUTA,B</sub>   | OUTA or OUTB to GND                      | -0.3 to 6          | V     |

| V <sub>FAULTA,B</sub> | FAULTA or FAULTB to GND                  | -0.3 to 6          | V     |

| I <sub>OUT</sub>      | Output Current                           | Internally Limited | А     |

| T <sub>J</sub>        | Operating Junction Temperature Range     | -40 to 150         | °C    |

| V <sub>ESD</sub>      | ESD Rating <sup>2</sup> - HBM            | 4000               | V     |

| T <sub>LEAD</sub>     | Maximum Soldering Temperature (at Leads) | 300                | °C    |

### Thermal Characteristics<sup>3</sup>

| Symbol         | Description                            | Value | Units |

|----------------|----------------------------------------|-------|-------|

| $\Theta_{JA}$  | Maximum Thermal Resistance (SOP-8)     | 100   | °C/W  |

| $\Theta_{JA}$  | Maximum Thermal Resistance (TDFN33-12) | 50    | °C/W  |

| P <sub>D</sub> | Maximum Power Dissipation (SOP-8)      | 1.25  | W     |

| P <sub>D</sub> | Maximum Power Dissipation (TDFN33-12)  | 2.0   | W     |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

<sup>2.</sup> Human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin.

<sup>3.</sup> Mounted on a demo board.

# **Electrical Characteristics**

$\overline{V_{IN}}$  = 5V,  $T_A$  = 25°C, unless otherwise noted. **Bold** values designate -40°C to +85°C temperature range.

| Symbol                | Description                                  | Conditions                                                                                                           | Min | Тур  | Max  | Units   |  |

|-----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|------|------|---------|--|

| V <sub>IN</sub>       | Operation Voltage                            |                                                                                                                      | 2.2 |      | 5.5  | V       |  |

| IQ                    | Quiescent Current                            | $V_{INA}$ or $V_{INB} = 5V I_{OUTA} = I_{OUTB} = 0$                                                                  |     | 18   | 40   | μA      |  |

| I <sub>Q(OFF)</sub>   | Off Supply Current                           | $\overline{\text{EN}} = V_{\text{IN}}, V_{\text{INA}} = V_{\text{INB}} = 5V, \text{OUTA, OUTB Open}$                 |     |      | 1    | μA      |  |

| I <sub>SD(OFF)</sub>  | Off Switch Current                           | $\overline{\text{EN}} = V_{\text{IN}}, V_{\text{INA}} = V_{\text{INB}} = 5V, V_{\text{OUTA}} = V_{\text{OUTB}} = 0V$ |     | 0.1  | 1    | μA      |  |

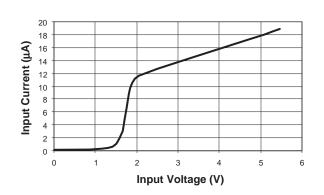

| V <sub>UVLO</sub>     | Under-Voltage Lockout                        |                                                                                                                      |     | 1.7  | 2.2  | V       |  |

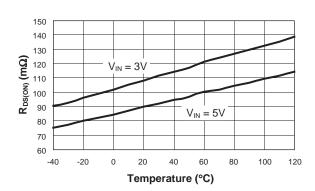

| _                     | On-Resistance Channel                        | $V_{IN} = 5.0V$                                                                                                      |     | 95   | 130  | mΩ      |  |

| R <sub>DS(ON)</sub>   | A or B                                       | $V_{IN} = 3.0V$                                                                                                      |     | 105  | 150  | 0 11152 |  |

| T <sub>CRDS</sub>     | Switch Resistance<br>Temperature Coefficient |                                                                                                                      |     | 2800 |      | ppm/°C  |  |

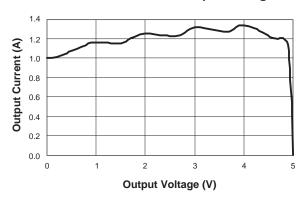

| I <sub>LIM</sub>      | Current Limit Channel A or B                 | V <sub>OUT</sub> < V <sub>IN</sub> - 0.5V                                                                            | 1.0 | 1.25 | 1.50 | Α       |  |

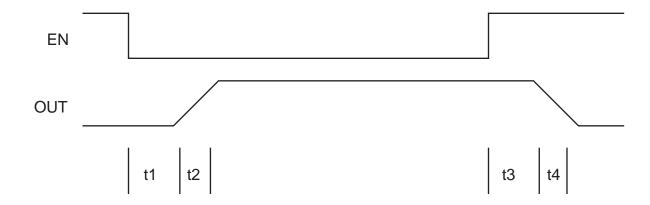

| t <sub>1</sub>        | Output Turn-On Delay Time                    | $V_{IN} = 5V$ , OUT = 0 to 10%, $R_{LOAD} = 20\Omega$                                                                |     | 100  | 1000 | μs      |  |

| t <sub>2</sub>        | Output Rise Time                             | $V_{IN} = 5V$ , OUT = 10% to 90%, $R_{LOAD} = 20\Omega$                                                              |     | 100  | 1000 | μs      |  |

| t <sub>3</sub>        | Output Turn-Off Delay Time                   | $V_{IN} = 5V$ , OUT = 100% to 90%, $R_{LOAD} = 20\Omega$                                                             |     | 10   | 20   | μs      |  |

| t <sub>4</sub>        | Output Fall Time                             | $V_{IN}$ = 5V, OUT = 90% to 10%, $R_{LOAD}$ = 20 $\Omega$                                                            |     | 5    | 20   | μs      |  |

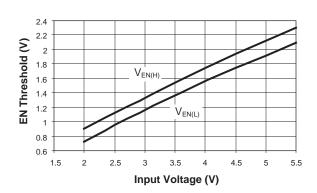

| V <sub>EN(L)</sub>    | EN Input Low Voltage                         | $V_{IN} = 2.7V \text{ to } 5.5V^{1}$                                                                                 |     |      | 0.8  | V       |  |

|                       | EN Input High Voltage                        | $V_{IN} = 2.7V \text{ to } < 3.6V$                                                                                   | 2.0 |      |      | V       |  |

| V <sub>EN(H)</sub>    | EN Input High Voltage                        | V <sub>IN</sub> = 3.6V to 5.5V                                                                                       | 2.4 |      |      |         |  |

| I <sub>EN(SINK)</sub> | EN Input Leakage                             | $V_{EN} = 5.5V$                                                                                                      |     | 0.01 | 1    | μA      |  |

| t <sub>RESP</sub>     | Current Loop Response                        | V <sub>IN</sub> = 5V                                                                                                 |     | 750  |      | ns      |  |

| V <sub>FAULTLOW</sub> | FAULT Logic Output Low                       | I <sub>SINK</sub> = 1mA                                                                                              |     |      | 0.4  | V       |  |

| I <sub>SINK</sub>     | FAULT Logic Output High                      | $V_{FAULT} = 5.5V$                                                                                                   |     | 0.5  | 1    | μΑ      |  |

|                       | Leakage Current                              |                                                                                                                      |     |      |      |         |  |

| T <sub>blank</sub>    | Fault Blanking Time                          |                                                                                                                      |     | 3    |      | ms      |  |

| T <sub>SD</sub>       | Over-Temperature Threshold                   |                                                                                                                      |     | 125  |      | °C      |  |

<sup>1.</sup> For  $\rm V_{\rm IN}$  outside this range, consult typical EN threshold curve.

# **Typical Characteristics**

#### **Quiescent Current vs. Temperature**

#### **Quiescent Current vs. Input Voltage**

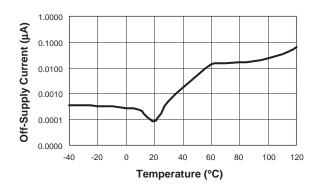

Off-Supply Current vs. Temperature

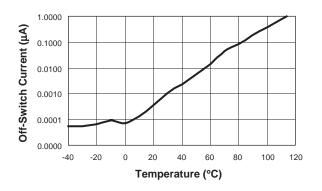

**Off-Switch Current vs. Temperature**

**Current Limit vs. Output Voltage**

R<sub>DS(ON)</sub> vs. Temperature

# **Typical Characteristics**

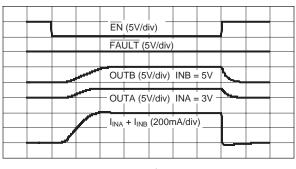

#### Turn-On/Off Response with 20 $\Omega$ 1 $\mu$ F Loads

100μs/div

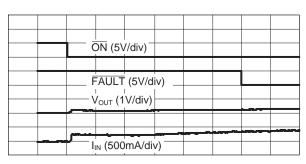

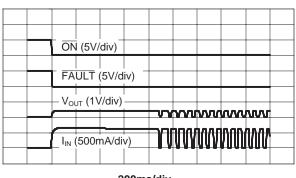

**FAULT** Delay Start Into  $0.6\Omega$  Load

500μs/div

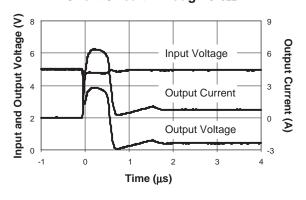

Short Circuit Through 0.6Ω

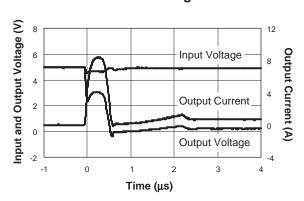

Short Circuit Through  $0.3\Omega$

**Thermal Shutdown Response**

200ms/div

Typical EN Threshold vs. Input Voltage

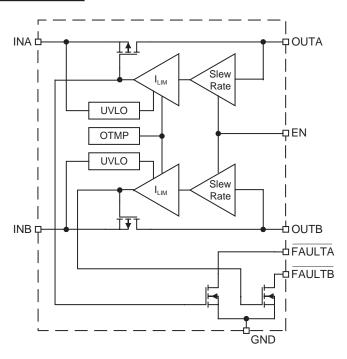

### **Functional Block Diagram**

### **Functional Description**

The AAT4670 dual channel load switch, implemented with isolated independent P-channel MOSFET devices, is ideal for applications where dual power supplies are in continuous use. Typical applications for this include products with multiple USB ports, or ports requiring protection that operate from separate power supplies. The input power supplies can be any voltage between 2.2V and 5.5V in any combination; one supply is not required to be the higher voltage. Internally, the power supply for the control circuitry will automatically switch to the higher of the two supplies. In the case where the supplies are equal, +/- 30mV of hysteresis prevents the internal supply from oscillating between the two input supplies. The low impedance P-channel MOSFET devices are identical in size, allowing for layout flexibility. They are controlled by a patented fast acting current loop and respond to short circuits in a fraction of a microsecond, easing requirements on the input capacitors. With such fast transient response time, the upstream power supply rail is naturally isolated from the protected port.

The AAT4670 is internally protected from thermal damage by an over-temperature detection circuit. If

a high ambient temperature or an over-current condition causes the die temperature to reach the internal thermal limit, both power devices are switched off until the die temperature cools to a level below the thermal limit threshold. The device will thermal cycle indefinitely until the over-current or high temperature condition is removed. Due to the high thermal conductivity of silicon and the size of the die, the temperature across the die is relatively uniform at high temperatures; therefore, as a precaution, both power devices are switched off when the thermal threshold is reached. Since the power devices operate from independent power supplies, independent undervoltage lockout circuits are employed. If the power supply to one channel falls below the under-voltage lockout threshold, the other channel will remain active. A current limit condition is reported by the open drain FAULT output associated with the appropriate channel. A thermal limit condition is reported by both FAULT outputs. A three millisecond blanking interval prevents false reporting during the charging of a capacitive load, which typically occurs during device turn-on, but may also occur during a port hot plug-in event.

The AAT4670 is ideally suited for protection of peripheral ports such as USB, PS2, and parallel ports.

### **Applications Information**

### **Input Capacitor**

The input capacitors,  $C_{INA}$  and  $C_{INB}$ , protect the input power supplies from current transients generated by loads attached to the AAT4670. If a short circuit is suddenly applied to an output of the AAT4670, there is a 750 nanosecond period during which a large current flows before current limit circuitry activates. (See characteristic curve "Short Circuit Through  $0.3\Omega$ .") In this event, a properly sized input capacitor can dramatically reduce the voltage transient seen by the power supply and other circuitry upstream from the AAT4670. CIN should be located as close to the device V<sub>IN</sub> pin as practically possible. Ceramic, tantalum, or aluminum electrolytic capacitors may be selected for C<sub>IN</sub>. There is no specific capacitor equivalent series resistance (ESR) requirement for C<sub>IN</sub>. However, for higher current operation, ceramic capacitors are recommended for C<sub>IN</sub> due to their inherent capability over tantalum capacitors to withstand input current surges from low impedance sources such as batteries in portable devices.

#### **Output Capacitor**

In order to insure stability while the current limit is active, a small capacitance of approximately  $1\mu F$  is required on each output. No matter how big the output capacitor, output current is limited to the value set by the AAT4670 current limiting circuitry, allowing very large output capacitors to be used. For example, USB ports are specified to have at least  $120\mu F$  of capacitance downstream from their controlling power switch. The current limiting circuit will allow an output capacitance of  $1000\mu F$  or more without disturbing the upstream power supply.

### **Attaching Loads**

Capacitive loads attached to the AAT4670 will charge at a rate no greater than the current limit setting.

#### **FAULT Output**

FAULT flags are provided to alert the system if an AAT4670 load is not receiving sufficient voltage to operate properly. If current limit or over-temperature circuits in any combination are active for more

than approximately three milliseconds, the associated  $\overline{FAULT}$  flag is pulled to ground through approximately  $100\Omega$ . Removal of voltage or current transients of less than three milliseconds prevents capacitive loads connected to either  $\overline{AAT4670}$  output from activating the associated  $\overline{FAULT}$  flag when they are initially attached. Pull-up resistances of  $1k\Omega$  to  $100k\Omega$  are recommended. Since  $\overline{FAULT}$  is an open drain terminal, it may be pulled up to any unrelated voltage less than the maximum operating voltage of 5.5V, allowing for level shifting between circuits.

#### **Thermal Considerations**

Since the AAT4670 has internal current limit and over-temperature protection, junction temperature is rarely a concern. However, if the application requires large currents in a hot environment, it is possible that temperature, rather than current limit, will be the dominant regulating condition. In these applications, the maximum current available without risk of an over-temperature condition must be calculated. The maximum internal temperature while current limit is not active can be calculated using Equation 1.

Eq. 1:

$$T_{J(MAX)} = I_{MAX}^2 \cdot R_{DS(ON)(MAX)} \cdot R_{\Theta JA} + T_{A(MAX)}$$

In Equation 1,  $I_{MAX}$  is the maximum current required by the load.  $R_{DS(ON)(MAX)}$  is the maximum rated  $R_{DS(ON)}$  of the AAT4670 at high temperature.  $R_{\theta JA}$  is the thermal resistance between the AAT4670 die and the board onto which it is mounted.  $T_{A(MAX)}$  is the maximum temperature that the PCB under the AAT4670 would be if the AAT4670 were not dissipating power. Equation 1 can be rearranged to solve for  $I_{MAX}$ ; Equation 2.

Eq. 2:

$$I_{MAX} = \sqrt{\frac{T_{SD(MIN)} - T_{A(MAX)}}{R_{DS(ON)(MAX)} \cdot R_{OJA}}}$$

$T_{\text{SD(MIN)}}$  is the minimum temperature required to activate the AAT4670 over-temperature protection. With typical specification of 125°C, 115°C is a safe minimum value to use.

For example, if an application is specified to operate in 50°C environments, the PCB operates at temperatures as high as 85°C. The application is sealed and its PCB is small, causing  $R_{\theta JA}$  to be approximately 120°C/W. Using Equation 2:

To prevent thermal limiting, the operating load current in the application must be less than 1.25A which lies in the current limiting range. So, in this application, any operating current below the current limit threshold is allowed.

**Eq. 3:**

$$I_{MAX} = \sqrt{\frac{115 - 85}{160m \cdot 120}} = 1.25A$$

### **Timing Diagram**

# **Ordering Information**

| Package   | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|-----------|----------------------|------------------------------------------|

| SOP-8     | 4670                 | AAT4670IAS-T1                            |

| TSSOP-8   | 4670                 | AAT4670IHS-T1                            |

| MSOP-8    | BFXYY                | AAT4670IKS-T1                            |

| TDFN33-12 |                      |                                          |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/pbfree.

### **Package Information**

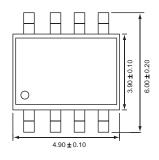

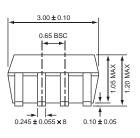

#### SOP-8

All dimensions in millimeters.

<sup>1.</sup> XYY = assembly and date code.

<sup>2.</sup> Sample stock is generally held on part numbers listed in BOLD.

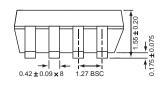

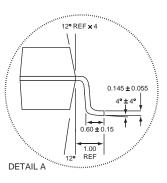

#### **TSSOP-8**

All dimensions in millimeters.

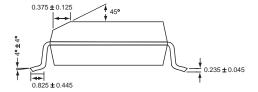

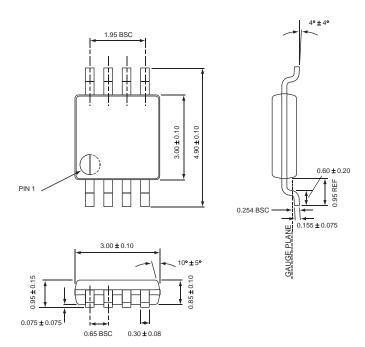

### MSOP-8

All dimensions in millimeters.

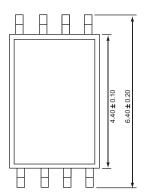

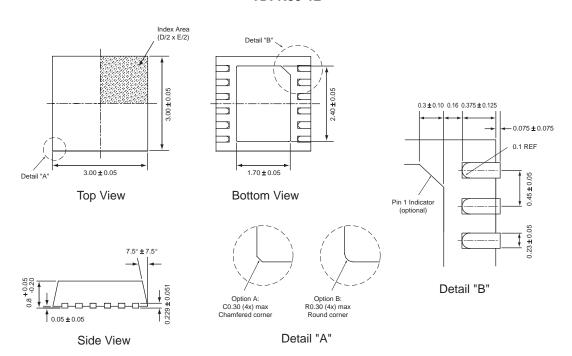

#### **TDFN33-12**

All dimensions in millimeters.

AnalogicTech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied.

AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

AnalogicTech warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with AnalogicTech's standard warranty. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed.

# Advanced Analogic Technologies, Inc.

830 E. Arques Avenue, Sunnyvale, CA 94085 Phone (408) 737-4600 Fax (408) 737-4611