### PRELIMINARY PRODUCT DATA

# Ultra-Performance, Analog Input Boards for CompactPCI® Computer Systems

#### **FEATURES**

- High performance data acquisition for embedded applications

- Space saving CompactPCI 3U form factor

- Up to 10 MHz A/D sampling rates

- Choice of 12-, 14-, or 16-bit A/D resolutions

- Wideband inputs with low harmonic distortion

- 2 to 16-channel simultaneous sampling eliminates phase skew

- On-board A/D FIFO memory holds 8192 samples

- 32 megasamples or greater data streaming

- Pre/post-trigger, gap-free, ring buffering

- · Ideal for DSP, FFT's, digital filtering, etc.

- Windows 95/98/NT® software; LabVIEW® drivers available

The CPCI-510 Family consists of several advanced-performance, data acquisition boards based on the 3U 32-bit CompactPCI Form Factor. CompactPCI is quickly becoming the preferred bus architecture choice for new embedded or ruggedized applications. CompactPCI combines desktop PCI performance and PC software compatibility with a rugged Eurocard packaging and passive backplane architecture.

With an emphasis on continuous, non-stop, high-speed streaming of A/D samples to host memory or disk, the system has been optimized for a wide range of signal-processing and data-recording applications. The CPCI-510 can collect huge amounts of "seamless" digitized data to host memory.

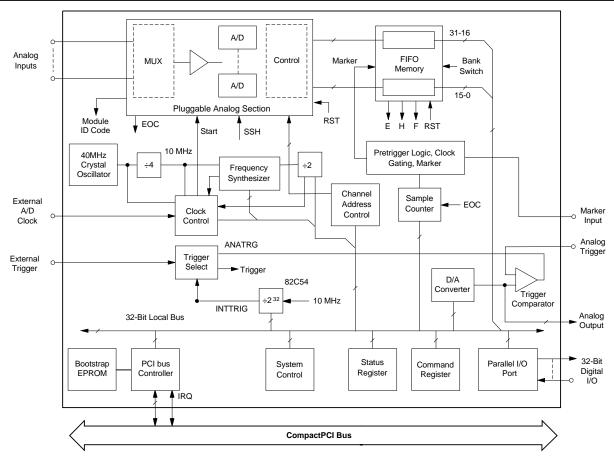

Incorporating a unique "banked" FIFO architecture, the CPCI-510 moves two A/D words in each 32-bit PCI transfer. The FIFO memory (8 Ksamples deep) serves to decouple the precise timing of the A/D converter from the block bursts of the PCI bus.

The CPCI-510's modular analog front ends utilize DATEL's low-noise, wide-bandwidth sampling A/D converters. All models exhibit excellent harmonic distortion and perform well in DSP/FFT applications. Software for Windows 95/98, NT, and LabVIEW® implements a menu-driven, no-programming", fast data recording and display system to memory or disk.

Figure 1. Simplified Block Diagram

# **Consider the Advantages of CompactPCI!**

# All the benefits of desktop PCI Computers ...

- · Leverage cost and technology of industry standard components

- Operating System Compatibility

- Application Software Compatibility

- 132 Mbyte/second PCI bus transfers

- · Open Architecture with 100's of suppliers

#### Improved for your demanding Test Applications!

- Robust Eurocard rackmount packaging

- Front loading cards with front signal access

- High performance bus connectors for improved reliability

- · More expansion slots than desktop PCs

- ESD/EMI protection

Several different "pluggable" analog options offer up to 16 input channels in single-ended or differential configurations, multiple input ranges, sampling rates to 10 MHz per channel, 12-, 14-, 16-bit A/D resolutions, and various simultaneous sampling configurations (A/D per channel) up to 16 channels. A/D-per-channel boards may be operated in "software differential" mode. Two A/D's are applied to the high and low legs of a single differential input signal. The two data values are then algebraically subtracted, either on the fly in real time or after all samples have been stored. Channel capacity in "software differential" is one-half the number of single-ended channels

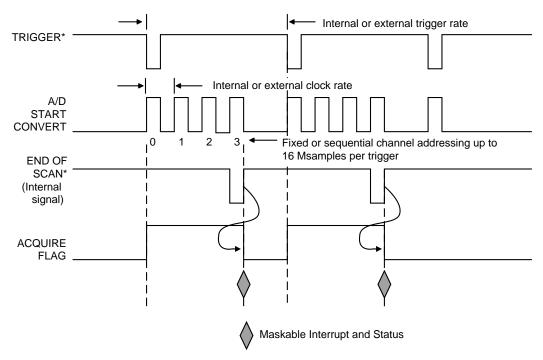

Two on-board software-programmable timebases run the A/D sample clock. A 40 MHz frequency synthesizer provides high resolution, whereas the 10 MHz 16-stage programmable divider offers very low clock jitter. If preferred, external clocks can be used for both the A/D start clock and the trigger. And several CPCI-510's can be run in parallel via external clock for many simultaneous channels. A programmable 24-bit sample counter collects long blocks up to 16 million samples. The trigger system collects a single fixed length frame, N repeating frames separated by programmable delays, or it can run "forever". Interrupts to the PCI bus are programmable from the FIFO half full flag, the bus master block transfer done, or the sample counter.

System features optimize gapless sampling without data loss. A pretrigger system can collect data continuously to host circular memory (ring buffer) of several megabytes or more. When an external trigger is received, the CPCI-510 will count down the number of preloaded post-trigger samples then automatically stop when all samples are collected. The trigger sample may then be found using a negative circular offset into the ring buffer, knowing the post-trigger sample count.

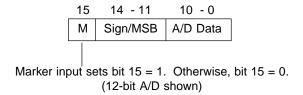

In addition, a digital marker input will tag data samples on the fly as often as needed. This provides later identification of external events without stopping sample collection. A 16 bit D/A converter is included to set the trip level to generate external analog triggers. Or the D/A can be used for analog output. Plus 16 digital inputs and 16 digital outputs are available.

Like any PC hardware, the CPCI-510 needs software to command and control it. Data acquisition, data display and data storage applications are available for Windows® 95/98, Windows® NT, and National Instrument's LabVIEW®. Simply install the software on your CompactPCI system and you will be acquiring and storing data within minutes. When data acquisition is complete, any third party data processing application can be used to analyze the results. Programmers developing their own code will appreciate the commented source code available for all of DATEL's software. The software was designed using common integrated development environments such as Visual C/C++.

Figure 2. CPCI-510 Timing Diagram

## **SPECIFICATIONS**

(Typical @ +25°C, dynamic conditions, unless noted)

| A/D SAMPLE CLOCK                           |                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sample Clock Sources                       | Selectable from among:                                                                                                                                                                                                                                                                                                                                                                                 |

| Frequency Synthesizer                      | <ol> <li>Frequency synthesizer</li> <li>10 MHz crystal oscillator</li> <li>20 MHz crystal oscillator</li> <li>16-stage binary divider to either 1 or 2, maximum input: 10 MHz</li> <li>External digital input Output 5-10 MHz in 625 Hz steps, further divisible by</li> <li>16-stage binary divider, all software programmable. Up</li> </ol>                                                         |

|                                            | to 40 MHz is available in 2500 Hz steps.                                                                                                                                                                                                                                                                                                                                                               |

| Total Sample Range                         | 76.3 Hz to 40 MHz                                                                                                                                                                                                                                                                                                                                                                                      |

| TRIGGER CONTROL                            |                                                                                                                                                                                                                                                                                                                                                                                                        |

| Trigger Sources                            | Analog threshold comparator using internal D/A to set trip level                                                                                                                                                                                                                                                                                                                                       |

| Trigger Response                           | <ol> <li>Internal trigger derived from 10 MHz timebase, divided by 32-stage divider (82C54). Range: 20 ns to 429.5 seconds.</li> <li>External digital trigger Selectable from among:</li> <li>Starts one frame ("single trigger mode")</li> <li>Collects repeating frames, each started by a trigger ("continuous trigger mode").</li> <li>Runs the A/D "forever" (sample counter disabled)</li> </ol> |

| A/D Samples per Frame                      | 1 to 16,777,216 samples (24-bit counter) or "forever"                                                                                                                                                                                                                                                                                                                                                  |

| Analog Trigger Input Range<br>Marker Input | ±10V Digital input which sets A/D bit 15 to logic "1" for one A/D clock cycle. Used to tag samples to external events if enabled.                                                                                                                                                                                                                                                                      |

| Pretrigger Mode                            | The sample down-counter is delayed until an external trigger. Pretrigger samples are stored in a host ring buffer for transient capture, if enabled.                                                                                                                                                                                                                                                   |

| ANALOG OUTPUT                              |                                                                                                                                                                                                                                                                                                                                                                                                        |

| Number of Channels<br>Function             | One channel Selectable from among: 1. General-purpose analog output 2. Threshold comparator for A/D trigger                                                                                                                                                                                                                                                                                            |

| Resolution<br>Output Voltage Range         | 16 bits<br>±10V at 5 mA                                                                                                                                                                                                                                                                                                                                                                                |

| Linearity                     | ±4 LSB                                                     |

|-------------------------------|------------------------------------------------------------|

| Settling Time<br>Input Coding | 6 microseconds (20V step)                                  |

|                               | Binary 2's complement                                      |

| PCI Bus                       |                                                            |

| Data Bus Size                 | 32 bits                                                    |

| PCI Controller Type           | AMCC S5933 DMA bus                                         |

|                               | master or slave mode                                       |

| Data Transfer                 | 32-bit I/O                                                 |

| Bus Transfer Mode             | Up to 2 <sup>24</sup> longwords, per PCI spec.             |

| Interrupt                     | One interrupt, selectable to                               |

|                               | INTA, B, C, or D                                           |

| Interrupt Sources             | FIFO half full, sample count                               |

|                               | reached (ACQuire flag), bus                                |

|                               | master transfer done.                                      |

| MISCELLANEOUS                 |                                                            |

| Analog Section Modularity     | The MUX-S/H-A/D module is                                  |

|                               | socketed for function                                      |

|                               | interchange.                                               |

| Analog Section                | Offset and gain per channel.                               |

| Adjustments                   | CPCI-510J/L require no                                     |

|                               | adjustments. Recommended recalibration interval is 90 days |

|                               | in stable conditions.                                      |

| Operating Temp. Range         | 0 to +60°C, no thermal shock                               |

|                               | ±5°C max per minute.                                       |

| Storage Temp. Range           | -25 to +85°C                                               |

| Humidity                      | 10% to 90%,                                                |

| Altitude                      | non-condensing<br>0 to 10,000 feet, forced                 |

| 7 miliado                     | cooling is required                                        |

| Power Required                | +5V dc @ 3A max. and                                       |

|                               | ±12V dc @ 300 mA max.                                      |

| 0 41 - 0                      | from CompactPCI backplane.                                 |

| Outline Dimensions            | 100 x 160 x 20.32 mm, 4 PH compatible to CompactPCI        |

|                               | 3U standard                                                |

| Memory Architecture           | First-In, First-Out (FIFO)                                 |

|                               | 8192 A/D samples                                           |

| LED Lamp                      | Internal light-emitting diode                              |

|                               | lamp programmable by user                                  |

| Digital I/O Port              | for diagnostics, etc. 16 in, 16 out lines, TTL/LS          |

| Digital 1/0 l Olt             | levels, 16 mA output per bit.                              |

| CONNECTORS                    | ,                                                          |

|                               |                                                            |

| CompactPCI bus                | 110 pin connector                                          |

| Front Connector               | (CompactPCI 32 bit) 100-pin connector on front             |

| Tone Confidence               | panel. Analog inputs,                                      |

|                               | external digital trigger,                                  |

|                               | external digital clock, digital                            |

|                               | I/O.                                                       |

All multiple A/D models may also be software selected as single channel only. Some models may also be short-cycle channel addressed for less than maximum channel capacity.

\*No 3.3V power is used.

#### **FUNCTIONAL SPECIFICATIONS**

(Typical at +25°C, dynamic conditions, gain = 1, unless noted)

| ANALOG INPUTS                                                                                   | CPCI-510E                                                                                              | CPCI-510G                                                       | CPCI-510H                                                       | CPCI-510J                                                    |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------|

| Number of Channels Input Configuration (non-isolated) Full Scale Input Ranges Input Overvoltage | 16 SE/8 Diff. Single Ended or Differential ±5V, ±10V, 0 to +10V (optional gain = x1 to x1K) CMV = ±10V | 2 Simultaneous  Single Ended ±5V (510G2A) or 0 to +10V (510G2B) | One SE or limited Diff. ±5V (special ranges optional) CMV = ±1V | 8 Simultaneous  Single Ended ±5V, ±10V (user selectable) [1] |

| (no damage, power on)  Overvoltage Recovery  Time, maximum  Input Impedance                     | ±12V<br>—<br>100 ΜΩ                                                                                    | ±12V<br>2μs<br>>1 MΩ                                            | ±12V<br>1μs<br>2 ΚΩ                                             | ±12V<br>—<br>8 ΚΩ                                            |

| SAMPLE/HOLD                                                                                     |                                                                                                        |                                                                 |                                                                 |                                                              |

| Acquisition Time Aperture Delay Aperture Delay Uncertainty                                      | 750 ns<br>20 ns<br>±40 ps                                                                              | 350 ns<br>20 ns<br>±70 ps                                       | 35 ns<br>±10 ns<br>3 ps RMS                                     | 400 ns<br>—<br>—                                             |

| A/D CONVERTER                                                                                   |                                                                                                        |                                                                 |                                                                 |                                                              |

| Resolution<br>Conversion Period                                                                 | 12 bits<br>500 ns                                                                                      | 14 bits<br>1 µsec                                               | 12 bits<br>100 ns                                               | 12 bits<br>2 μs<br>(all chans. in<br>simul. sampling)        |

| Number of A/D Converters                                                                        | 1                                                                                                      | 2                                                               | 1                                                               | 8                                                            |

| SYSTEM DC CHARACTERISTIC                                                                        | <b>S</b>                                                                                               |                                                                 |                                                                 |                                                              |

| Integral Non-linearity (LSB of FSR)  Differential Non-linearity                                 | ±1                                                                                                     | ±1.5                                                            | ±1.5                                                            | ±1                                                           |

| (LSB of FSR) Full Scale Temperature                                                             | ±0.75                                                                                                  | ±1                                                              | ±1                                                              | ±1                                                           |

| Coefficient (LSB per °C) Zero or Offset Temperature Coefficient                                 | ±0.1                                                                                                   | ±0.3                                                            | ±1                                                              | [1]                                                          |

| (LSB per °C)                                                                                    | ±0.1                                                                                                   | ±0.3                                                            | ±1                                                              | [1]                                                          |

| SYSTEM DYNAMIC PERFORMANCE                                                                      |                                                                                                        |                                                                 |                                                                 |                                                              |

| Sample Rate (single channel only) Sample Rate per Channel (sinul. or sequential chans.)         | 1 MHz<br>15 KHz/chan.                                                                                  | 1 MHz<br>1 MHz/chan.<br>(2 simul. chans.)                       | 10 MHz<br>—                                                     | 400 KHz<br>250 KHz/chan.<br>(8 simul. chans.)                |

| Total Harmonic Distortion                                                                       | –72 dB                                                                                                 | −80 dB                                                          | -65 dB                                                          | -75dB                                                        |

## **FOOTNOTES**

- CPCI-510J and 510L bipolar input is user-selectable ±5V or ±10V (default) per channel. Total gain error over temperature range is ±4 LSB maximum. Total zero/offset error over temperature range is ±4 LSB maximum. Monotonicity: no missing codes over temperature range.

- The CPCI-16M analog module accepts an optional surface mount precision resistor on each channel for limited gain increase. Preliminary specifications are shown. CMR = 90dB at DC, gain = 1. Input bias current = ±20 pA.

- Data output of the CPCI-14P and Q analog module is pipelined with a 4-sample delay after the first sample clock. The design is intended for semi-continuous sampling of wideband signals and is less suitable for low speed data acquisition.

- Preliminary specifications are shown for the CPCI-510P and CPCI-510Q. Contact DATEL for availability.

- Please note that the D/A section is not a streaming design.

## **FUNCTIONAL SPECIFICATIONS**

(Typical at +25°C, dynamic conditions, gain = 1, unless noted)

| ANALOG INPUTS                                            | CPCI-510L                    | CPCI-510M                   | CPCI-510P                   |  |

|----------------------------------------------------------|------------------------------|-----------------------------|-----------------------------|--|

| Number of Channels                                       | 16 Simultaneous              | 4 Simultaneous              | 4 Simultaneous              |  |

| Input Configuration (non-isolated)                       | Single Ended                 | Differential                | Single Ended                |  |

| Full Scale Input Ranges                                  | ±5V, ±10V                    | ±10V [2]                    | ±2.5V or 0 to +5V           |  |

| Tan Court input itaniges                                 | (user selectable)            | (optional gain              | (user selectable)           |  |

|                                                          | [1]                          | per channel)                |                             |  |

| Input Overvoltage                                        |                              | CMV = ±10V                  |                             |  |

| (no damage, power on)                                    | ±12V                         | ±12V                        | ±7V                         |  |

| Overvoltage Recovery                                     |                              |                             |                             |  |

| Time, maximum                                            | <br>8 KΩ                     | $ 10^{12}\Omega$            |                             |  |

| Input Impedance                                          | 8 KΩ                         | 10'2Ω                       | 1000Ω                       |  |

| SAMPLE/HOLD                                              |                              |                             |                             |  |

| Acquisition Time                                         | 400 ns                       | 2 µs                        | 80 ns                       |  |

| Aperture Delay Aperture Delay Uncertainty                | _                            | _                           | _                           |  |

| A/D CONVERTER                                            |                              |                             |                             |  |

|                                                          |                              |                             |                             |  |

| Resolution Conversion Period                             | 12 bits<br>2 μs              | 16 bits<br>5 µs             | 14 bits<br>330 ns           |  |

| Conversion remod                                         | (all chans. in               | Ο μ3                        | 330 113                     |  |

|                                                          | simul. sampling)             |                             |                             |  |

| Number of A/D Converters                                 | 16                           | 4                           | 4                           |  |

| SYSTEM DC CHARACTERISTIC                                 | S                            |                             |                             |  |

| Integral Non-linearity                                   |                              |                             |                             |  |

| (LSB of FSR)  Differential Non-linearity                 | ±2                           | ±4                          | ±3                          |  |

| (LSB of FSR)                                             | ±1                           | ±3                          | ±1.5                        |  |

| Full Scale Temperature                                   |                              |                             |                             |  |

| Coefficient (LSB per °C)                                 | [1]                          | ±1                          | ±0.5                        |  |

| Zero or Offset Temperature Coefficient                   |                              |                             |                             |  |

| (LSB per °C)                                             | [1]                          | ±1                          | ±0.5                        |  |

| SYSTEM DYNAMIC PERFORMANCE                               |                              |                             |                             |  |

| Sample Rate                                              |                              |                             | 3 MHz                       |  |

| (single channel only)                                    | 400 KHz                      | 200 KHz                     | [3]                         |  |

| Sample Rate per Channel                                  | 190 KHz/chan.                | 200 KHz/chan.               | 2.5 MHz/chan.               |  |

| (simul. or sequential chans.)  Total Harmonic Distortion | (16 simul. chans.)<br>-75 dB | (4 simul. chans.)<br>–80 dB | (4 simul. chans.)<br>-75 dB |  |

| Total Harmonio Distortion                                | 70 UD                        | 00 00                       | 7000                        |  |

#### **Marker Input**

When selected in the Command Register, the marker input tags A/D samples to an external event such as a clock timebase. The marker sets bit 15 of the A/D word to logic "1" for one sample clock cycle. Lower A/D bits still retain sign extension polarity. This tag is now stored in the FIFO along with the A/D sample. The user may do this as often as needed, and the marker can be asynchronous with the A/D sample clock. Post processing software then searches through the saved data to find each marked sample. The marker bit is not available for 16-bit A/D's.

Figure 3. Marker Sample Tagging

#### ORDERING INFORMATION

| Hardware:    |                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPCI-510E    | 16SE/8D chanels, 12 bits, Unipolar/bipolar inputs                                                                                                                                                                                                                                                  |

| CPCI-510G2A  | 2SE simultaneous chanels, 14 bits, Bipolar inputs                                                                                                                                                                                                                                                  |

| CPCI-510G2B  | 2SE simultaneous channels, 14 bits, Unipolar inputs                                                                                                                                                                                                                                                |

| CPCI-510H    | 1SE channel, 12 bits, Bipolar input                                                                                                                                                                                                                                                                |

| CPCI-510J    | 8SE simultaneous channels, 12 bits, Unipolar inputs                                                                                                                                                                                                                                                |

| CPCI-510L    | 16SE simultaneous channels, 12 bits, Unipolar inputs                                                                                                                                                                                                                                               |

| CPCI-510M    | 4D simultaneous channels, 16 bits, Bipolar inputs                                                                                                                                                                                                                                                  |

| CPCI-510P    | 4SE simultaneous channels, 14 bits, Unipolar/bipolar inputs                                                                                                                                                                                                                                        |

| PC-8506-2    | 100 conductor 2 foot cable                                                                                                                                                                                                                                                                         |

| PC-8404      | 100 screw terminal adapter board                                                                                                                                                                                                                                                                   |

| Software:    |                                                                                                                                                                                                                                                                                                    |

| CPCI-510WIN  | Installation, setup, configuration, and data collection program for Windows 95/98 and Windows NT. Includes a user control panel (GUI), allows board calibration, and saves A/D data to memory and/or disk. Includes LabVIEW VI's. Binary executables only. CPCI-510WIN is included with the board. |

| CPCI-510WINS | Source code to CPCI-510WIN. Includes Visual BASIC code. CPCI-510WIN consists of the GUI, a library of DLL's and the device drivers. Note: Full software support requires CPCI-510WINS purchase. CPCI-510WINS also includes all CPCI-510WIN binary executables.                                     |

CompactPCI is a trademark of PCI Industrial Computer Manufacturers Group

LabVIEW is a trademark of National Instruments

Windows is a trademark of Microsoft Corporation