# EM78P258N

# 8-Bit Microprocessor with OTP ROM

# Product Specification

Doc. VERSION 1.0

ELAN MICROELECTRONICS CORP. June 2005 Trademark Acknowledgments: IBM is a registered trademark and PS/2 is a trademark of IBM. Windows is a trademark of Microsoft Corporation. ELAN and ELAN logo

Copyright © 2005 by ELAN Microelectronics Corporation All Rights Reserved Printed in Taiwan

The contents of this specification are subject to change without further notice. ELAN Microelectronics assumes no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN Microelectronics makes no commitment to update, or to keep current the information and material contained in this specification. Such information and material may change to conform to each confirmed order.

In no event shall ELAN Microelectronics be made responsible for any claims attributed to errors, omissions, or other inaccuracies in the information or material contained in this specification. ELAN Microelectronics shall not be liable for direct, indirect, special incidental, or consequential damages arising from the use of such information or material.

The software (if any) described in this specification is furnished under a license or nondisclosure agreement, and may be used or copied only in accordance with the terms of such agreement.

ELAN Microelectronics products are not intended for use in life support appliances, devices, or systems. Use of ELAN Microelectronics product in such applications is not supported and is prohibited. NO PART OF THIS SPECIFICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS WITHOUT THE EXPRESSED WRITTEN PERMISSION OF ELAN MICROELECTRONICS.

# ELAN MICROELECTRONICS CORPORATION

#### Headquarters:

No. 12, Innovation Road 1 Hsinchu Science Park Hsinchu, Taiwan 308 Tel: +886 3 563-9977 Fax: +886 3 563-9966 http://www.emc.com.tw

# Europe:

# Elan Microelectronics Corp. (Europe)

Siewerdtstrasse 105 8050 Zurich, SWITZERLAND Tel:+41 43 299-4060 Fax:+41 43 299-4079 http://www.elan-europe.com

# Hong Kong: Elan (HK) Microelectronics Corporation, Ltd.

Rm. 1005B, 10/F Empire Centre 68 Mody Road, Tsimshatsui Kowloon , HONG KONG Tel: +852 2723-3376 Fax: +852 2723-7780 elanhk@emc.com.hk

#### Shenzhen:

# Elan Microelectronics Shenzhen, Ltd.

SSMEC Bldg., 3F, Gaoxin S. Ave. Shenzhen Hi-Tech Industrial Park Shenzhen, Guandong, CHINA Tel: +86 755 2601-0565 Fax: +86 755 2601-0500

#### USA:

# Elan Information Technology Group

1821 Saratoga Ave., Suite 250 Saratoga, CA 95070 USA Tel: +1 408 366-8223 Fax: +1 408 366-8220

#### Shanghai:

#### Elan Microelectronics Shanghai Corporation, Ltd.

23/Bldg. #115 Lane 572, Bibo Road Zhangjiang Hi-Tech Park Shanghai, CHINA Tel: +86 021 5080-3866 Fax: +86 021 5080-4600

# Contents

| 1 | Ger | neral D | escription                                         | . 1 |

|---|-----|---------|----------------------------------------------------|-----|

| 2 | Fea | tures   |                                                    | . 1 |

| 3 | Pin | Config  | urations (Package)                                 | . 2 |

|   | 3.1 | EM78F   | P258NP/N Pin Assignments                           | 2   |

| 4 |     |         | I Block Diagram                                    |     |

| 5 |     |         | ptions                                             |     |

|   | 5.1 |         | P258NP/N Pin Description                           |     |

| 6 | Fun |         | Description                                        |     |

| Ū | 6.1 |         | tional Registers                                   |     |

|   | 0.1 | 6.1.1   | R0 (Indirect Address Register)                     |     |

|   |     | 6.1.2   | R1 (Time Clock /Counter)                           |     |

|   |     | 6.1.3   | R2 (Program Counter) and Stack                     |     |

|   |     | 01110   | 6.1.3.1 Data Memory Configuration                  |     |

|   |     | 6.1.4   | R3 (Status Register)                               |     |

|   |     | 6.1.5   | R4 (RAM Select Register)                           |     |

|   |     | 6.1.6   | R5 ~ R6 (Port 5 ~ Port 6)                          |     |

|   |     | 6.1.7   | R7 (Port 7)                                        |     |

|   |     | 6.1.8   | R8 (AISR: ADC Input Select Register)               | .10 |

|   |     | 6.1.9   | R9 (ADCON: ADC Control Register)                   | .11 |

|   |     | 6.1.10  | RA (ADOC: ADC Offset Calibration Register)         | 12  |

|   |     | 6.1.11  | RB (ADDATA: Converted Value of ADC)                | .12 |

|   |     | 6.1.12  | RC (ADDATA1H: Converted Value of ADC)              | 13  |

|   |     | 6.1.13  | RD (ADDATA1L: Converted Value of ADC)              | .13 |

|   |     |         | RE (Interrupt Status 2 & Wake-Up Control Register) |     |

|   |     |         | RF (Interrupt Status 2 Register)                   |     |

|   |     | 6.1.16  | R10 ~ R3F                                          | .14 |

|   | 6.2 | •       | Il Purpose Registers                               |     |

|   |     |         | A (Accumulator)                                    |     |

|   |     | 6.2.2   | CONT (Control Register)                            |     |

|   |     | 6.2.3   | IOC50 ~ IOC70 (I/O Port Control Register)          |     |

|   |     | 6.2.4   | IOC80 (TCCA Control Register)                      |     |

|   |     | 6.2.5   | IOC90 (TCCB and TCCC Control Register)             |     |

|   |     | 6.2.6   | IOCA0 (IR and TCCC Scale Control Register)         |     |

|   |     | 6.2.7   | IOCB0 (Pull-Down Control Register)                 |     |

|   |     | 6.2.8   | IOCC0 (Open-Drain Control Register)                |     |

|   |     | 6.2.9   | IOCD0 (Pull-high Control Register)                 |     |

|   |     |         | IOCE0 (WDT Control & Interrupt Mask Registers 2)   |     |

|   |     |         | IOCF0 (Interrupt Mask Register)                    |     |

|   |     | o.z.12  | IOC51 (TCCA Counter)                               | .22 |

|      | 6.2.13  | IOC61 (TCCB Counter)                                    | 22 |

|------|---------|---------------------------------------------------------|----|

|      | 6.2.14  | IOC71 (TCCBH / MSB Counter)                             | 22 |

|      | 6.2.15  | IOC81 (TCCC Counter)                                    | 23 |

|      | 6.2.16  | IOC91 (Low-Time Register)                               | 23 |

|      | 6.2.17  | IOCA1 (High Time Register)                              | 24 |

|      | 6.2.18  | IOCB1 High/Low Time Scale Control Register)             | 24 |

|      | 6.2.19  | IOCC1 (TCC Prescaler Counter)                           | 25 |

| 6.3  | TCC/W   | VDT and Prescaler                                       |    |

| 6.4  | I/O Po  | rts                                                     |    |

|      | 6.4.1   | Usage of Port 5 Input Change Wake-up/Interrupt Function | 29 |

| 6.5  | RESE    | T and Wake-up                                           |    |

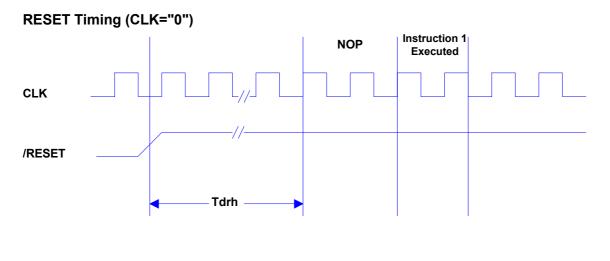

|      | 6.5.1   | RESET and Wake-up Operation                             | 29 |

|      |         | 6.5.1.1 Wake-Up and Interrupt Modes Operation Summary   | 32 |

|      |         | 6.5.1.2 Register Initial Values after Reset             | 34 |

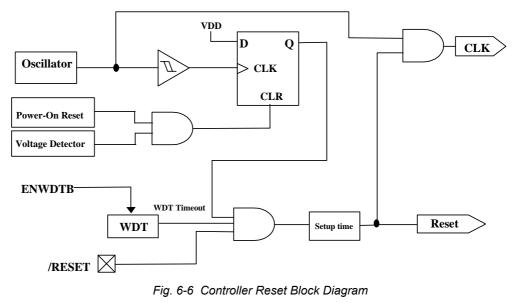

|      |         | 6.5.1.3 Controller Reset Block Diagram                  | 38 |

|      | 6.5.2   | The T and P Status under STATUS (R3) Register           | 39 |

| 6.6  | Interru | pt                                                      | 39 |

| 6.7  | Analoc  | -<br>g-To-Digital Converter (ADC)                       |    |

|      | 6.7.1   | ADC Control Register (AISR/R8, ADCON/R9, ADOC/RA)       |    |

|      |         | 6.7.1.1 R8 (AISR: ADC Input Select Register)            |    |

|      |         | 6.7.1.2 R9 (ADCON: AD Control Register)                 |    |

|      |         | 6.7.1.3 RA (ADOC: AD Offset Calibration Register)       |    |

|      | 6.7.2   | ADC Data Register (ADDATA/RB, ADDATA1H/RC, ADDATA1L/RD) |    |

|      | 6.7.3   | ADC Sampling Time                                       | 45 |

|      | 6.7.4   | AD Conversion Time                                      | 45 |

|      | 6.7.5   | ADC Operation during Sleep Mode                         | 45 |

|      | 6.7.6   | Programming Process/Considerations                      | 46 |

|      |         | 6.7.6.1 Programming Process                             | 46 |

|      |         | 6.7.6.2 Sample Demo Programs                            | 47 |

| 6.8  | Infrare | d Remote Control Application/PWM Waveform Generation    |    |

|      | 6.8.1   | Overview                                                | 49 |

|      | 6.8.2   | Function Description                                    | 50 |

|      | 6.8.3   | Programming the Related Registers                       | 52 |

| 6.9  | Timer / | / Counter                                               | 53 |

|      | 6.9.1   | Overview                                                | 53 |

|      | 6.9.2   | Function Description                                    | 53 |

|      | 6.9.3   | Programming the Related Registers                       | 55 |

| 6.10 | Oscilla | tor                                                     | 55 |

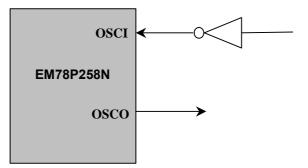

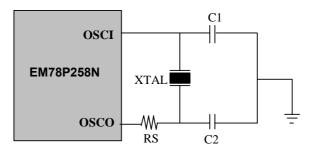

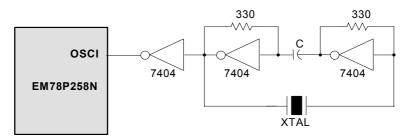

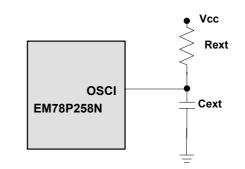

|      | 6.10.1  | Oscillator Modes                                        | 55 |

|      | 6.10.2  | Crystal Oscillator/Ceramic Resonators (XTAL)            | 56 |

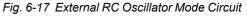

|      | 6.10.3  | External RC Oscillator Mode                             | 58 |

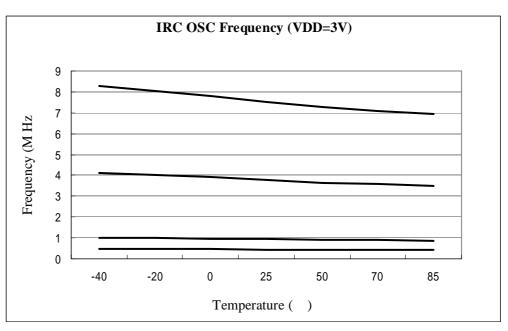

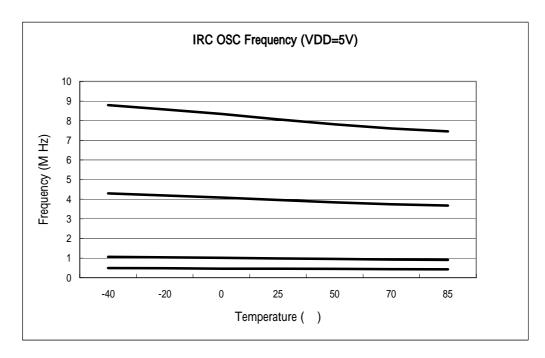

|      | 6.10.4  | Internal RC Oscillator Mode                             | 59 |

|      |         |                                                         |    |

# Contents

|    | 6.11 Power-on Considerations            | 59 |

|----|-----------------------------------------|----|

|    | 6.11.1 Programmable WDT Time-Out Period | 60 |

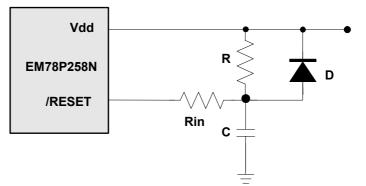

|    | 6.11.2 External Power-on Reset Circuit  | 60 |

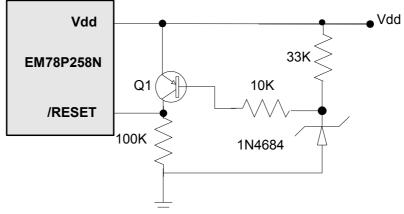

|    | 6.11.3 Residual Voltage Protection      | 60 |

|    | 6.12 Code Option                        | 62 |

|    | 6.12.1 Code Option Register (Word 0)    | 62 |

|    | 6.12.2 Code Option Register (Word 1)    | 63 |

|    | 6.12.3 Customer ID Register (Word 2)    |    |

|    | 6.13 Instruction Set                    | 64 |

| 7  | Absolute Maximum Ratings                | 66 |

| 8  | DC Electrical Characteristics           | 67 |

|    | 8.1 AD Converter Characteristics        | 68 |

|    | 8.2 Device Characteristics              | 69 |

| 9  | AC Electrical Characteristic            | 70 |

| 10 | Timing Diagrams                         | 71 |

# APPENDIX

| Package Types Summary                             | 72                                                                                                                                                        |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Packaging Configurations                          | 72                                                                                                                                                        |

| B.1 14-Lead Plastic Dual in line (PDIP) — 300 mil | 72                                                                                                                                                        |

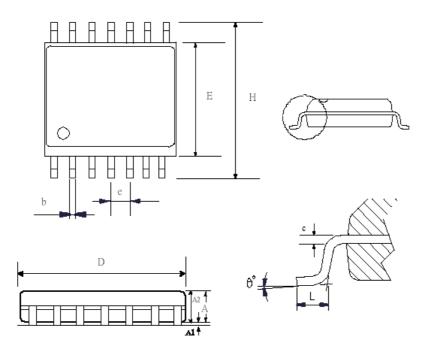

| B.2 14-Lead Plastic Small Outline (SOP) — 150 mil | 73                                                                                                                                                        |

| Quality Assurance and Reliability                 | 74                                                                                                                                                        |

| C.1 Address Trap Detect                           | 74                                                                                                                                                        |

|                                                   | Packaging ConfigurationsB.114-Lead Plastic Dual in line (PDIP) — 300 milB.214-Lead Plastic Small Outline (SOP) — 150 milQuality Assurance and Reliability |

# **Specification Revision History**

| Doc. Version | Revision Description     | Date       |

|--------------|--------------------------|------------|

| 1.0          | Initial official version | 2005/06/16 |

# **1** General Description

EM78P258N are 8-bit microprocessors designed and developed with low-power and high-speed CMOS technology. It is equipped with a 2K\*13-bit Electrical One Time Programmable Read Only Memory (OTP-ROM). With its OTP-ROM feature, it is able to offer a convenient way of developing and verifying your programs. Moreover, it provides a protect bit to guard against code intrusion, as well as 3 Code Option words to accommodate your requirements. Furthermore you can take advantage of ELAN Writer to easily write your development code into the EM78P258N.

# 2 Features

- Operating voltage range:2.3V~5.5V base on 0°C ~ 70°C (commercial)

2.5V~5.5V base on -40°C ~ 85°C (industrial)

- Operating frequency range (base on 2 clocks):

- Crystal mode:DC ~ 20MHz/2clks, 5V; DC ~ 8MHz/2clks, 3V

- RC mode: DC ~ 4MHz/2clks, 5V; DC ~ 4MHz/2clks, 3V

- Low power consumption:

- Less than 1.9 mA at 5V/4MHz

- Typically 15 μA, at 3V/32KHz

- Typically 1 µA, during sleep mode

- Built-in RC oscillator 4MHz, 8MHz, 1MHz, 455KHz (auto calibration)

- Programmable WDT time (4.5ms:18ms)

- Independent Programmable prescaler of WDT

- One configuration register to match your requirements, and user's ID code for customer use is provided

- 80× 8 on chip registers (SRAM, general purpose register)

- 2K × 13 on chip ROM

- Bi-directional I/O ports

- 8-level stacks for subroutine nesting

- 8-bit real time clock/counter (TCC) with selective signal sources, trigger edges, and overflow interrupt

- 8-bit real time clock/counter (TCCA, TCCC) and 16-bit real time clock/counter (TCCB) with selective signal sources, trigger edges, and overflow interrupt

- 4-bit multi-channel Analog-to-Digital Converter with 12-bit resolution

- Easy-implemented IR (Infrared remote control) application circuit

(This specification is subject to change without further notice)

- Power down (SLEEP) mode

- Five interrupt sources:

- TCC, TCCA, TCCB, and TCCC overflow interrupt

- Input-port status change interrupt (wake-up from sleep mode)

- External interrupt

- IR/PWM interrupt

- ADC completion interrupt

- Programmable free running watchdog timer

- 8 programmable pull-high I/O pins

- 8 programmable open-drain I/O pins

- 8 programmable pull-down I/O pins.

- Two or Four clocks per instruction cycle

- Package types:

- 14 pin DIP 300mil : EM78P258NP

- 14 pin SOP 150mil : EM78P258NN

- Power on voltage detector available (2.0V± 0.1V)

# 3 **Pin Configurations (Package)**

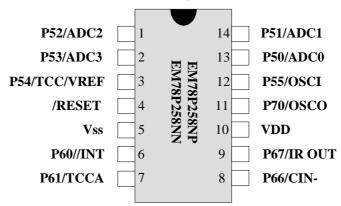

# 3.1 EM78P258NP/N Pin Assignments

Fig. 3-1 Pin Assignment – EM78P258NP/N

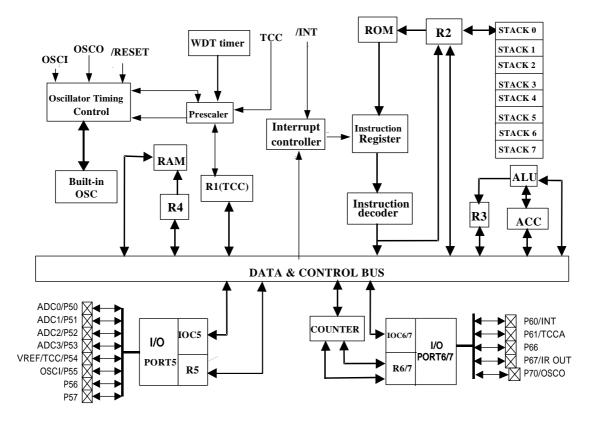

# 4 Functional Block Diagram

Fig. 4-1 EM78P258N Functional Block Diagram

# **5 Pin Descriptions**

# 5.1 EM78P258NP/N Pin Description

| Symbol               | Pin No.          | Туре | Function                                                                                                                                                                                                            |  |  |

|----------------------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDD                  | 10               | _    | Power supply                                                                                                                                                                                                        |  |  |

| OSCI                 | 12               | I    | <ul> <li>XTAL type Crystal input terminal or external clock input pin</li> <li>RC type: RC oscillator input pin</li> </ul>                                                                                          |  |  |

| OSCO                 | 11               | I/O  | <ul> <li>XTAL type: Output terminal for crystal oscillator or external clock input pin</li> <li>RC type: Clock output with a duration one instruction cycle</li> <li>External clock signal input</li> </ul>         |  |  |

| P70                  | 11               | I/O  | <ul> <li>General-purpose I/O pin</li> <li>Default value at power-on reset</li> </ul>                                                                                                                                |  |  |

| P60, P61<br>P66, P67 | 6~9              | I/O  | <ul> <li>General-purpose I/O pin</li> <li>Open_drain</li> <li>Default value at power-on reset</li> </ul>                                                                                                            |  |  |

| P50 ~ P55            | 1 ~ 3<br>12 ~ 14 | I/O  | <ul> <li>General-purpose I/O pin</li> <li>Pull_high/pull_down</li> <li>Wake up from sleep mode when the status of the pin changes</li> <li>Default value at power-on reset</li> </ul>                               |  |  |

| IR OUT               | 13               | 0    | <ul> <li>IR mode output pin.</li> <li>Driving current = 10mA when the output voltage drops to Vdd-0.5V at Vdd = 5V</li> <li>Sinking current = 15mA when the output voltage drops to GND+0.5V at Vdd = 5V</li> </ul> |  |  |

| VREF                 | 3                | I    | <ul> <li>External reference voltage for ADC</li> <li>Defined by ADCON (R9)&lt;7&gt;</li> </ul>                                                                                                                      |  |  |

| /INT                 | 6                | I    | <ul> <li>External interrupt pin triggered by falling or rising edge</li> <li>Defined by CONT &lt;7&gt;</li> </ul>                                                                                                   |  |  |

| TCC, TCCA,           | 3, 7,            | I    | <ul> <li>External Counter input</li> <li>TCC defined by CONT&lt;5&gt;</li> <li>TCCA defined by IOC80 &lt;1&gt;</li> </ul>                                                                                           |  |  |

| ADC0 ~ ADC3          | 1, 2,<br>13, 14  | I    | <ul> <li>Analog to Digital Converter</li> <li>Defined by ADCON (R9)&lt;1:0&gt;</li> </ul>                                                                                                                           |  |  |

| /RESET               | 4                | I    | <ul> <li>If it remains at logic low, the device will be reset</li> <li>Wake-up from sleep mode when pin status changes</li> <li>Voltage on /RESET/Vpp must not exceed Vdd during normal mode</li> </ul>             |  |  |

| VSS                  | 5                | _    | Ground.                                                                                                                                                                                                             |  |  |

# 6 Function Description

# 6.1 Operational Registers

# 6.1.1 R0 (Indirect Address Register)

R0 is not a physically implemented register. Its major function is to perform as an indirect address pointer. Any instruction using R0 as a pointer, actually accesses the data pointed by the RAM Select Register (R4).

# 6.1.2 R1 (Time Clock /Counter)

- Increased by an external signal edge which is defined by the TE bit (CONT-4) through the TCC pin, or by the instruction cycle clock.

- Writable and readable as any other registers

- The TCC prescaler counter (IOCC1) is assigned to TCC

- The contents of the IOCC1 register is cleared whenever

- a value is written to TCC register.

- a value is written to TCC prescaler bits (Bit3, 2, 1, 0 of the CONT register)

- during power on reset, /RESET, or WDT time out reset.

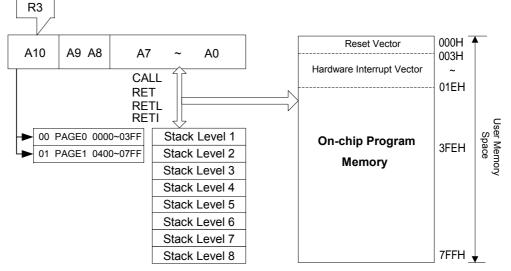

# 6.1.3 R2 (Program Counter) and Stack

Fig. 6-1 Program Counter Organization

- R2 and hardware stacks are 12-bit wide. The structure is depicted in the table under Section 6.1.3.1, *Data Memory Configuration* (next page).

- Generates 2K×13 bits on-chip ROM addresses to the relative programming instruction codes. One program page is 1024 words long.

- The contents of R2 are all set to "0"s when a RESET condition occurs.

- "JMP" instruction allows direct loading of the lower 10 program counter bits. Thus,

"JMP" allows PC to jump to any location within a page.

- "CALL" instruction loads the lower 10 bits of the PC, and then PC+1 is pushed into the stack. Thus, the subroutine entry address can be located anywhere within a page.

- "RET" ("RETL k", "RETI") instruction loads the program counter with the contents of the top of stack.

- "ADD R2, A" allows a relative address to be added to the current PC, and the ninth and above bits of the PC will increase progressively.

- "MOV R2, A" allows loading of an address from the "A" register to the lower 8 bits of the PC, and the ninth and tenth bits (A8 ~ A9) of the PC will remain unchanged.

- Any instruction (except "ADD R2,A") that is written to R2 (e.g., "MOV R2, A", "BC R2, 6",....) will cause the ninth bit and the tenth bit (A8 ~ A9) of the PC to remain unchanged.

- In the case of EM78P258N, the most significant bit (A10) will be loaded with the content of PS0 in the status register (R3) upon execution of a "JMP", "CALL", or any other instructions set which write to R2.

- All instructions are single instruction cycle (fclk/2 or fclk/4) except for the instructions that are written to R2. Note that these instructions need one or two instructions cycle as determined by Code Option Register CYES bit.

## EM78P258N 8-Bit Microprocessor with OTP ROM

# 6.1.3.1 Data Memory Configuration

|   | Address       | R PAGE registers                  |                            |                                  | IC      | OCX0 PAGE registers                                     | IO      | IOCX1 PAGE registers                               |  |  |

|---|---------------|-----------------------------------|----------------------------|----------------------------------|---------|---------------------------------------------------------|---------|----------------------------------------------------|--|--|

|   | 00            | R0 (Indirect Addressing Register) |                            |                                  | Reserve |                                                         | Reserve |                                                    |  |  |

|   | 01            | R1                                | (Time Cloc                 | ck Counter)                      | CONT    | (Control Register)                                      | Reserve |                                                    |  |  |

|   | 02            | R2                                | (Program (                 | Counter)                         |         | Reserve                                                 |         | Reserve                                            |  |  |

|   | 03            | R3                                | (Status Re                 | gister)                          |         | Reserve                                                 |         | Reserve                                            |  |  |

|   | 04            | R4                                | (RAM Sele                  | ect Register)                    |         | Reserve                                                 |         | Reserve                                            |  |  |

|   | 05            | R5                                | (Port5)                    |                                  | IOC50   | (I/O Port Control Register)                             | IOC51   | (TCCA Counter)                                     |  |  |

|   | 06            | R6                                | (Port6)                    |                                  | IOC60   | (I/O Port Control Register)                             | IOC61   | (TCCB LSB Counter)                                 |  |  |

| - | 07            | R7                                | (Port7)                    |                                  | 10C70   | (I/O Port Control Register)                             | IOC71   | (TCCB HSB Counter)                                 |  |  |

|   | 08            | R8                                | (ADC Input Select Register |                                  | IOC80   | (TCCA Control Register)                                 | IOC81   | (TCCC Counter)                                     |  |  |

|   | 09            | R9                                | (ADC Con                   | trol Register)                   | IOC90   | (TCCB and TCCC<br>Control Register)                     | IOC91   | (Low-Time Register)                                |  |  |

|   | 0A            | RA                                | (ADC Offse<br>Register)    | et Calibration                   | IOCA0   | (IR and TCCC Scale<br>Control Register)                 | IOCA1   | (High-Time Register)                               |  |  |

|   | 0B            | RB                                | ·                          | erted value<br>04 of ADC)        | ЮСВО    | (Pull-down Control<br>Register)                         | IOCB1   | (High-Time and Low-Time<br>Scale control Register) |  |  |

|   | 0C            | RC                                |                            | erted value<br>08 of ADC)        | 10000   | (Open-drain Control<br>Register)                        | IOCC1   | (TCC Prescaler Control)                            |  |  |

|   | 0D            | RD                                |                            | erted value<br>0 of ADC)         |         | (Pull-high Control Register)                            | Reserve |                                                    |  |  |

| - | 0E            | RE                                |                            | Status 2 and<br>Control Register | IOCE0   | (WDT Control Register and<br>Interrupt Mask Register 2) | Reserve |                                                    |  |  |

|   | 0F            | RF                                | (Interrupt S               | Status Register 1)               | IOCF0   | (Interrupt Mask Register 1)                             |         | Reserve                                            |  |  |

|   | 10<br>:<br>1F | General Registers                 |                            |                                  |         |                                                         |         |                                                    |  |  |

|   | 20<br>:<br>3F | Bank0 Bank1                       |                            | *                                |         |                                                         |         |                                                    |  |  |

# 6.1.4 R3 (Status Register)

| 7   | 6    | 5   | 4 | 3 | 2 | 1  | 0 |

|-----|------|-----|---|---|---|----|---|

| RST | IOCS | PS0 | Т | Р | Z | DC | С |

Bit 7 (RST): Bit of reset type

Set to "1" if wake-up from sleep on pin change, status change, or AD conversion completed. Set to "0" if wake-up from other reset types

- Bit 6 (IOCS): Select the Segment of IO control register

- 0 = Segment 0 (IOC50 ~ IOCF0) selected

- 1 = Segment 1 (IOC51 ~ IOCC1) selected

- **Bit 5 (PS0):** Page select bits. PS0 is used to select a program memory page. When executing a "JMP," "CALL," or other instructions which cause the program counter to change (e.g., MOV R2, A), PS0 is loaded into the 11th bit of the program counter where it selects one of the available program memory pages. Note that RET (RETL, RETI) instruction does not change the PS0 bit. That is, the return will always be back to the page from where the subroutine was called, regardless of the current PS0 bit setting.

| PS0 Program Memory Page [Address] |                  |  |  |  |

|-----------------------------------|------------------|--|--|--|

| 0                                 | Page 0 [000-3FF] |  |  |  |

| 1                                 | Page 1 [400-7FF] |  |  |  |

- **Bit 4 (T):** Time-out bit. Set to "1" by the "SLEP" and "WDTC" commands, or during power on and reset to "0" by WDT time-out.

- **Bit 3 (P):** Power-down bit. Set to "1" during power-on or by a "WDTC" command and reset to "0" by a "SLEP" command.

- **Bit 2 (Z):** Zero flag. Set to "1" if the result of an arithmetic or logic operation is zero.

- Bit 1 (DC): Auxiliary carry flag

- Bit 0 (C): Carry flag

# 6.1.5 R4 (RAM Select Register)

- Bit 7: Set to "0" all the time

- Bit 6: Used to select Bank 0 or Bank 1 of register

- **Bits 5~0:** Used to select a register (address: 00~0F, 10~3F) in the indirect addressing mode

See the table under Section 6.1.3.1, *Data Memory Configuration* for the configuration of the data memory.

# 6.1.6 R5 ~ R6 (Port 5 ~ Port 6)

#### **R5 & R6** are I/O registers

The upper 2 bits of R5 are fixed to "0" Only the lower 6 bits of R5 are available

The Bit2 ~ Bit5 of R6 are fixed to"0" Only Bits 1, 2, 6 and, 7 of R6 are available

# 6.1.7 R7 (Port 7)

| Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|-----------|-----|-----|-----|-----|------|------|-----|-----|

| EM78P258N | ʻ0' | ʻ0' | ʻ0' | '0' | ʻ0'  | ʻ0'  | '0' | I/O |

| ICE259N   | C3  | C2  | C1  | C0  | RCM1 | RCM0 | '0' | I/O |

|   | NOTE                                                     |

|---|----------------------------------------------------------|

| - | R7 is I/O registers                                      |

|   | With EM78P258N, only the lower 1 bit of R7 is available. |

#### Bit 7 ~ Bit 2:

[With EM78P258N]: Unimplemented, read as '0'.

[With Simulator (C3~C0, RCM1, & RCM0)]: are IRC calibration bits in IRC oscillator mode. Under IRC oscillator mode of ICE255N (with ICE259N) (simulator, these are the IRC mode selection bits and IRC calibration bits.

#### Bit 7 ~ Bit 4 (C3 ~ C0): Calibrator of internal RC mode

| C3 | C2 | C1 | C0 | Frequency (MHz) |

|----|----|----|----|-----------------|

| 0  | 0  | 0  | 0  | (1-36%) x F     |

| 0  | 0  | 0  | 1  | (1-31.5%) x F   |

| 0  | 0  | 1  | 0  | (1-27%) x F     |

| 0  | 0  | 1  | 1  | (1-22.5%) x F   |

| 0  | 1  | 0  | 0  | (1-18%) x F     |

| 0  | 1  | 0  | 1  | (1-13.5%) x F   |

| 0  | 1  | 1  | 0  | (1-9%) x F      |

| 0  | 1  | 1  | 1  | (1-4.5%) x F    |

| 1  | 1  | 1  | 1  | F (default)     |

| 1  | 1  | 1  | 0  | (1+4.5%) x F    |

| 1  | 1  | 0  | 1  | (1+9%) x F      |

| 1  | 1  | 0  | 0  | (1+135%) x F    |

| 1  | 0  | 1  | 1  | (1+18%) x F     |

| 1  | 0  | 1  | 0  | (1+22.5%) x F   |

| 1  | 0  | 0  | 1  | (1+27%) x F     |

| 1  | 0  | 0  | 0  | (1+31.5%) x F   |

**NOTE:** 1. Frequency values shown are theoretical and taken from an instance of a high frequency mode. Hence, they are shown for reference only. Definite values will depend on the actual process.

2. Similar way of calculation is also applicable to low frequency mode.

Bit 3 & Bit 2 (RCM1, RCM0): IRC mode selection bits

| RCM 1 | RCM 0 | Frequency (MHz) |

|-------|-------|-----------------|

| 1     | 1     | 4 (default)     |

| 1     | 0     | 8               |

| 0     | 1     | 1               |

| 0     | 0     | 455kHz          |

# 6.1.8 R8 (AISR: ADC Input Select Register)

The AISR register defines the pins of Port 5 as analog inputs or as digital I/O, individually.

| 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|---|---|---|---|------|------|------|------|

| - | - | - | - | ADE3 | ADE2 | ADE1 | ADE0 |

Bit 7 ~ Bit 4: Not used

Bit 3 (ADE3): AD converter enable bit of P53 pin

0 = Disable ADC3, P53 acts as I/O pin

- 1 = Enable ADC3, acts as analog input pin

- Bit 2 (ADE2): AD converter enable bit of P52 pin

- 0 = Disable ADC2, P52 acts as I/O pin

- 1 = Enable ADC2, acts as analog input pin

- Bit 1 (ADE1): AD converter enable bit of P51 pin

- 0 = Disable ADC1, P51 acts as I/O pin

- 1 = Enable ADC1, acts as analog input pin

- Bit 0 (ADE0 ): AD converter enable bit of P50 pin.

- 0 = Disable ADC0, P50 acts as I/O pin

- 1 = Enable ADC0, acts as analog input pin

# 6.1.9 R9 (ADCON: ADC Control Register)

| 7     | 6    | 5    | 4     | 3    | 2 | 1     | 0     |

|-------|------|------|-------|------|---|-------|-------|

| VREFS | CKR1 | CKR0 | ADRUN | ADPD | _ | ADIS1 | ADIS0 |

Bit 7 (VREFS): The input source of the Vref of the ADC

- 0 = The Vref of the ADC is connected to Vdd (default value), and the P54/VREF pin carries out the function of P54

- 1 = The Vref of the ADC is connected to P54/VREF

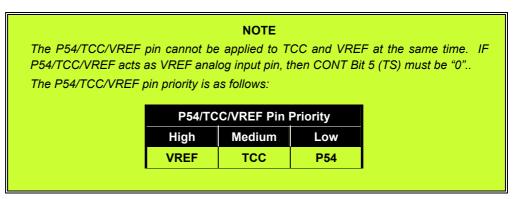

|                  |                                                                                                                                                                 | NOTE              |          |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|--|--|--|

|                  | The P54/TCC/VREF pin cannot be applied to TCC and VREF at the same time.<br>If P53/TCC/VREF acts as VREF analog input pin, then CONT Bit 5 "TS" must be<br>"0." |                   |          |  |  |  |

| ■ The P54/TCC/VF | REF pin priori                                                                                                                                                  | ity is as follow: | 5.       |  |  |  |

|                  | P53/TC                                                                                                                                                          | C/VREF Pin        | Priority |  |  |  |

|                  | High Medium Low                                                                                                                                                 |                   |          |  |  |  |

|                  | VREF TCC P54                                                                                                                                                    |                   |          |  |  |  |

|                  |                                                                                                                                                                 |                   |          |  |  |  |

Bit 6 & Bit 5 (CKR1 & CKR0): The prescaler of oscillator clock rate of ADC

00 = 1: 4 (default value)

11 = 1: WDT ring oscillator frequency

| CKR0:CKR1 | <b>Operation Mode</b> | Max. Operation Frequency |  |  |

|-----------|-----------------------|--------------------------|--|--|

| 00        | Fsco/4                | 1 MHz                    |  |  |

| 01        | Fsco/16               | 4 MHz                    |  |  |

| 10        | Fsco/64               | 16MHz                    |  |  |

| 11        | Internal RC           | 1 MHz                    |  |  |

Bit 4 (ADRUN): ADC starts to RUN.

- 1 = an AD conversion is started. This bit can be set by software

- 0 = Reset upon completion of the conversion. This bit **cannot** be reset through software

- Bit 3 (ADPD): ADC Power-down mode

- 1 = ADC is operating

- 0 = Switch off the resistor reference to save power even while the CPU is operating

- Bit 2: Not used

## Bit 1 ~ Bit 0 (ADIS1 ~ADIS0): Analog Input Select

- 00 = ADIN0/P50

- 01 = ADIN1/P51

- 10 = ADIN2/P52

- 11 = ADIN3/P53

These bits can only be changed when the ADIF bit (see Section 6.1.14, *RE (Interrupt Status 2 & Wake-Up Control Register)*) and the ADRUN bit are both LOW.

# 6.1.10 RA (ADOC: ADC Offset Calibration Register)

| 7    | 6    | 5      | 4      | 3      | 2   | 1   | 0   |

|------|------|--------|--------|--------|-----|-----|-----|

| CALI | SIGN | VOF[2] | VOF[1] | VOF[0] | "0" | "0" | "0" |

Bit 7 (CALI): Calibration enable bit for ADC offset

0 = Calibration disable

1 = Calibration enable

- Bit 6 (SIGN): Polarity bit of offset voltage

- 0 = Negative voltage

- 1 = Positive voltage

# Bit 5 ~ Bit 3 (VOF[2] ~ VOF[0]): Offset voltage bits

| VOF[2] | VOF[1] | VOF[0] | EM78P258N | ICE259N |

|--------|--------|--------|-----------|---------|

| 0      | 0      | 0      | 0LSB      | 0LSB    |

| 0      | 0      | 1      | 2LSB      | 1LSB    |

| 0      | 1      | 0      | 4LSB      | 2LSB    |

| 0      | 1      | 1      | 6LSB      | 3LSB    |

| 1      | 0      | 0      | 8LSB      | 4LSB    |

| 1      | 0      | 1      | 10LSB     | 5LSB    |

| 1      | 1      | 0      | 12LSB     | 6LSB    |

| 1      | 1      | 1      | 14LSB     | 7LSB    |

**Bit 2 ~ Bit 0:** Unimplemented, read as '0'

# 6.1.11 RB (ADDATA: Converted Value of ADC)

| 7    | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|------|------|-----|-----|-----|-----|-----|-----|

| AD11 | AD10 | AD9 | AD8 | AD7 | AD6 | AD5 | AD4 |

When the AD conversion is completed, the result is loaded into the ADDATA. The ADRUN bit is cleared, and the ADIF (see Section 6.1.14, *RE (Interrupt Status 2 & Wake-Up Control Register)*) is set.

RB is read only.

# 6.1.12 RC (ADDATA1H: Converted Value of ADC)

| 7   | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|-----|-----|-----|-----|------|------|-----|-----|

| "0" | "0" | "0" | "0" | AD11 | AD10 | AD9 | AD8 |

When the AD conversion is completed, the result is loaded into the ADDATA1H. The ADRUN bit is cleared, and the ADIF (see Section 6.1.14, *RE (Interrupt Status 2 & Wake-Up Control Register)*) is set.

RC is read only

# 6.1.13 RD (ADDATA1L: Converted Value of ADC)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 |

When the AD conversion is completed, the result is loaded into the ADDATA1L. The ADRUN bit is cleared, and the ADIF (see Section 6.1.14, *RE (Interrupt Status 2 & Wake-Up Control Register)*) is set.

RD is read only

# 6.1.14 RE (Interrupt Status 2 & Wake-Up Control Register)

| 7 | 6 | 5    | 4 | 3    | 2 | 1    | 0 |

|---|---|------|---|------|---|------|---|

| _ | _ | ADIF | - | ADWE | - | ICWE | - |

| -              | <b>NOTE</b><br><i>RE &lt;5&gt; can be cleared by instruction but cannot be set.</i><br><i>IOCE0 is the interrupt mask register.</i><br><i>Reading RE will result to "logic AND" of RE and IOCE0.</i> |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7 & Bit 6: | Not used                                                                                                                                                                                             |

| Bit 5 (ADIF):  | Interrupt flag for analog to digital conversion. Set when AD<br>conversion is completed. Reset by software<br>0 = no interrupt occurs<br>1 = interrupt request                                       |

| Bit 4 :        | Not used, fixed to "0"                                                                                                                                                                               |

| Bit 3 (ADWE):  | ADC wake-up enable bit<br>0 = Disable ADC wake-up<br>1 = Enable ADC wake-up<br>When AD Conversion enters sleep mode, this bit must be set to<br>"Enable."                                            |

| Bit 2 (CMPWE)  | Not used, fixed to "0"                                                                                                                                                                               |

| Bit 1 (ICWE): | Port 5 input change to wake-up status enable bit                           |

|---------------|----------------------------------------------------------------------------|

|               | 0 = Disable Port 5 input change to wake-up status                          |

|               | 1 = Enable Port 5 input change to wake-up status                           |

|               | When Port 5 change enters sleep mode, this bit must be set to<br>"Enable." |

Bit 0: Not implemented, read as '0'

# 6.1.15 RF (Interrupt Status 2 Register)

| 7      | 6      | 5      | 4      | 3      | 2    | 1    | 0    |

|--------|--------|--------|--------|--------|------|------|------|

| LPWTIF | HPWTIF | TCCCIF | TCCBIF | TCCAIF | EXIF | ICIF | TCIF |

| ■ F<br>■ /      | <b>NOTE</b><br>1" means interrupt request; "0" means no interrupt occurs.<br>RF can be cleared by instruction but cannot be set.<br>OCF0 is the relative interrupt mask register.<br>Reading RF will result to "logic AND" of RF and IOCF0. |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7 (LPWTIF): | Internal low-pulse width timer underflow interrupt flag for IR/PWM function. Reset by software.                                                                                                                                             |

| Bit 6 (HPWTIF): | Internal high-pulse width timer underflow interrupt flag for IR/PWM function. Reset by software.                                                                                                                                            |

| Bit 5 (TCCCIF): | TCCC overflow interrupt flag. Set when TCCC overflows. Reset by software.                                                                                                                                                                   |

| Bit 4 (TCCBIF): | TCCB overflow interrupt flag. Set when TCCC overflows. Reset by software.                                                                                                                                                                   |

| Bit 3 (TCCAIF): | TCCA overflow interrupt flag. Set when TCCC overflows. Reset by software.                                                                                                                                                                   |

| Bit 2 (EXIF):   | External interrupt flag. Set by falling edge on /INT pin. Reset by software.                                                                                                                                                                |

| Bit 1 (ICIF):   | Port 5 input status change interrupt flag. Set when Port 5 input changes. Reset by software.                                                                                                                                                |

| Bit 0 (TCIF):   | TCC overflow interrupt flag. Set when TCC overflows. Reset by software.                                                                                                                                                                     |

# 6.1.16 R10 ~ R3F

These are all 8-bit general-purpose registers.

# 6.2 Special Purpose Registers

# 6.2.1 A (Accumulator)

Internal data transfer, or instruction operand holding. It cannot be addressed.

# 6.2.2 CONT (Control Register)

| 0.2.2 00      |                 | li oi neg                                        | ister)       |               |               |              |         |  |  |  |  |  |

|---------------|-----------------|--------------------------------------------------|--------------|---------------|---------------|--------------|---------|--|--|--|--|--|

| 7             | 6               | 5                                                | 4            | 3             | 2             | 1            | 0       |  |  |  |  |  |

| INTE          | INT             | TS                                               | TE           | PSTE          | PST2          | PST1         | PST0    |  |  |  |  |  |

|               |                 |                                                  |              |               |               |              |         |  |  |  |  |  |

|               |                 |                                                  |              | DTE           |               |              |         |  |  |  |  |  |

|               |                 | The CONT register is both readable and writable. |              |               |               |              |         |  |  |  |  |  |

|               | ■ Bit 6 is      | read only.                                       |              |               |               |              |         |  |  |  |  |  |

| Bit 7 (INTE)  | INT signal edge |                                                  |              |               |               |              |         |  |  |  |  |  |

|               | 0 = inter       | rupt occur                                       | s at the ris | sing edge o   | on the INT    | oin          |         |  |  |  |  |  |

|               | 1 = inter       | rupt occur                                       | s at the fa  | lling edge o  | on the INT    | pin          |         |  |  |  |  |  |

| Bit 6 (INT):  | Interrupt       | enable fla                                       | q            |               |               |              |         |  |  |  |  |  |

| ( <i>,</i>    | -               |                                                  | -            | ware interru  | upt           |              |         |  |  |  |  |  |

|               |                 | -                                                |              | I instructior | •             |              |         |  |  |  |  |  |

|               | This bit i      | s readable                                       | e only.      |               |               |              |         |  |  |  |  |  |

| Bit 5 (TS):   | TCC sig         | nal source                                       | 9            |               |               |              |         |  |  |  |  |  |

|               | 0 = inter       | nal instruc                                      | tion cycle   | clock. P54    | 1 is bi-direc | tional I/O p | oin.    |  |  |  |  |  |

|               | 1 = trans       | sition on th                                     | e TCC pii    | า             |               |              |         |  |  |  |  |  |

| Bit 4 (TE):   | TCC sig         | nal edge                                         |              |               |               |              |         |  |  |  |  |  |

|               | 0 = incre       | ement if the                                     | e transitio  | n from low    | to high take  | es place or  | the TCC |  |  |  |  |  |

|               | pin             |                                                  |              |               |               |              |         |  |  |  |  |  |

|               | 1 = incre       | ement if the                                     | e transitio  | n from high   | to low take   | es place or  | the TCC |  |  |  |  |  |

|               | pin.            |                                                  |              |               |               |              |         |  |  |  |  |  |

| Bit 3 (PSTE   | ): Prescale     | er enable b                                      | oit for TCC  | ;             |               |              |         |  |  |  |  |  |

|               |                 |                                                  |              | CC rate is 1  |               |              |         |  |  |  |  |  |

|               | 1 = pres        | caler enab                                       | ole bit. TC  | C rate is se  | et as Bit 2 · | ~ Bit 0.     |         |  |  |  |  |  |

| Bit 2 ~ Bit 0 | (PST2 ~ I       | PST0): TC                                        | C prescal    | er bits       |               |              |         |  |  |  |  |  |

|               | PST2            | PST1                                             | PST0         | TCC Ra        | te            |              |         |  |  |  |  |  |

|               | 0               | 0                                                | 0            | 1:2           |               |              |         |  |  |  |  |  |

|               | 0               | 0                                                | 1<br>0       | 1:4<br>1:8    |               |              |         |  |  |  |  |  |

|               | 0               | 1                                                | 1            | 1:16          | —             |              |         |  |  |  |  |  |

|               | 1               | 0                                                | 0            | 1:32          |               |              |         |  |  |  |  |  |

|               |                 | 1                                                | 1            | -             |               |              |         |  |  |  |  |  |

(This specification is subject to change without further notice)

0

1

1

1

1

1

1

0

1

1:64

1:128

1:256

#### NOTE

Tcc timeout period [1/Fosc x prescaler x 256(Tcc cnt) x 1(CLK=2)] Tcc timeout period [1/Fosc x prescaler x 256(Tcc cnt) x 2(CLK=4)]

# 6.2.3 IOC50 ~ IOC70 (I/O Port Control Register)

- "1" puts the relative I/O pin into high impedance, while "0" defines the relative I/O pin as output.

- Only the lower 6 bits of **IOC50** can be defined.

- Only the bit1, 2, 6 and, 7 of **IOC60** can be defined.

- Only the lower 1 bits of **IOC70** can be defined, the others bits are not available.

- IOC50, IOC60, and IOC70 registers are all readable and writable

# 6.2.4 IOC80 (TCCA Control Register)

| 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0      |

|---|---|---|---|---|--------|--------|--------|

| _ | - | - | - | - | TCCAEN | TCCATS | TCCATE |

|                 | <b>NOTE</b><br>4 ~ 0 of IOC80 register is both readable and writable.<br>5 of IOC80 register is readable only.                                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7 ~ Bit 5:  | Not used                                                                                                                                                                                                 |

| Bit 4 & Bit 3:  | Not used, fixed to "0".                                                                                                                                                                                  |

| Bit 2 (TCCAEN): | TCCA enable bit                                                                                                                                                                                          |

|                 | 0 = disable TCCA<br>1 = enable TCCA as a counter                                                                                                                                                         |

| Bit 1 (TCCATS): | TCCA signal source<br>0 =: internal instruction cycle clock. P61 is a bi-directional I/O pin.<br>1 = transit through the TCCA pin                                                                        |

| Bit 0 (TCCATE): | <ul> <li>TCCA signal edge</li> <li>0 = increment if transition from low to high takes place on the TCCA pin</li> <li>1 = increment if transition from high to low takes place on the TCCA pin</li> </ul> |

# 6.2.5 IOC90 (TCCB and TCCC Control Register)

| 7      | 6      | 5 | 4 | 3 | 2      | 1 | 0 |

|--------|--------|---|---|---|--------|---|---|

| TCCBHE | TCCBEN | - | - | _ | TCCCEN | - | - |

Bit 7 (TCCBHE): Control bit is used to enable the most significant byte of counter

- 1 = Enable the most significant byte of TCCBH

- TCCB is a 16-bit counter

- 0 = Disable the most significant byte of TCCBH (default value) TCCB is an 8-bit counter

- Bit 6 (TCCBEN): TCCB enable bit

- 0 = disable TCCB

- 1 = enable TCCB as a counter

- Bit 5 & Bit 4: Not used, fixed to "0".

- Bit 3: Not used.

- Bit 2 (TCCCEN): TCCC enable bit

- 0 = disable TCCC

- 1 = enable TCCC as a counter

- Bit 1 & Bit 0: Not used, fixed to "0".

# 6.2.6 IOCA0 (IR and TCCC Scale Control Register)

| 7      | 6      | 5      | 4      | 3   | 2  | 1   | 0      |

|--------|--------|--------|--------|-----|----|-----|--------|

| TCCCSE | TCCCS2 | TCCCS1 | TCCCS0 | IRE | HF | LGP | IROUTE |

Bit 7 (TCCCSE): Scale enable bit for TCCC

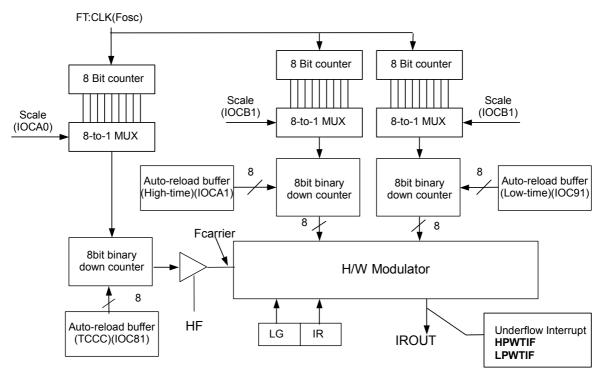

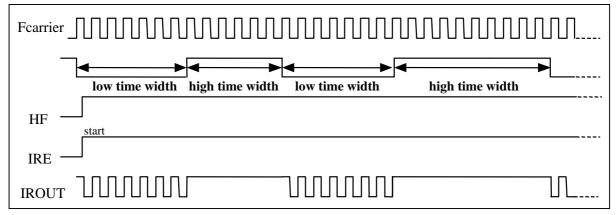

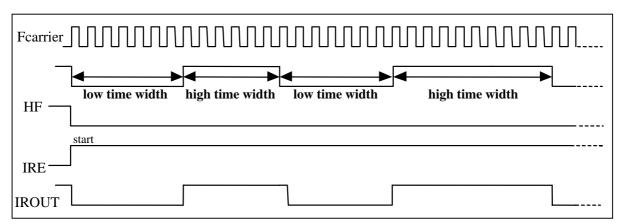

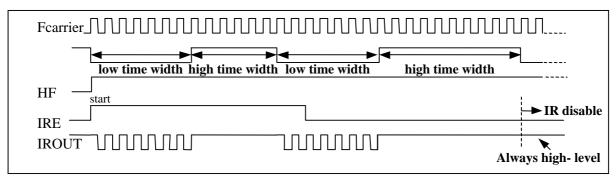

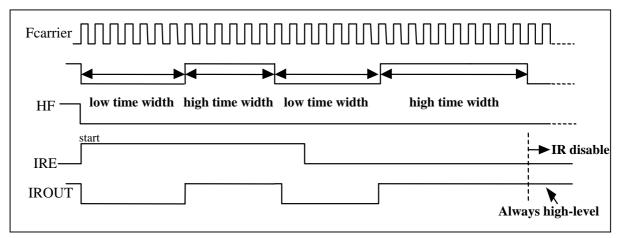

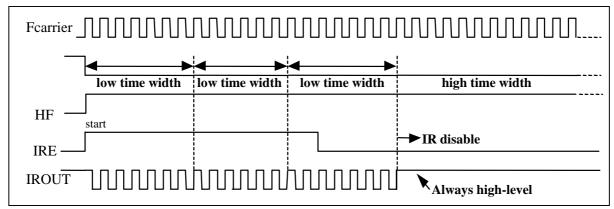

An 8-bit counter is provided as scale for TCCC and IR-Mode. When in IR-Mode, TCCC counter scale uses the low-time segments of the pulse generated by Fcarrier frequency modulation (see Fig. 6-11 in Section 6.8.2, *Function Description*).

- 0 = scale disable bit, TCCC rate is 1:1

- 1 = scale enable bit, TCCC rate is set as Bit 6 ~ Bit 4

# Bit 6 ~ Bit 4 (TCCCS2 ~ TCCCS0): TCCC scale bits

The TCCCS2 ~ TCCCS0 bits of the IOCA0 register are used to determine the scale ratio of TCCC as shown below:

|                 | TCCCS2                                                           | TCCCS1                                                   | TCCCS0                                                                                                 | TCCC Rate                                                                  |

|-----------------|------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|                 | 0                                                                | 0                                                        | 0                                                                                                      | 1:2                                                                        |

|                 | 0                                                                | 0                                                        | 1                                                                                                      | 1:4                                                                        |

|                 | 0                                                                | 1                                                        | 0                                                                                                      | 1:8                                                                        |

|                 | 0                                                                | 1                                                        | 1                                                                                                      | 1:16                                                                       |

|                 | 1                                                                | 0                                                        | 0                                                                                                      | 1:32                                                                       |

|                 | 1                                                                | 0                                                        | 1                                                                                                      | 1:64                                                                       |

|                 | 1                                                                | 1                                                        | 0                                                                                                      | 1:128                                                                      |

|                 | 1                                                                | 1                                                        | 1                                                                                                      | 1:256                                                                      |

|                 | 1 = Enable IRE,<br>defined as IF<br>low-time seg<br>modulation ( | level and the TC<br>i.e., enable H/W<br>ROUT. If HP=1, t | CC is UP Counte<br>Modulator Functi<br>he TCCC counte<br>se generated by F<br>Section 6.8.2, <i>Fu</i> | r.<br>on. Pin 67<br>r scale uses the<br>carrier frequency<br><i>nction</i> |

| Bit 2 (HF):     | determine th<br>1 = IR applicatio<br>generated by                |                                                          | w-pulse width tim<br>and low time wid<br>y-time segments<br>ancy modulation (s                         | er which<br>dth respectively<br>of the pulse                               |

| Bit 1 (LGP):    | Long Pulse.<br>0 = The high-tim<br>1 = The high-tim              | e register and lov<br>e register is igno                 | -                                                                                                      |                                                                            |

| Bit 0 (IROUTE): |                                                                  | as bi-directional                                        | I/O pin<br>er this condition, t                                                                        | he I/O control bit                                                         |

| 7          | 6                 | 5                                                          | 4              | 3            | 2           | 1        | 0     |  |  |  |  |

|------------|-------------------|------------------------------------------------------------|----------------|--------------|-------------|----------|-------|--|--|--|--|

| -          | -                 | /PD55                                                      | /PD54          | /PD53        | /PD52       | /PD51    | /PD50 |  |  |  |  |

| 1          |                   |                                                            |                |              |             |          |       |  |  |  |  |

|            | NOTE              |                                                            |                |              |             |          |       |  |  |  |  |

|            |                   | IOCB0 re                                                   | gister is both | n readable a | nd writable |          |       |  |  |  |  |

| Bit 7&Bite | 6: Not u          | sed, fixed t                                               | o "1".         |              |             |          |       |  |  |  |  |

| Bit 5 (/PD | <b>55):</b> Contr | Control bit is used to enable the pull-down of the P55 pin |                |              |             |          |       |  |  |  |  |

|            | 0 = E             | nable inter                                                | nal pull-dov   | wn           |             |          |       |  |  |  |  |

|            | 1 = D             | isable inter                                               | nal pull-do    | wn           |             |          |       |  |  |  |  |

| Bit 4 (/PD | 54): Contr        | ol bit is use                                              | ed to enabl    | e the pull-d | lown of the | P54 pin  |       |  |  |  |  |

| Bit 3 (/PD | 53): Contr        | ol bit is use                                              | ed to enabl    | e the pull-d | lown of the | P53 pin  |       |  |  |  |  |

| Bit 2 (/PD | 52): Contr        | ol bit is use                                              | ed to enabl    | e the pull-d | lown of the | P52 pin  |       |  |  |  |  |

| Bit 1 (/PD | 51): Contr        | ol bit is use                                              | ed to enabl    | e the pull-d | lown of the | P51 pin  |       |  |  |  |  |

| Bit 0 (/PD | 50): Contr        | ol bit is use                                              | ed to enabl    | e the pull-d | lown of the | P50 pin. |       |  |  |  |  |

# 6.2.7 IOCB0 (Pull-Down Control Register)

# 6.2.8 IOCC0 (Open-Drain Control Register)

| 7     | 6     | 5 | 4 | 3 | 2 | 1     | 0     |

|-------|-------|---|---|---|---|-------|-------|

| /OD67 | /OD66 | - | - | - | - | /OD61 | /OD60 |

| NOTE                                         |  |

|----------------------------------------------|--|

| IOCC0 register is both readable and writable |  |

Bit 7 (/OD67): Control bit is used to enable the open-drain of the P67 pin

0 = Enable open-drain output

1 = Disable open-drain output

Bit 6 (/OD66): Control bit is used to enable the open-drain of the P66 pin

Bit 5~Bit2: Not used, fixed to "1".

Bit 1 (/OD61): Control bit is used to enable the open-drain of the P61 pin

Bit 0 (/OD60): Control bit is used to enable the open-drain of the P60 pin

# 6.2.9 IOCD0 (Pull-high Control Register)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| /PH57 | /PH56 | /PH55 | /PH54 | /PH53 | /PH52 | /PH51 | /PH50 |

|                | <b>NOTE</b><br>IOCD0 register is both readable and writable |

|----------------|-------------------------------------------------------------|

| Bit 7&Bit6:    | Not used, fixed to "1".                                     |

| Bit 5 (/PH55): | Control bit is used to enable the pull-high of the P55 pin. |

|                | 0 = Enable internal pull-high;                              |

|                | 1 = Disable internal pull-high.                             |

| Bit 4 (/PH54): | Control bit is used to enable the pull-high of the P54 pin. |

| Bit 3 (/PH53): | Control bit is used to enable the pull-high of the P53 pin. |

| Bit 2 (/PH52): | Control bit is used to enable the pull-high of the P52 pin. |

| Bit 1 (/PH51): | Control bit is used to enable the pull-high of the P51 pin. |

| Bit 0 (/PH50): | Control bit is used to enable the pull-high of the P50 pin. |

# 6.2.10 IOCE0 (WDT Control & Interrupt Mask Registers 2)

| 7    | 6   | 5    | 4 | 3    | 2    | 1    | 0    |

|------|-----|------|---|------|------|------|------|

| WDTE | EIS | ADIE | - | PSWE | PSW2 | PSW1 | PSW0 |

Bit 7 (WDTE): Control bit is used to enable Watchdog Timer

| 0 = Disable W | /DT |

|---------------|-----|

|---------------|-----|

1 = Enable WDT

WDTE is both readable and writable

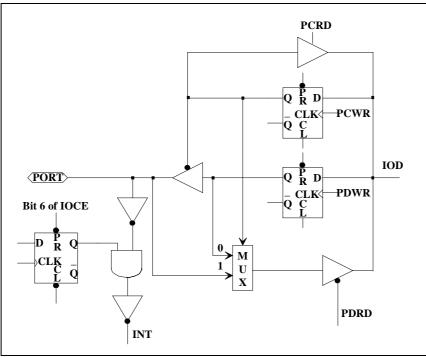

- Bit 6 (EIS): Control bit is used to define the function of the P60 (/INT) pin

- 0 = P60, bi-directional I/O pin

- 1 = /INT, external interrupt pin. In this case, the I/O control bit of P60 (Bit 0 of IOC60) must be set to "1"

#### NOTE

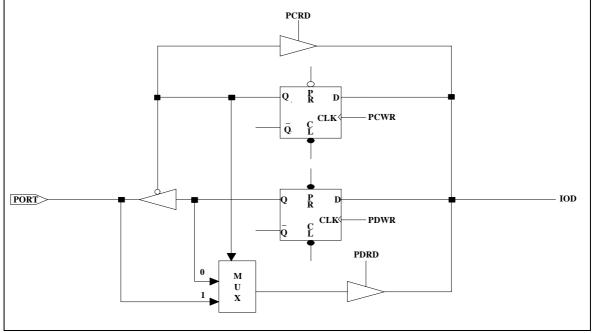

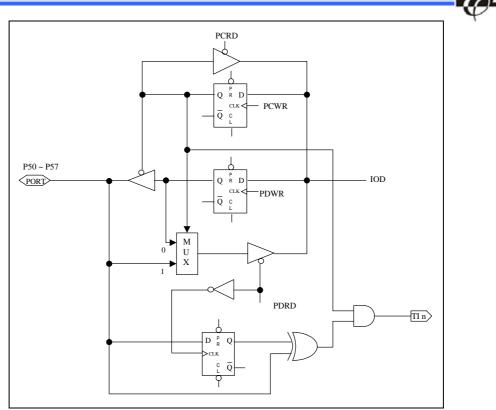

- When EIS is "0," the path of /INT is masked. When EIS is "1," the status of /INT pin can also be read by way of reading Port 6 (R6). Refer to Fig. 6-3 (I/O Port and I/O Control Register Circuit for P60(/INT)) under Section 6.4 (I/O Ports).

- EIS is both readable and writable.

Bit 5 (ADIE): ADIF interrupt enable bit

- 0 = disable ADIF interrupt

- 1 = enable ADIF interrupt

- Bit 4: Not used, fixed to "0".

Bit 3 (PSWE): Prescaler enable bit for WDT

- 0 = prescaler disable bit, WDT rate is 1:1

- 1 = prescaler enable bit, WDT rate is set as Bit2 ~ Bit0

# Bit 2 ~ Bit 0 (PSW2 ~ PSW0): WDT prescaler bits

| PSW2 | PSW1 | PSW0 | WDT Rate |

|------|------|------|----------|

| 0    | 0    | 0    | 1:2      |

| 0    | 0    | 1    | 1:4      |

| 0    | 1    | 0    | 1:8      |

| 0    | 1    | 1    | 1:16     |

| 1    | 0    | 0    | 1:32     |

| 1    | 0    | 1    | 1:64     |

| 1    | 1    | 0    | 1:128    |

| 1    | 1    | 1    | 1:256    |

# 6.2.11 IOCF0 (Interrupt Mask Register)

| 7      | 6      | 5      | 4      | 3      | 2    | 1    | 0    |

|--------|--------|--------|--------|--------|------|------|------|

| LPWTIE | HPWTIE | TCCCIE | TCCBIE | TCCAIE | EXIE | ICIE | TCIE |

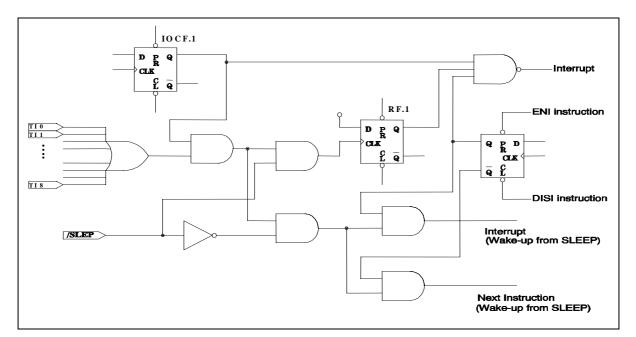

| NOTE <ul> <li>IOCF0 register is both readable and writable</li> <li>Individual interrupt is enabled by setting its associated control bit in the IOCF0 and in IOCE0 Bit 5 to "1".</li> <li>Global interrupt is enabled by the ENI instruction and is disabled by the DISI instruction. Refer to Fig. 6-7 (Interrupt Input Circuit) under Section 6.6 (Interrupt).</li> </ul> |                                                                                            |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Bit 7 (LPWTIE):                                                                                                                                                                                                                                                                                                                                                              | LPWTIF interrupt enable bit<br>0 = Disable LPWTIF interrupt<br>1 = Enable LPWTIF interrupt |  |  |  |  |

| Bit 6 (HPWTIE):                                                                                                                                                                                                                                                                                                                                                              | HPWTIF interrupt enable bit<br>0 = Disable HPWTIF interrupt<br>1 = Enable HPWTIF interrupt |  |  |  |  |

| Bit 5 (TCCCIE):                                                                                                                                                                                                                                                                                                                                                              | TCCCIF interrupt enable bit<br>0 = Disable TCCCIF interrupt<br>1 = Enable TCCCIF interrupt |  |  |  |  |

| Bit 4 (TCCBIE):                                                                                                                                                                                                                                                                                                                                                              | TCCBIF interrupt enable bit<br>0 = Disable TCCBIF interrupt<br>1 = Enable TCCBIF interrupt |  |  |  |  |

| Bit 3 (TCCAIE): | TCCAIF interrupt enable bit<br>0 = Disable TCCAIF interrupt<br>1 = Enable TCCAIF interrupt |

|-----------------|--------------------------------------------------------------------------------------------|

| Bit 2 (EXIE):   | EXIF interrupt enable bit<br>0 = Disable EXIF interrupt<br>1 = Enable EXIF interrupt       |

| Bit 1 (ICIE):   | ICIF interrupt enable bit<br>0 = Disable ICIF interrupt<br>1 = Enable ICIF interrupt       |

| Bit 0 (TCIE):   | TCIF interrupt enable bit.<br>0 = Disable TCIF interrupt<br>1 = Enable TCIF interrupt      |

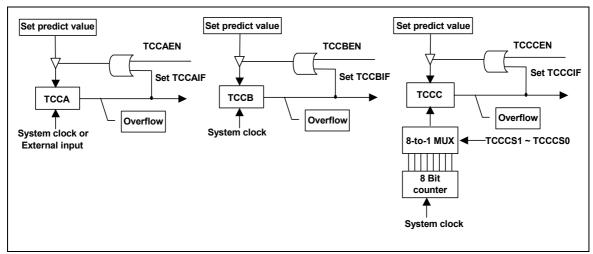

# 6.2.12 IOC51 (TCCA Counter)

**IOC51 (TCCA)** is an 8-bit clock counter. It can be read, written, and cleared on any reset condition and is an UP Counter.

#### NOTE

- TCCA timeout period [1/Fosc x (256-TCCA cnt) x 1(CLK=2)]

- TCCA timeout period [1/Fosc x (256-TCCA cnt) x 2(CLK=4)]

# 6.2.13 IOC61 (TCCB Counter)

An 8-bit clock counter is for the least significant byte of **TCCBX (TCCB)**. It can be read, written, and cleared on any reset condition and is an UP Counter.

# 6.2.14 IOC71 (TCCBH / MSB Counter)

An 8-bit clock counter is for the most significant byte of **TCCBX (TCCBH)**. It can be read, written, and cleared on any reset condition.

When TCCBHE (IOC90) is "0," then TCCBH is disabled. When TCCBHE is"1," then TCCB is a 16-bit length counter.

| NOTE                                                                            |

|---------------------------------------------------------------------------------|

| When TCCBH is Disabled:                                                         |

| ■ TCCB timeout period [1/Fosc x(256 - TCCB cnt)x 1(CLK=2)]                      |

| TCCB timeout period [1/Fosc x ( 256 - TCCB cnt ) x 2(CLK=4)]                    |

| When TCCBH is Enabled:                                                          |

| ■ TCCB timeout period {1/Fosc x [ 65536 - (TCCBH * 256 + TCCB cnt)] x 1(CLK=2)} |

| ■ TCCB timeout period {1/Fosc x [ 65536 - (TCCBH * 256 + TCCB cnt)] x 2(CLK=4)} |

# 6.2.15 IOC81 (TCCC Counter)

**IOC81 (TCCC)** is an 8-bit clock counter that can be extended to 16-bit counter. It can be read, written, and cleared on any reset condition.

If HF (Bit 2 of IOCA0) = 1 and IRE (Bit 3 of IOCA0) = 1, TCCC counter scale uses the low-time segments of the pulse generated by Fcarrier frequency modulation (see Fig. 6-11 in Section 6.8.2, *Function Description*). Then TCCC value will be TCCC predict value.

When HP = 0 or IRE = 0, the TCCC is an UP Counter.

NOTE Under TCCC UP Counter mode: TCCC timeout period [1/Fosc x scaler (IOCA0) x (256-TCCC cnt) x 1(CLK=2)] TCCC timeout period [1/Fosc x scaler (IOCA0) x (256-TCCC cnt) x 2(CLK=4)]

When HP = 1 and IRE = 1, TCCC counter scale uses the low-time segments of the pulse generated by Fcarrier frequency modulation.

| NOTE                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Under IR mode:<br>Fcarrier = FT/2 { [1+decimal TCCC Counter value (IOC81)] * TCCC Scale (IOCA0) }<br>FT is system clock: FT = Fosc/1 (CLK=2)<br>FT = Fosc/2 (CLK=4) |

|                                                                                                                                                                     |

# 6.2.16 IOC91 (Low-Time Register)

The 8-bit Low-time register controls the active or Low segment of the pulse.

The decimal value of its contents determines the number of oscillator cycles and verifies that the IR OUT pin is active. The active period of IR OUT can be calculated as follows:

| NOTE                                                                                 |

|--------------------------------------------------------------------------------------|

| Low time width = { [1+decimal low-time value (IOC91)] * Low time Scale(IOCB1) } / FT |

| ■ FT is system clock: FT = Fosc/1 (CLK=2)                                            |

| FT = Fosc/2 (CLK=4)                                                                  |

When an interrupt is generated by the Low time down counter underflow (when enabled), the next instruction will be fetched from address 015H (Low time).

# 6.2.17 IOCA1 (High Time Register)

The 8-bit High-time register controls the inactive or High period of the pulse.

The decimal value of its contents determines the number of oscillator cycles and verifies that the IR OUT pin is inactive. The inactive period of IR OUT can be calculated as follows:

| NOTE                                                                                   |

|----------------------------------------------------------------------------------------|

| High time width = {[1+decimal high-time value (IOCA1)] * High time Scale(IOCB1) } / FT |

| ■ FT is system clock: FT=Fosc/1(CLK=2)                                                 |

| FT=Fosc/2(CLK=4)                                                                       |

When an interrupt is generated by the High time down counter underflow (when enabled), the next instruction will be fetched from address 012H (High time).

# 6.2.18 IOCB1 High/Low Time Scale Control Register)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| HTSE | HTS2 | HTS1 | HTS0 | LTSE | LTS2 | LTS1 | LTS0 |

Bit 7 (HTSE): High-time scale enable bit.

0 = scale disable bit, High-time rate is 1:1

1 = scale enable bit, High-time rate is set as Bit 6~Bit 4.

## Bit 6 ~ Bit 4 (HTS2 ~ HTS0): High-time scale bits:

| HTS2 | HTS1 | HTS0 | High-Time Rate |

|------|------|------|----------------|

| 0    | 0    | 0    | 1:2            |

| 0    | 0    | 1    | 1:4            |

| 0    | 1    | 0    | 1:8            |

| 0    | 1    | 1    | 1:16           |

| 1    | 0    | 0    | 1:32           |

| 1    | 0    | 1    | 1:64           |

| 1    | 1    | 0    | 1:128          |

| 1    | 1    | 1    | 1:256          |

Bit 3 (LTSE):

Low-time scale enable bit.

0 = scale disable bit, Low-time rate is 1:1

1 = scale enable bit, Low-time rate is set as Bit 2~Bit 0.

Bit 2 ~ Bit 0 (LTS2 ~ LTS0): Low-time scale bits:

| LTS2 | LTS1 | LTS0 | Low-Time Rate |

|------|------|------|---------------|

| 0    | 0    | 0    | 1:2           |

| 0    | 0    | 1    | 1:4           |

| 0    | 1    | 0    | 1:8           |

| 0    | 1    | 1    | 1:16          |

| 1    | 0    | 0    | 1:32          |

| 1    | 0    | 1    | 1:64          |

| 1    | 1    | 0    | 1:128         |

| 1    | 1    | 1    | 1:256         |

(This specification is subject to change without further notice)

# 6.2.19 IOCC1 (TCC Prescaler Counter)

| 0 |   |   |   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | TCC<br>Rate |

|---|---|---|---|-------|-------|-------|-------|-------|-------|-------|-------------|

| 0 | 0 | 0 | - | -     | -     | -     | -     | -     | -     | V     | 1:2         |

| 0 | 0 | 1 | - | -     | -     | _     | -     | -     | V     | V     | 1:4         |

| 0 | 1 | 0 | - | -     | -     | -     | -     | V     | V     | V     | 1:8         |

| 0 | 1 | 1 | - | -     | -     | -     | V     | V     | V     | V     | 1:16        |

| 1 | 0 | 0 | - | -     | -     | V     | V     | V     | V     | V     | 1:32        |

| 1 | 0 | 1 | - | -     | V     | V     | V     | V     | V     | V     | 1:64        |

| 1 | 1 | 0 | - | V     | V     | V     | V     | V     | V     | V     | 1:128       |

| 1 | 1 | 1 | V | V     | V     | V     | V     | V     | V     | V     | 1:256       |

# TCC prescaler counter can be read and written:

V = valid value

The TCC prescaler counter is assigned to TCC (R1).

The contents of the IOCC1 register is cleared when one of the following occurs:

- a value is written to TCC register

- a value is written to TCC prescaler bits (Bit3,2,1,0 of CONT)

- power on reset, /RESET

- WDT time out reset

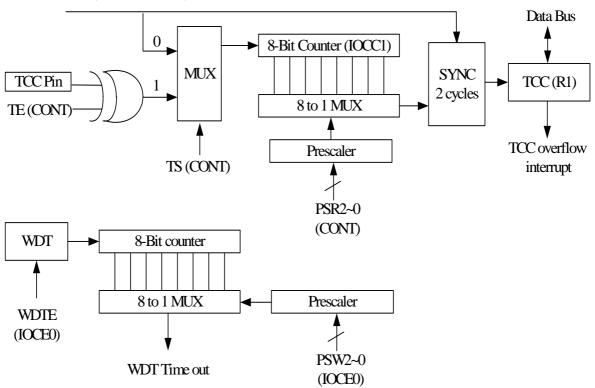

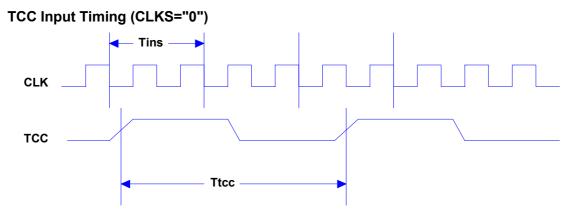

# 6.3 TCC/WDT and Prescaler

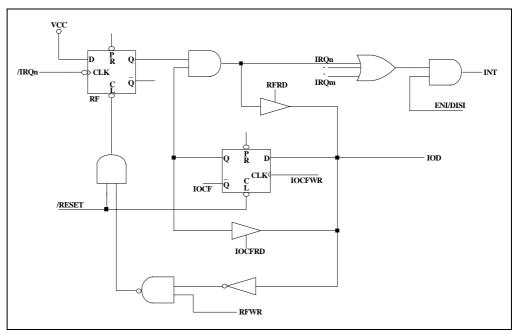

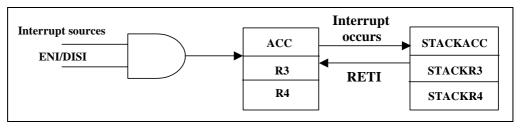

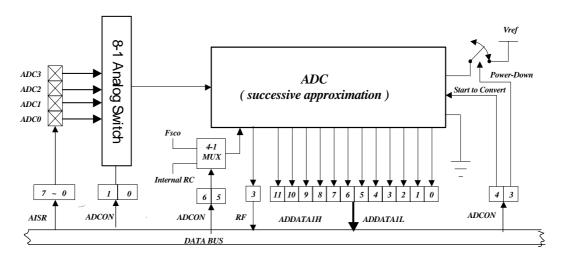

There are two 8-bit counters available as prescalers that can be extended to 16-bit counter for the TCC and WDT respectively. The PST2 ~ PST0 bits of the CONT register are used to determine the ratio of the TCC prescaler, and the PWR2 ~ PWR0 bits of the IOCE0 register are used to determine the prescaler of WDT. The prescaler counter is cleared by the instructions each time such instructions are written into TCC. The WDT and prescaler will be cleared by the "WDTC" and "SLEP" instructions. Fig. 6-1 (next page) depicts the block diagram of TCC/WDT.