# **LXT6282**

# Octal E1 Digital Interface with CRC-4 Monitoring and Jitter/Wander Suppression

#### **Datasheet**

LXT6282 is an eight-channel E1 digital interface. It integrates an E1 dejitter phase locked loop, an E1 retiming function and a CRC-4 monitor function for each E1 transmitter and a CRC-4 monitoring function for each E1 receiver. It is optimized for SDH applications and can used in conjunction with the LXT6251A (21 E1 mapper).

# **Applications**

- SDH 21 or 63 E1 multiplexer

- STM-0 and STM1 SDH add/drop multiplexer

- PDH NxE1 multiplexer

- DCS

- Microwave radio

- Satellite

- Test equipment

- Protection Switch

## **Product Features**

- Octal E1 transceiver digital interface

- Performs the jitter attenuation function on a gapped clock supplied by a PDH or SDH multiplexer

- Performs CRC4 performance monitoring on both transmit and receive sides

- Provides a retiming function on the transmit side for SDH applications (demapped E1 tributaries)

- Built-in HDB3 encoder/decoder

- Compatible with LXT6251A for STM-0/1 applications

- Compatible with LXT334 and the next generation octal LIU

- Microprocessor programmable

- Low power, 3.3 Volt operation, 5 V tolerant I/O

- IEEE 1149.1 (JTAG) compliant

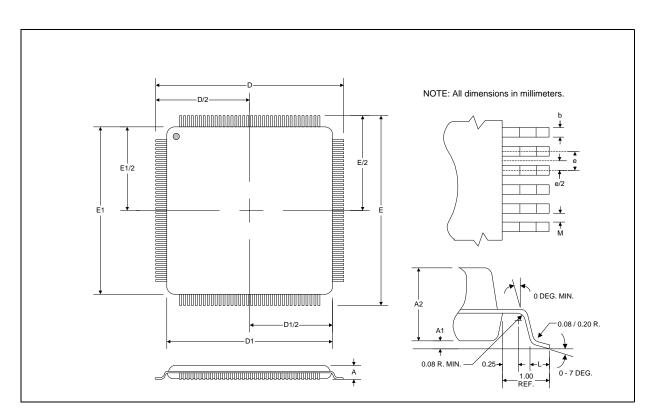

- LQFP 144 surface mount packaging

- Compatible with ITU G.703, G.704, G.706, G.707, G.775 (Draft 1996), G.783 and G.742

- Industrial temperature operating range 40°C to +85°C.

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT6282 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Pin A | Assignn  | nents and Signal Descriptions                                  | 10 |

|-----|-------|----------|----------------------------------------------------------------|----|

| 2.0 | Gene  | eral Fur | nctional Description                                           | 15 |

|     | 2.1   |          | ction                                                          |    |

|     | 2.2   |          | nitter Description                                             |    |

|     |       | 2.2.1    | Dejitter Mode                                                  |    |

|     |       | 2.2.2    | Retiming Mode                                                  |    |

|     |       | 2.2.3    | Pass-Through Mode                                              |    |

|     | 2.3   |          | e Data Flow Description                                        |    |

| 3.0 | Fund  | tional I | Description Per E1 Channel                                     | 18 |

|     | 3.1   | Transn   | ritter Default Operation                                       | 18 |

|     |       | 3.1.1    | Data Input Interface                                           |    |

|     |       | 3.1.2    | Frame Alignment                                                |    |

|     |       | 3.1.3    | CRC-4 Multiframe Alignment                                     |    |

|     |       | 3.1.4    | AIS Detection                                                  |    |

|     |       | 3.1.5    | CRC-4 Multiframe Monitoring                                    |    |

|     |       | 00       | 3.1.5.1 CRC-4 Block Errors Calculation                         |    |

|     |       |          | 3.1.5.2 Remote End Block Errors                                |    |

|     |       |          | 3.1.5.3 Remote Alarm                                           |    |

|     |       | 3.1.6    | Retiming Elastic Store Operation                               | 20 |

|     |       | 3.1.7    | De-jittering Circuitry                                         | 23 |

|     |       | 3.1.8    | AIS Signal Insertion                                           |    |

|     |       | 3.1.9    | Line Coding HDB3                                               | 23 |

|     |       | 3.1.10   |                                                                |    |

|     |       |          | 3.1.10.1Line decoding HDB3                                     |    |

|     |       |          | 3.1.10.2AIS Detection                                          |    |

|     |       |          | 3.1.10.3AIS Insert/LOS Alarm filtering                         |    |

|     |       |          | 3.1.10.4Frame Alignment/Out Of Frame Alarm                     | 25 |

|     |       |          | 3.1.10.5CRC-4 Multiframe Alignment/Out of CRC Multiframe Alarm |    |

|     |       |          | 3.1.10.6CRC-4 Multiframe Monitoring                            |    |

|     |       |          | 3.1.10.7Test Pattern Generator for Autotesting/Maintenance     |    |

|     |       | 3.1.11   | MICROCONTROLLER INTERFACE                                      | _  |

|     |       |          | 3.1.11.1Intel Interface                                        |    |

|     |       |          | 3.1.11.2Motorola Interface                                     |    |

|     |       | 3.1.12   | linterrupt Handling                                            |    |

|     |       |          | 3.1.12.1Interrupt Sources                                      | 27 |

|     |       |          | 3.1.12.2Interrupt Enables                                      |    |

|     |       |          | 3.1.12.3Interrupt Clearing                                     |    |

|     |       |          | 3.1.12.4Status Registers Access                                |    |

| 4.0 | Micro | oproces  | ssor Register Description                                      |    |

| -   | 4.1   | -        | Registers                                                      |    |

|     | 7.1   | 4.1.1    | GLOB_CONF0 - Global Operational Configuration 0 (0FH)          |    |

|     |       | 4.1.1    | GLOB_CONF1- Global Operational Configuration 1 (1FH)           |    |

|     |       | 4.1.3    | IND_XMTE1_CHN - Individual Transmit E1 Channel Interrupt (2FH) |    |

|     |       | 4.1.3    | IND_RCVF1_CHN - Individual Preceive F1 Channel Interrunt (3FH) |    |

|     |       | 4.1.5   | CHIP_ID_NMB - Chip ID Number (4FH)                                                |                   |

|-----|-------|---------|-----------------------------------------------------------------------------------|-------------------|

|     |       | 4.1.6   | BUFF_ALLCNT - Buffer All Counters (5FH)                                           |                   |

|     |       | 4.1.7   | E1_RCV_AISTAT - E1 Receivers AIS Status (8FH)                                     |                   |

|     |       | 4.1.8   | EI_XMT_AISTAT - E1 Transmitters AIS Status (9FH)                                  |                   |

|     |       | 4.1.9   | GLOB_CONF - Global Operational Configuration 3 (AFH)                              |                   |

|     | 4.2   |         | nit Side Registers                                                                |                   |

|     |       | 4.2.1   | XMT_CONF - Transmitter Configuration (iEH)                                        |                   |

|     |       | 4.2.2   | XMT_ALRM_INTO - Transmitter Alarm Interrupt 0 (i1H)                               | 36                |

|     |       | 4.2.3   | XMT_ALRM_INT1 - Transmitter Alarm Interrupt 1(i2H)                                |                   |

|     |       | 4.2.4   | XMT_ALM_STAT - Transmitter Alarm Status (i3H)                                     |                   |

|     |       | 4.2.5   | XMT_ALM_INTE0 - Transmitter Alarm Interrupt Enable 0 (i4H)                        |                   |

|     |       | 4.2.6   | XMT_ALM_INTE1 - Transmitter Alarm Interrupt Enable 1 (i5H)                        | 38                |

|     |       | 4.2.7   | XMT_FRMWD_ERC - Transmitter FrameWord Error Counter (i7- i6h                      | <del>1</del> ) 38 |

|     |       | 4.2.8   | XMT_BLCK_ERC - Transmitter CRC-4 Block Errors Counter (i9H - i8H)                 | 39                |

|     |       | 4.2.9   | XMT_RMT_ERC - Transmitter Remote CRC-4 Block Errors Counter (iB - iAH)            |                   |

|     |       | 4.2.10  | XMT_RÉTMBUF - Transmitter Retiming Buffer Positive & Negative Slip Counters (iCH) |                   |

|     |       | 4.2.11  | XMT_RTMBUF_STAT - Transmitter Retiming Buffer Status (iDH)                        | 40                |

|     | 4.3   |         | e Side Registers                                                                  |                   |

|     |       | 4.3.1   | RCV_CONF- Receiver Configuration (jEH)                                            | 41                |

|     |       | 4.3.2   | RCV_ALRM_INT0 - Receiver Alarm Interrupt 0 (j1H)                                  |                   |

|     |       | 4.3.3   | RCV_ALRM_INT1 - Receiver Alarm Interrupt 1 (j2H)                                  |                   |

|     |       | 4.3.4   | REC_ALRMS - Receiver Alarm Status (j3H)                                           |                   |

|     |       | 4.3.5   | RCE_ALM_INTE0 - Receiver Alarm Interrupt Enable Register 0 (j4H                   |                   |

|     |       | 4.3.6   | RCV_ALM_INTE1 - Receiver Alarm Interrupt Enable Register 1 (j5H                   |                   |

|     |       | 4.3.7   | RCV_FRMWD_ERC - Receiver FrameWord Error Counter (j7 - j6H)                       |                   |

|     |       | 4.3.8   | RCV_BLCK_ERC - Receiver CRC-4 Block Error Counter (j9 - j8H)                      |                   |

|     |       | 4.3.9   | RCV_RMT_BLCK_ERC - Receiver Remote CRC-4 Block Error Cour (jB - jAH)              | nter              |

|     |       | 4.3.10  | RCV_CD_ERC - Receiver Code Errors Counter (jDH)                                   |                   |

| 5.0 | Test  |         | cations                                                                           |                   |

| 6.0 | Testa | ability |                                                                                   | 52                |

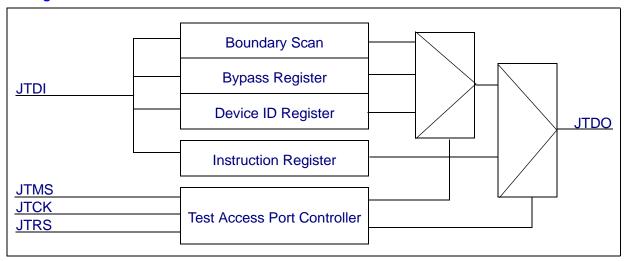

|     | 6.1   | IEEE 1  | 149.1 Boundary Scan Description                                                   | 52                |

|     |       | 6.1.1   | Instruction Register and Definitions                                              |                   |

|     |       |         | 6.1.1.1 EXTEST ('b00)                                                             | 53                |

|     |       |         | 6.1.1.2 SAMPLE/PRELOAD ('b01)                                                     | 53                |

|     |       |         | 6.1.1.3 BYPASS ('b11)                                                             |                   |

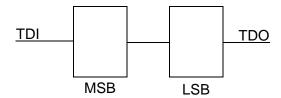

|     |       |         | 6.1.1.4 IDCODE ('b10)                                                             |                   |

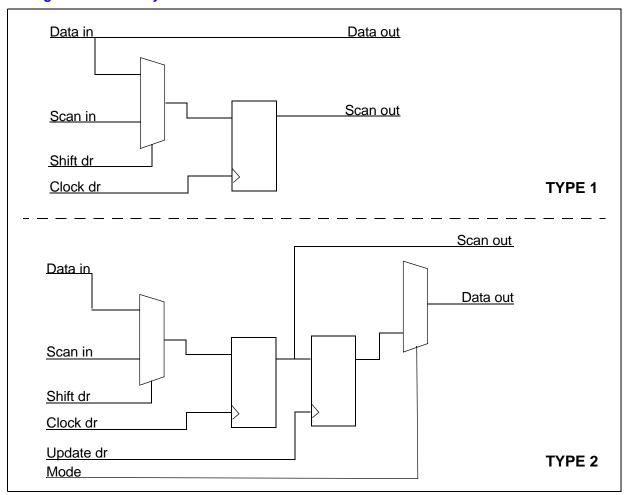

|     |       | 6.1.2   | Boundary Scan Register                                                            | 54                |

| 7.0 | Glos  | sary    |                                                                                   | 59                |

| 3.0 | Pack  | age Inf | ormation                                                                          | 60                |

|     |       | _       |                                                                                   |                   |

# Figures

**Tables**

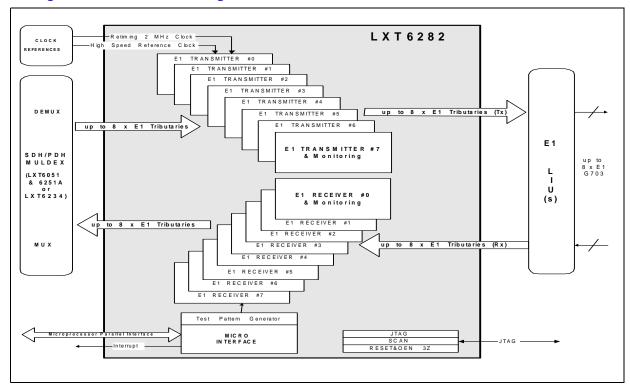

| 1                                                | LXT6282 Block Diagram                                                                                                                                                                                                          | 7                                      |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

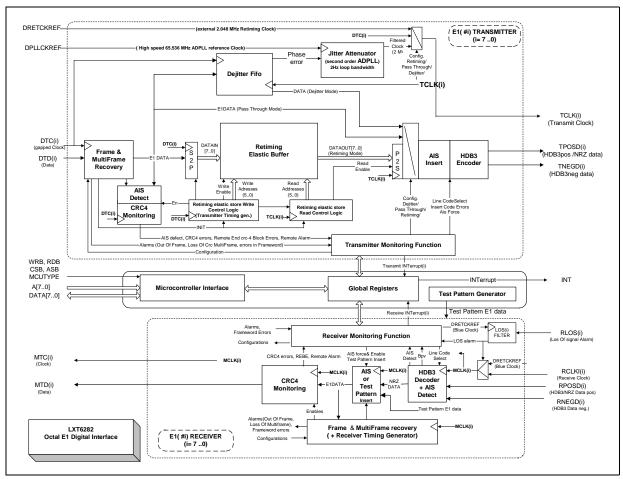

| 2                                                | LXT6282 Block Diagram                                                                                                                                                                                                          | 8                                      |

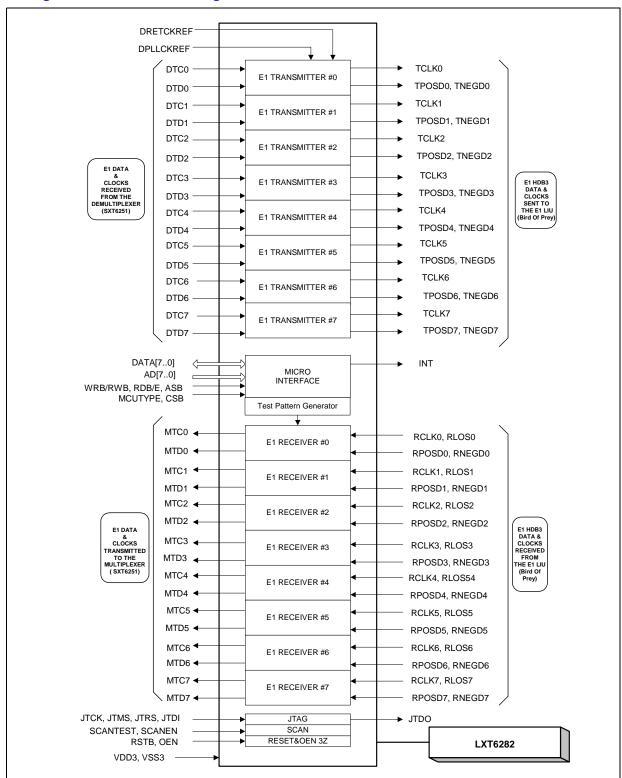

| 3                                                | LXT6282 Block Diagram 2                                                                                                                                                                                                        | 9                                      |

| 4                                                | LXT6282 Pin Assignment                                                                                                                                                                                                         | 10                                     |

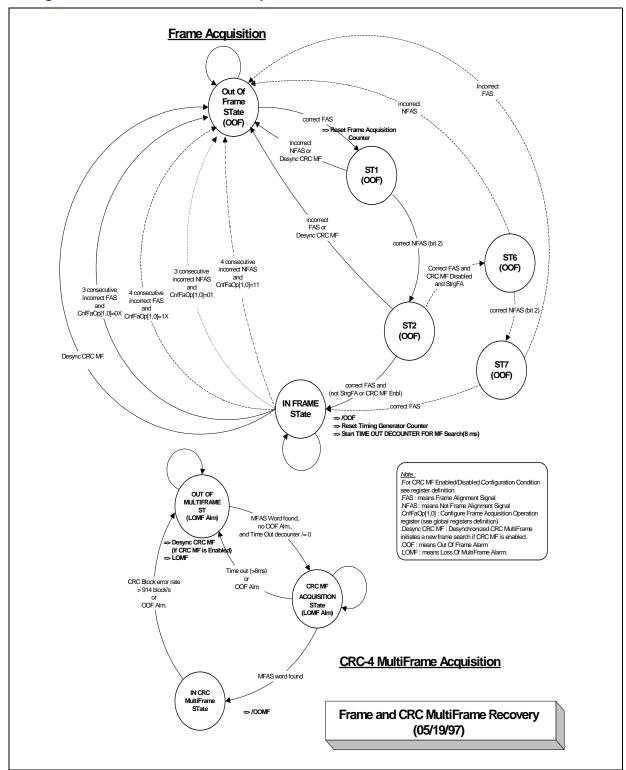

| 5                                                | Frame and Multiframe Acquisition                                                                                                                                                                                               | 22                                     |

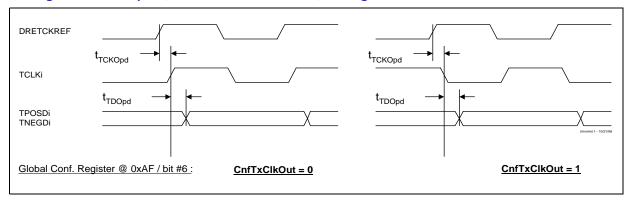

| 6                                                | E1 outputs, transmitted to the LIUs, Timing                                                                                                                                                                                    |                                        |

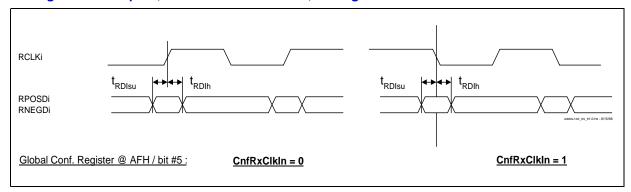

| 7                                                | E1 inputs, received from the LIUs, Timing                                                                                                                                                                                      | 47                                     |

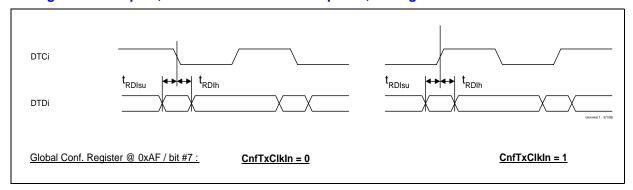

| 8                                                | E1 inputs, received from the demultiplexer, Timing                                                                                                                                                                             | 48                                     |

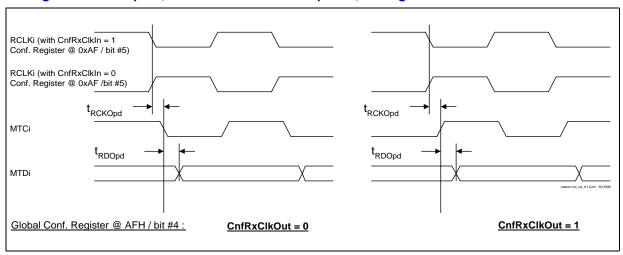

| 9                                                | E1 outputs, transmitted to the multiplexer, Timing                                                                                                                                                                             | 48                                     |

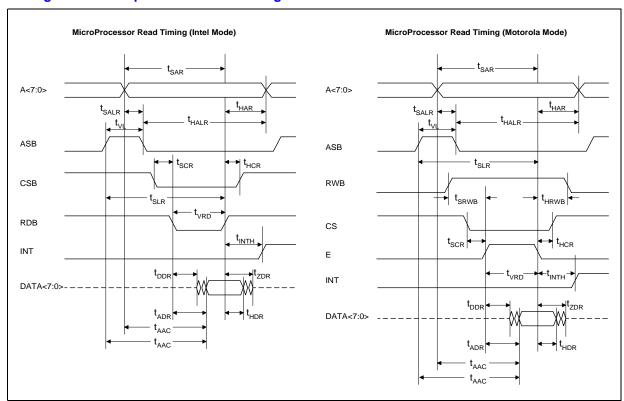

| 10                                               | Microprocessor Read Timing                                                                                                                                                                                                     |                                        |

| 11                                               | Microprocessor Write Timing                                                                                                                                                                                                    | 50                                     |

| 12                                               | Test Access Port                                                                                                                                                                                                               | 52                                     |

| 13                                               | Boundary Scan Cell                                                                                                                                                                                                             | 55                                     |

|                                                  |                                                                                                                                                                                                                                |                                        |

| 1                                                | Signal Descriptions                                                                                                                                                                                                            | 11                                     |

| 1 2                                              | Signal Descriptions                                                                                                                                                                                                            |                                        |

| -                                                | Multiframe TimeSlot 0 Signaling Description                                                                                                                                                                                    | 19                                     |

| 2                                                | Multiframe TimeSlot 0 Signaling Description  Transmitter clock output scheme                                                                                                                                                   | 19<br>24                               |

| 2                                                | Multiframe TimeSlot 0 Signaling Description<br>Transmitter clock output scheme                                                                                                                                                 | 19<br>24<br>46                         |

| 2<br>3<br>4                                      | Multiframe TimeSlot 0 Signaling Description  Transmitter clock output scheme                                                                                                                                                   | 19<br>46<br>46                         |

| 2<br>3<br>4<br>5                                 | Multiframe TimeSlot 0 Signaling Description<br>Transmitter clock output scheme                                                                                                                                                 | 19<br>46<br>46                         |

| 2<br>3<br>4<br>5<br>6                            | Multiframe TimeSlot 0 Signaling Description                                                                                                                                                                                    | 19<br>46<br>46<br>46                   |

| 2<br>3<br>4<br>5<br>6<br>7                       | Multiframe TimeSlot 0 Signaling Description  Transmitter clock output scheme  Absolute Maximum Ratings  Operating Conditions  5 V Tolerant Digital I/O Characteristics  E1 outputs, transmitted to the LIUs, Timing Parameters | 19<br>46<br>46<br>46<br>47             |

| 2<br>3<br>4<br>5<br>6<br>7<br>8                  | Multiframe TimeSlot 0 Signaling Description  Transmitter clock output scheme                                                                                                                                                   | 19<br>46<br>46<br>47<br>47             |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9             | Multiframe TimeSlot 0 Signaling Description                                                                                                                                                                                    | 19<br>24<br>46<br>46<br>47<br>47<br>48 |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10       | Multiframe TimeSlot 0 Signaling Description  Transmitter clock output scheme                                                                                                                                                   |                                        |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | Multiframe TimeSlot 0 Signaling Description  Transmitter clock output scheme                                                                                                                                                   |                                        |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10       | Multiframe TimeSlot 0 Signaling Description  Transmitter clock output scheme                                                                                                                                                   |                                        |

# **Revision History**

| Revision | Date | Description |

|----------|------|-------------|

|          |      |             |

|          |      |             |

|          |      |             |

Figure 1. LXT6282 Block Diagram

Figure 2. LXT6282 Block Diagram

Figure 3. LXT6282 Block Diagram 2

Part #

Rev#

Lot#

FPO#

Identifies the batch.

Identifies the Finish Process Order.

# 1.0 Pin Assignments and Signal Descriptions

VCC\_IO DTD0 MTD0 MTD0 MTD0 MTD0 MTD0 DTD1 MTD1 DTD1 DTD1 DTD1 DTD2 DTD2 MTD2 DTD2 MTD3 DTD3 MTD3 DTD3 MTD3 DTD4 MTD6 DTD4 MTD6 DTD4 MTD6 DTD6 MTD7 DTD7 VCC\_3 UDD7 VCC\_3 UDD7 VCC\_3 UDD7 GND\_3 DATA7 108 VCC\_IO 2 DATA6 107 NC DATA5 3 106 OEN DATA4 105 **JTCK** GND\_IO 5 104 VCC\_IO 6 103 **JTMS JTRS** DATA3 102 101 JTDI DATA2 JTD0 9 100 DATA1 DRETCKREF 10 DATAG 99 SCANTEST 11 98 GND\_3 int<sub>el®</sub> SCANEN VCC\_3 12 97 VCC\_3 13 Α7 GND\_3 14 Α6 MCUTYPE 15 Α5 DPLLCKREF 16 Α4 Revision# VCC 3 17 АЗ 18 RLOS7 A2 -LXT6282LE RNFGD7 Α1 Part# -20 RPOSD7 89 A0 RCLK7 88 -XXXXXXXXXXXXXX CSB LOT# -TNEGD7 22 ASB 87 TPOSD7 23 XXXXXXXX 86 FPO# WRB/RWB TCLK7 24 85 RDB/E RLOS6 25 RSTB 84 RNEGD6 26 INT 83 RPOSD6 27 VCC\_3 82 RCLK6 GND\_3 28 81 TNEGD6 RLOS0 29 80 RNEGD0 30 TPOSD6 31 78 TCLK6 RPOSD0 RLOS4 77 RCLK0 33 RNEGD4 76 TNEGD0 RPOSD4 TPOSD0 34 75 RCLK4 35 74 TCLK0 VCC\_IO GND IO **Package Topside Markings** Marking

Figure 4. LXT6282 Pin Assignment

10 Datasheet

LXT6282 is the unique identifier for this product family. LE indicates the family member.

Identifies the particular silicon "stepping" — refer to the specification update for additional stepping information.

**Table 1. Signal Descriptions**

| Pin Name  | Pin                                                  | PROP    | I/O      | Description                                                                                                                                                                                                                                                                                                                                                       |

|-----------|------------------------------------------------------|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1                                                    | E1 Tr   | ansmit   | ters (receive side of demultiplexer)                                                                                                                                                                                                                                                                                                                              |

|           |                                                      | E       | 1 data   | and clocks transmitted to the LIU                                                                                                                                                                                                                                                                                                                                 |

| TPOSD<70> | 86<br>79<br>62<br>69<br>50<br>59<br>43<br>34         | HiZ-4ma | 0        | Positive HDB3 or NRZ Data Transmit outputs. Eight E1 data channel outputs (channel <i>&gt;, i=&lt;70&gt;) at 2.048 Mbit/s, in either NRZ or HDB3 format.</i>                                                                                                                                                                                                      |

| TNEGD<70> | 87<br>80<br>63<br>70<br>49<br>58<br>42<br>33         | HiZ-4ma | 0        | Negative HDB3 Data Transmit outputs. Eight E1 data channel outputs (channel <i>, i=&lt;70&gt;) at 2.048 Mbit/s when HDB3 coding is used.</i>                                                                                                                                                                                                                      |

| TCLK<70>  | 85<br>78<br>61<br>68<br>51<br>60<br>44<br>35         | HiZ-8ma | 0        | <b>Transmit clock outputs.</b> The 2.048 MHz clock output of each of the eight independent transmitters (TCLK <i>, i=&lt;70&gt;) is to be used with the corresponding E1 data (TPOSD<i> and TNEGD<i>) signals when needed.</i></i></i>                                                                                                                            |

|           | 1                                                    | E1 da   | ta and o | clocks received from the demultiplexer                                                                                                                                                                                                                                                                                                                            |

| DTD<70>   | 111<br>116<br>119<br>124<br>129<br>134<br>137        | BUF-in  | I        | <b>Demultiplexed NRZ data inputs.</b> Eight E1 data channel inputs (transmitters, channel <i>&gt;, i=&lt;70&gt;) at 2.048 Mbit/s received from the demultiplexer.</i>                                                                                                                                                                                             |

| DTC<70>   | 110<br>117<br>118<br>125<br>128<br>135<br>136<br>143 | BUF-in  | I        | <b>Demultiplexed Clock inputs.</b> Eight E1 clock inputs (transmitters; channel <i>&gt;, i=&lt;70&gt;) at 2.048 MHz received from the demultiplexer. These clocks can be gapped due to the SDH frame structure and the justification process.</i>                                                                                                                 |

|           | •                                                    | •       | E        | cternal Clock References                                                                                                                                                                                                                                                                                                                                          |

| DRETCKREF | 99                                                   | BUF-in  | I        | Demultiplexer Re-timing Clock. This is an external 2.048 MHz reference clock input that can be used in each E1 transmitter to retime the E1 data received from the demultiplexer (wander reduction if the E1 transmitter # i is configured in retiming mode). This clock is also used as a blue clock in each receiver to generate an AIS signal in case of RLOS. |

<sup>1.</sup> Buf-in = CMOS Input buffer with switching threshold at 3.3V / 2 (V  $_{DD}$  / 2) 2. i = <7...0> which corresponds to the E1 channel number

**Table 1. Signal Descriptions**

| Pin Name  | Pin                                                  | PROP    | I/O     | Description                                                                                                                                                                                                                                                            |

|-----------|------------------------------------------------------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPLLCKREF | 93                                                   | BUF-in  | 1       | High speed PLL clock reference. This is an external 65.536 MHz (+ /-50 ppm) reference clock that can be used in each E1 transmitter as the Digital Phase Locked Loop Clock input reference. Only needed if an E1 transmitter is configured in jitter attenuation mode. |

|           |                                                      | E1      | Receiv  | ers (Transmit side of multiplexer)                                                                                                                                                                                                                                     |

|           |                                                      | E       | 1 Data  | and Clocks received from the LIU                                                                                                                                                                                                                                       |

| RPOSD<70> | 89<br>82<br>65<br>75<br>47<br>56<br>40<br>31         | BUF-in  | ı       | Positive HDB3 or NRZ Data Receive. Eight E1 data channel inputs (channel <i>&gt;, i=&lt;70&gt;) at 2.048 Mbit/s supplied by the E1 line interface unit(s), in either NRZ or HDB3 format.</i>                                                                           |

| RNEGD<70> | 90<br>83<br>66<br>76<br>46<br>55<br>39<br>30         | BUF-in  | I       | Positive HDB3 Data Receive. Eight E1 data channel inputs (channel <i>, i=&lt;70&gt;) at 2.048 Mbit/s supplied by the E1 line interface unit(s), when HDB3 coding is used. If HDB3 coding is not used, these inputs have to be grounded.</i>                            |

| RLOS<70>  | 91<br>84<br>67<br>77<br>45<br>54<br>38<br>29         | BUF-in  | I       | Loss of Signal from the external line interface unit(s). Eight input alarms from the E1 line interface circuits (channel <i>, i=&lt;70&gt;). RLOS alarm is active high.</i>                                                                                            |

| RCLK<70>  | 88<br>81<br>64<br>74<br>48<br>57<br>41<br>32         | BUF-in  | I       | Receive clock inputs. Eight receive E1 clocks at 2.048 MHz provided by the E1 line interface unit(s).                                                                                                                                                                  |

|           |                                                      | E1 D    | ata and | Clocks transmitted to the Multiplexer                                                                                                                                                                                                                                  |

| MTD<70>   | 112<br>115<br>120<br>123<br>130<br>133<br>138<br>141 | HiZ-4ma | 0       | NRZ Data outputs. Eight E1 data channel outputs of the receivers (channel <i>, i=&lt;70&gt;) at 2.048 Mbit/s transmitted to the multiplexer.</i>                                                                                                                       |

<sup>1.</sup> Buf-in = CMOS Input buffer with switching threshold at 3.3V / 2 ( $V_{DD}$  / 2) 2. i = <7...0> which corresponds to the E1 channel number

**Table 1. Signal Descriptions**

| Pin Name | Pin                                                  | PROP                         | I/O | Description                                                                                                                                                                                               |

|----------|------------------------------------------------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MTC<70>  | 113<br>114<br>121<br>122<br>131<br>132<br>139<br>140 | HiZ-8ma                      | 0   | Clock outputs. Each one of these eight 2048 MHz clock outputs of the receivers is to be used with the corresponding E1 data (MTD <i>, i=&lt;70&gt;) signal transmitted to the multiplexer, if needed.</i> |

|          |                                                      |                              | •   | Microprocessor Bus                                                                                                                                                                                        |

| A<70>    | 13-20                                                | BUF-in                       | 1   | Address Bus 8 bits. Eight-bit address port for data, command and status addresses.                                                                                                                        |

| DATA<70> | 1-4<br>7-10                                          | BUF-in/<br>Hiz-10ma          | I/O | Data Bus 8 bits. Eight bits I/O to read and write data, commands and status to and from the device.                                                                                                       |

| WRB/RWB  | 23                                                   | BUF-in                       | 1   | Write-Bar Intel; Read/Write Bar Motorola                                                                                                                                                                  |

| RDB/E    | 24                                                   | BUF-in                       | I   | Read-bar Intel; Enable Motorola                                                                                                                                                                           |

| INT      | 26                                                   | Hiz-4ma                      | 0   | Interrupt request. Active low                                                                                                                                                                             |

| CSB      | 21                                                   | BUF-in                       | I   | Chip Select. Active low                                                                                                                                                                                   |

| ASB      | 22                                                   | BUF-in                       | 1   | Address Strobe Enable. Indication that the address on the address bus is valid. Active high.                                                                                                              |

| MCUTYPE  | 94                                                   | BUF-in                       | 1   | Motorola/Intel Interface mode select. A High indicates a Motorola and a Low an Intel Microprocessor.                                                                                                      |

| RSTB     | 25                                                   | BUF-in<br>(60K pull<br>up)   | 1   | Chip Master Reset. A low will reset all registers to default values.                                                                                                                                      |

| OEN      | 105                                                  | BUF-in<br>(60K pull<br>up)   | 1   | Master chip output enable. Active high (a low will set all outputs and bidirectionnal to 3Z)                                                                                                              |

|          | •                                                    | •                            | J.  | TAG and SCAN test ports                                                                                                                                                                                   |

| JTCK     | 104                                                  | BUF-in                       | I   | JTAG Clock. Clock for all boundary scan circuitry.                                                                                                                                                        |

| JTMS     | 103                                                  | BUF-in<br>(60K pull<br>up)   | 1   | JTAG Test Mode Select. Determine state of TAP controller.                                                                                                                                                 |

| JTRS     | 102                                                  | BUF-in<br>(60K pull<br>down) | I   | JTAG Reset. Active low.                                                                                                                                                                                   |

| JTDI     | 101                                                  | BUF-in<br>(60K pull<br>up)   | 1   | JTAG Data Input. Input signal used to shift in instructions and data.                                                                                                                                     |

| JTDO     | 100                                                  | 2mA                          | 0   | JTAG Data Output. Output signal used to shift out instructions and data.                                                                                                                                  |

| SCANTEST | 98                                                   | BUF-in<br>(60K pull<br>up)   | I   | Scan test mode (active low)                                                                                                                                                                               |

| SCANEN   | 97                                                   | BUF-in<br>(60K pull<br>up)   | 1   | Scan enable (active low)                                                                                                                                                                                  |

<sup>1.</sup> Buf-in = CMOS Input buffer with switching threshold at 3.3V / 2 ( $V_{DD}$  / 2) 2. i = <7...0> which corresponds to the E1 channel number

**Table 1. Signal Descriptions**

| Pin                                    | PROP                                                                                                            | I/O                                                                                                             | Description                                                                                                     |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                                        |                                                                                                                 |                                                                                                                 | Power Supply                                                                                                    |

| 12, 27, 52,<br>71, 92, 96,<br>109, 127 |                                                                                                                 |                                                                                                                 | 3.3 V Core supply. (8 pins)                                                                                     |

| 11, 28, 53,<br>95, 108,<br>126         |                                                                                                                 |                                                                                                                 | GND-Core. Ground for 3.3 V supply. (6 pins)                                                                     |

| 6, 37, 73,<br>107, 144                 |                                                                                                                 |                                                                                                                 | 3.3V I/O ring supply. (5 pins)                                                                                  |

| 5, 36, 72                              |                                                                                                                 |                                                                                                                 | GND-I/O Ring. Ground for I/O supply. (3 pins)                                                                   |

| 106                                    |                                                                                                                 |                                                                                                                 | This pin should be left unconnected.                                                                            |

|                                        | 12, 27, 52,<br>71, 92, 96,<br>109, 127<br>11, 28, 53,<br>95, 108,<br>126<br>6, 37, 73,<br>107, 144<br>5, 36, 72 | 12, 27, 52,<br>71, 92, 96,<br>109, 127<br>11, 28, 53,<br>95, 108,<br>126<br>6, 37, 73,<br>107, 144<br>5, 36, 72 | 12, 27, 52,<br>71, 92, 96,<br>109, 127<br>11, 28, 53,<br>95, 108,<br>126<br>6, 37, 73,<br>107, 144<br>5, 36, 72 |

<sup>1.</sup> Buf-in = CMOS Input buffer with switching threshold at 3.3V / 2 ( $V_{DD}$  / 2) 2. i = <7...0> which corresponds to the E1 channel number

# 2.0 General Functional Description

# 2.1 Introduction

The LXT6282 integrates eight E1 transmitters and eight E1 receivers that can operate independently. It performs jitter/wander filtering, CRC-4 monitoring and HDB3 encoding/decoding. It also includes a Motorola/Intel compatible microcontroller interface for alarm and performance monitoring.

The following description follows the simplified block diagram (refer to Figure 2 and Figure 3).

# 2.2 Transmitter Description

The eight fully independent E1 transmitter blocks can be configured for different applications.

Each transmitter input interface accepts an NRZ encoded E1 signal input (DTDx) and clock input (DTCx). The transmission frame structure and the justification process allow the incoming clock (DTCx) to be gapped and jittered. The E1 signal (DTDx) may have a CRC-4 multiframe structure according to recommendation ITU G.704 (refer to Table 2).

The DTDx data is fed to the frame/multiframe recovery block. This block synchronizes the Transmitter Timing Generator to the incoming E1 data frame and provides Out Of Frame (OOF) and Loss Of Multiframe (LOMF) alarm indications. Remote End Block Errors (REBE) are also counted and stored in a set of microprocessor-accessible counters. The Remote alarm is monitored (but not inserted) for status changes.

Once frame synchronization is achieved, any errors in the frame word are detected, counted and stored in a set of microprocessor-accessible counters. A CRC-4 calculation is also performed over the multiframe and compared with the incoming CRC-4 value. Again, any errors are counted and stored in a set of microprocessor-accessible counters.

An AIS defect at the DTDx input is also detected and monitored. All framing, multiframing and CRC-4 monitoring functions can be bypassed if not needed.

The transmitter can be configured to operate in three different modes:

#### 2.2.1 Dejitter Mode

In Dejitter mode, the transmitter filters jitter and eliminates gaps in the incoming E1 clock and data.

The incoming E1 data is fed into a 32-bit FIFO. The write clock of the FIFO is the gapped input clock (DTC), which is also fed to the jitter attenuator consisting of a second order All Digital Phase Locked Loop (ADPLL) having a 2.0 Hz loop bandwidth. The filtered clock output of the ADPLL is the read clock of the FIFO. The transmitter can be configured to insert an AIS signal (data "all one" + blue clock) automatically when the FIFO overflows, underflows or the PLL is unlocked.

The degapped E1 output is emitted as NRZ data on TPOSD, or as HDB3 encoded data on TPOSD and TNEGD. The dejittered and degapped output clock of each transmitter is emitted on TCLK at the same frequency as the DTC input clock (TCLK clock is the ADPLL output). This working mode is fully transparent - no data is lost or added in the transmission.

## 2.2.2 Retiming Mode

In the Retiming mode, the transmitter eliminates wander and jitter in the incoming clock (DTC).

Incoming E1 data is converted to a byte parallel format and fed into a two frame-wide elastic buffer. The write and read control logic of this elastic store are initialized by the E1 frame acquisition process. The data is read out of the elastic buffer using an external clock reference input (DRETCKREF). DRETCKREF may or may not be at the same frequency as the DTC clock input. If the read and write frequencies are different, the elastic store will periodically overflow or underflow. In either case, the read control logic will process a controlled slip of one complete frame in order to re-center the elastic buffer. This will result in the loss or repetition of one complete E1 frame.

The retiming FIFO may also operate on an un-framed 2.048 Mbit/s signal busy setting the transmitter to "Retiming Test Mode." In this case, the read and write control logic of the elastic store is in full free running mode and independent of the framing algorithm. As the data is supposed to be un-framed in this test mode, CRC-4 error monitoring is not valid.

The output from the elastic buffer is converted to a serial format and emitted as NRZ data on TPOSD, or output as HDB3 encoded data on TPOSD and TNEGD, at the TCLK clock rate that is synchronous with the DRETCKREF clock input.

This working mode may be non-transparent. It can handle a maximum of 26 time slots (208 UI) of wander or low frequency jitter before a frame slip occurs. This controlled frame slip assures that the time-slot assignment is not lost at the output of the chip. All the jitter and wander due to the multiplexing/demultiplexing process in the transmission is eliminated.

# 2.2.3 Pass-Through Mode

In the Pass-through mode no dejitter or retiming is performed on the input data.

The input clock (DTC) is shunted to the output clock (TCLK). CRC-4 monitoring and HDB3 encoding can be performed if so configured.

# 2.3 Receive Data Flow Description

The Receiver consists in eight fully independent E1 receiver blocks.

Each receiver input interface includes an NRZ encoded E1 signal input on RPOSDx or HDB3 encoded data on RPOSDx and RNEGDx, a serial clock RCLKx, and a Loss Of Signal (RLOSx) alarm indication coming from the output of an E1 Line Interface Unit Receiver. The E1 input data RPOSD/RNEGD may have a CRC-4 multiframe structure according to recommendation ITU G.704 (refer to Figure 5). HDB3 code errors (Bipolar Violations) are detected and stored in a set of microprocessor-accessible counters.

An AIS defect is detected according to recommendation ITU G.775 for the E1 incoming signal after HDB3 decoding, and the corresponding alarm is accessible to the microprocessor.

If the Loss Of Signal alarm is active, the receiver may insert an AIS signal (all ones in the data), using the DRETCLK clock reference input as a blue clock.

Data is fed to the framing/multiframing block that synchronizes the Receiver Timing Generator to the incoming E1 data frame, and provides Out Of Frame (OOF) and Out Of Multiframe (OOMF) alarm indications. Once the frame synchronization is acquired, frame word errors are detected, counted and stored in a set of microprocessor accessible counters. Remote End Block Errors (REBE) are also counted and stored in a set of microprocessor-accessible counters. The Remote alarm is monitored (but not inserted) for status changes.

A CRC-4 calculation is also performed over the multiframe and compared to the incoming CRC-4 value. Again, any errors are counted and stored in a set of microprocessor- accessible counters.

The E1 signal is emitted as NRZ data on MTD and clock on MTC.

All the AIS, framing, multiframing and CRC-4 monitoring functions can be independently bypassed in each receiver if not needed.

For testing and maintenance purposes, the receiver can be set via the microprocessor as a sequence pattern generator on MTD and MTC data and clock output pins (framed or unframed PRBS sequence).

# 3.0 Functional Description Per E1 Channel

# 3.1 Transmitter Default Operation

## 3.1.1 Data Input Interface

The relative phase between E1 NRZ data (on DTDx pin) and clock (on DTCx pin) inputs can be configured via microprocessor (DTDx data input may be sampled in the transmitter by the rising or falling edge of the input clock DTCx: see global register AFH).

# 3.1.2 Frame Alignment

The framing method follows the rules set forth in CCITT/ITU recommendations G.704 and G.706.

The frame alignment circuit searches for the first frame alignment signal ("0011011" frameword, bit 2-8 in time slot 0) within the incoming E1 data (DTDx). Once detected, the frame acquisition counter is set to check bit 2 in the non-frame alignment signal (time slot 0) of the next frame. If bit 2 is one, a second un-errored frame alignment signal is checked one frame later. Next, the timing generator counters are set and frame synchronization is declared. If bit 2 in the non-frame alignment signal is not one, or the frame alignment signal is not found in the third frame, then a new search is initiated.

If CRC-4 multiframing is configured (see paragraph below and Figure 5), two correct multiframes within 8 ms are used for immunity against false framing.

Once the E1 frame is synchronized, the framer will go out of synchronization after three consecutive frame alignment signals containing single or multiple errors are received. In addition, it is possible to configure the framing algorithm via register 0FH, so that the framer will also go out of synchronization if three consecutive bit 2 of the non- frame alignment signal are not one. A 12-bit microprocessor-accessible counter can be configured (see global register 0FH) to count either the errored FAS, the errored NFAS, or the FAS and the NFAS with single or multiple errors.

If the CRC-4 multiframing is not configured, it is possible to strengthen the frame acquisition algorithm to five consecutive frames (three FAS and two NFAS with no error) by programming global register 0FH. This will minimize the probability of incorrect synchronization. In this case, the frame desynchronization algorithm is also strengthened to four consecutive frame alignment signals received that contain single or multiple errors, or four consecutive bit 2 of the non-frame alignment signal not one (if so configured).

The Out Of Frame (OOF) alarm status is accessible to the microprocessor via the status registers.

## 3.1.3 CRC-4 Multiframe Alignment

CRC-4 multiframe alignment is used for immunity against false framing and also provides non-intrusive error monitoring capabilities for the E1 payload.

When CRC-4 is selected as the E1 framing option the transmitter attempts to synchronize to a 16 frame multiframe structure illustrated in Table 1.

The multiframe consists of 16 basic E1 frames (eight double frames), numbered 0-15, that are further divided into two 8-frame sub-multiframes (SMF I and SMF II). Bit 1 of each frame is used to transport the Cyclic Redundancy Check bits, multiframe sync word and Remote End Block Errors (REBE) in the following manner:

- In the four frames of each SMF that include the FAS word, bit 1 contains the four CRC bits, numbered C1-C4.

- In the eight frames of the entire multiframe that include the NFAS word, bit 1 contains a 6-bit CRC-4 multiframe alignment signal as well as two REBE indication bits.

Table 2. Multiframe TimeSlot 0 Signaling Description

|         | Frame # | 1  | 2 | 3 | 4   | 5   | 6   | 7   | 8   |

|---------|---------|----|---|---|-----|-----|-----|-----|-----|

|         | 0       | C1 | 0 | 0 | 1   | 1   | 0   | 1   | 1   |

|         | 1       | 0  | F | А | Sa4 | Sa5 | Sa6 | Sa7 | Sa8 |

|         | 2       | C2 | 0 | 0 | 1   | 1   | 0   | 1   | 1   |

| SMFI    | 3       | 0  | F | Α | Sa4 | Sa5 | Sa6 | Sa7 | Sa8 |

| JOINT 1 | 4       | C3 | 0 | 0 | 1   | 1   | 0   | 1   | 1   |

|         | 5       | 1  | F | Α | Sa4 | Sa5 | Sa6 | Sa7 | Sa8 |

|         | 6       | C4 | 0 | 0 | 1   | 1   | 0   | 1   | 1   |

|         | 7       | 0  | F | Α | Sa4 | Sa5 | Sa6 | Sa7 | Sa8 |

|          | Frame # | 1   | 2 | 3 | 4   | 5   | 6   | 7   | 8   |

|----------|---------|-----|---|---|-----|-----|-----|-----|-----|

|          | 8       | C1  | 0 | 0 | 1   | 1   | 0   | 1   | 1   |

|          | 9       | 1   | F | Α | Sa4 | Sa5 | Sa6 | Sa7 | Sa8 |

|          | 10      | C2  | 0 | 0 | 1   | 1   | 0   | 1   | 1   |

| SMF II   | 11      | 1   | F | Α | Sa4 | Sa5 | Sa6 | Sa7 | Sa8 |

| SIVII II | 12      | С3  | 0 | 0 | 1   | 1   | 0   | 1   | 1   |

|          | 13      | RE1 | F | Α | Sa4 | Sa5 | Sa6 | Sa7 | Sa8 |

|          | 14      | C4  | 0 | 0 | 1   | 1   | 0   | 1   | 1   |

|          | 15      | RE2 | F | А | Sa4 | Sa5 | Sa6 | Sa7 | Sa8 |

#### NOTES:

RE: Remote End CRC-4 Block Error indicator bits (REBE)

Sa4-Sa8: Spare bits for national use

C1-C4: CRC-4 Bits

A: Remote Alarm Indication

F: NFAS Framing Bit (normally = 1 to avoid spurious frame sync)

After FAS/NFAS frame synchronization is acquired, the CRC-4 multiframe alignment is declared when two correct CRC-4 MultiFrame Alignment signals are detected within 8 ms (one complete multiframe lasts two ms). If CRC-4 multiframe alignment is not achieved within 8 ms after frame alignment, a new search will be initiated for valid FAS/NFAS.

Once the CRC-4 Multiframe is acquired, a Loss Of CRC-4 Multiframe (LOMF) is declared when the frame synchronization is lost, or the CRC-4 error rate is greater or equal to 915 block/s. The Loss Of CRC-4 Multiframe alarm is accessible to the microprocessor via the status registers.

#### 3.1.4 AIS Detection

An AIS defect is detected in the DTDx input data when the incoming signal has two or less ZEROs in each of two consecutive double frame periods (512 bits). This defect alarm is cleared when each of two consecutive double frame periods contain three or more ZEROs or when the frame alignment signal has been found.

The AIS defect alarm status is accessible to the microprocessor via the status registers.

# 3.1.5 CRC-4 Multiframe Monitoring

#### 3.1.5.1 CRC-4 Block Errors Calculation

When the CRC-4 multiframe is synchronized, the CRC-4 bits are calculated internally based on a sub-multiframe (as specified in recommendation ITU G704) and compared to the incoming CRC-4 value in the next sub-multiframe. The block errors are stored in a 10-bit counter that can be read by the microprocessor. A maskable interrupt is provided for counter overflows.

#### 3.1.5.2 Remote End Block Errors

Two bits per multiframe (RE1 and RE2) are allocated for the CRC-4 Remote End Block Errors (REBE) indication. These errors are counted and stored in a 10 bit counter that can be read by the microprocessor. A maskable interrupt is provided for counter overflows.

#### 3.1.5.3 Remote Alarm

The Remote alarm bit (bit 3 in the NFAS) is used to tell the transmit end that the receive end has detected a loss of signal or loss of frame. The remote alarm is filtered for three consecutive frames before being declared a new value. Changes in its status is indicated to the microprocessor via a maskable interrupt.

### 3.1.6 Retiming Elastic Store Operation

This block is used to eliminate the wander and the jitter in the incoming clock and data (DTC and DTD). It may be non-transparent for the incoming data (see frame slips, below), but it keeps the time slot alignment in the E1 frame.

The incoming data is converted to a byte parallel format and clocked into a 2 frame wide elastic buffer. The write and read control logic of this elastic store are initialized by the frame synchronization process. Once the frame is acquired, the Elastic Store is centered and the data is read out of the elastic buffer and re-converted to a serial format using an external system clock reference input (DRETCKREF).

If the incoming clock DTC and the system clock DRETCKREF are synchronous and phase-locked (i.e., in the case of a synchronous network), the elastic buffer will never overflow or underflow.

If these two clocks, (DRETCKREF and DTC) do not have the same frequency, the elastic store will overflow or underflow repetitively, depending on the frequency offset.

If the read system clock (DRETCKREF) frequency is higher than the write incoming clock (DTC) frequency, then when the FIFO is close to underflowing, the read control logic will perform a slip of one complete frame. This results in the repetition of the last received frame ("positive slip").

If the read system clock (DRETCKREF) frequency is lower than the write incoming clock (DTCx) frequency, then when the FIFO is close to overflow, the read control logic will perform a slip of one complete frame. This results in the loss of the last received frame ("negative slip").

Positive and negative slips in the elastic store are indicated via two maskable interrupts, and counted in two different 4-bit counters accessible via the microprocessor. A maskable interrupt is provided to indicate counter overflows.

For FIFO and Wander monitoring, or delay calculation, the relative difference between FIFO write and read pointers is indicated in register iCH (6 bits used), accessible via the microprocessor.

For testing and debugging, this two-frame-wide elastic buffer may be reset via the microprocessor to its center point (see register iEH).

Figure 5. Frame and Multiframe Acquisition

A maskable interrupt is also provided to indicate the inoperability of the elastic store. This alarm indicates that the clock frequencies are so different that slippage is continual.

By setting a special configuration in register iEH, the transmit retiming 2 frame-wide elastic store (512 bits) may be used to retime an un-framed 2.048 Mbit/s signal for wander elimination. In this case, the read and write pointer of the FIFO are independent of the framing algorithm and operate in complete free running mode, but the CRC-4, REBE and remote alarm monitoring are un-valid, as the 2.048 Mbit/s input signal is considered un-framed.

The retiming elastic store can be bypassed by using the dejittering circuitry or configuring the data path in pass-through mode (see register iEH).

# 3.1.7 De-jittering Circuitry

The de-jittering circuitry consists of the dejitter FIFO and a jitter attenuator or phase lock loop. This function can be bypassed by using the retiming function or configuring the data path in pass-through mode (see register iEH).

The dejitter FIFO is a 32-bit asynchronous FIFO, whose write clock is the input gapped clock (DTCx) at 2.048MHz +/- 50 ppm average frequency, and whose read clock is the phase-locked and filtered output of the jitter attenuator (the ADPLL).

The jitter attenuator is a second order All Digital Phase Lock Loop with a 2.0 Hz loop bandwidth. The reference and sample clock of the digital PLL is provided by the high speed clock input pin DPLLCKREF at 65.536 MHz +/- 50 ppm. DPLLCKREF reference clock is provided by an external crystal oscillator. When the de-jittering circuitry is not selected in a transmitter, the high speed clock is shut down in this specific transmitter to save power consumption.

A maskable interrupt is provided to indicate dejitter FIFO overflows.

#### 3.1.8 AIS Signal Insertion

An AIS signal (unframed all ones signal) can be generated using the external clock input DRETCKREF at 2.048 MHz +/- 50 ppm (if the transmitter is configured to operate in retiming or passed through mode) or using the high-speed ADPLL reference clock at 65.536 MHz +/- 50 ppm divided by 32 (if the transmitter is configured to operate in dejitter mode), as a blue clock on the E1 transmitter output.

When the transmitter is configured to operate in dejitter mode, an AIS signal may be automatically hardware inserted when enabled (see registers iEH and AFH), if the dejitter ADPLL is unlocked and the FIFO crashed. In this case, the AIS blue clock is derived from the high-speed PLL reference clock (+/- 50 ppm), and the transition from non-AIS clock to AIS blue clock (and the inverse) is always smooth. The AIS state is accessible to the microprocessor via the global status register 9FH.

#### 3.1.9 Line Coding HDB3

The serial E1 output is a HDB3 signal output on TPOSD and TNEGD. The output clock is TCLK (2.048 MHz). For testing, it is possible to insert (microprocessor configurable) BPV errors on TPOSD and TNEGD output data. A single code error, one error every 1024 bits (BER 10-3), one error every multiframe, or one error every second may be inserted.

If the HDB3 encoder is not used, TPOSD is used as an NRZ output.

The relative phase between output data and clock can be configured via microprocessor (TPOSDx/TNEGDx data outputs emitted on rising or falling edge of the output clock TCLKx: see global register AFH).

Depending on the transmitter configuration, TCLK transmit clock output may be provided by different sources:

Table 3. Transmitter clock output scheme

| TCLK clock sources             | Synchronous with   | Clock source          |

|--------------------------------|--------------------|-----------------------|

| Retiming Mode (No AIS or AIS)  | DRETCKREF input    | DRETCKREF             |

| Dejitter Mode (No AIS)         | DTC input          | ADPLL filtered output |

| Dejitter Mode (AIS insert)     | DPLLCKREF input/32 | DPLLCKREF/32          |

| Pass Through Mode (No AIS)     | DTC input          | DTC                   |

| Pass Through Mode (AIS insert) | DRETCKREF input    | DRETCKREF             |

### 3.1.10 Receiver Operation

#### 3.1.10.1 Line decoding HDB3

The HDB3 decoder is microprocessor selectable. When selected, this block accepts an HDB3 encoded E1 signal via data inputs RPOSDx and RNEGDx and clock RCLKx. A bipolar violation (or code error) detector is implemented in the HDB3 decoder. The Bipolar Violation (BPV) Errors Detector can be configured for all the E1 HDB3 receivers via the microprocessor. The detector can:

- be disabled

- detect two consecutive '1's' with the same polarity (except when it is used as part of a valid HDB3 substitution)

- detect BPV that do not alternate polarity (recommendation ITU O161)

- detect two consecutive '1' with the same polarity, or BPV that do not alternate polarity, or four consecutive '0' badly encoded.

BPV errors are accumulated in a 16-bit counter that can be read by the microprocessor. A maskable interrupt is provided to indicate counter overflows.

If the HDB3 decoder is not used, the E1 NRZ data is input on RPOSD. In this case, RNEGD input pin has to be grounded, and the BPV error detection is invalid.

The relative phase between E1 data (on RPOSDx/RNEGDx pins) and clock (on RCLKx pin) inputs can be configured via microprocessor (RPOSDx/RNEGDx data inputs may be sampled, in the transmitter, by rising or falling edge of the input clock RCLKx: see global register AFH).

#### 3.1.10.2 AIS Detection

After HDB3 decoding, an AIS detection is performed on the incoming data according to recommendation ITU G.775.

AIS defect alarm is declared when each of two consecutive double frame periods (512 bits) has two or less ZEROs, and the alarm is cleared when three or more ZEROs or when the Frame Alignment Signal has been found in each of two consecutive double frame periods.

The AIS defect alarm status is accessible to the microprocessor via the status registers.

#### 3.1.10.3 AIS Insert/LOS Alarm filtering

This block includes a filter for Loss Of Signal Alarm input on RLOS pin from the external LIU. The filtering on the LOS can be integrated over 128 clock cycles or disabled via microprocessor.

An AIS signal (unframed all ones in the data) can be inserted on the incoming data RPOSD and RNEGD after decoding in case of LOS alarm. DRETCKREF clock reference input (2.048 MHz +/ - 50 ppm) may be used as a blue clock for AIS generation, if the receiver is so configured. The AIS insert can also be disabled or forced via microprocessor (see configuration register jEH). The AIS state for every receiver is reported in the global status registers.

#### 3.1.10.4 Frame Alignment/Out Of Frame Alarm

The framing method follows the rules set forth in CCITT/ITU recommendations G.704 and G.706 and is the same as the one described in the transmitter. Refer to Section 3.1.2, "Frame Alignment" on page 18 and Figure 5 on page 22.

Out Of Frame status changes are indicated via a maskable interrupt, and errored FAS/NFAS (see global configuration register 0FH) are counted via a 13- bit microprocessor-accessible counter.

#### 3.1.10.5 CRC-4 Multiframe Alignment/Out of CRC Multiframe Alarm

The multiframe acquisition is the same as in the transmitter. Refer to CRC-4 Multiframe Alignment on page 14.

Loss Of CRC-4 Multiframe status changes are indicated via a maskable interrupt.

#### 3.1.10.6 CRC-4 Multiframe Monitoring

#### **CRC-4 Block Errors Calculation**

Once the CRC-4 multiframe is acquired, the CRC-4 bits are calculated internally based on a submultiframe (as specified in recommendation ITU G704) and compared to the incoming CRC-4 value in the next sub-multiframe. The block errors are accumulated in a 10-bit counter that can be read by the microprocessor. A maskable interrupt is provided to indicate counter overflows.

#### **Remote End Block Errors**

Two bits per multiframe (RE1 and RE2) are allocated for the CRC-4 Remote End Block Error (REBE) indication. REBEs are accumulated in a 10-bit counter that can be read by the microprocessor. A maskable interrupt is provided to indicate counter overflows.

#### **Remote Alarm**

The Remote alarm bit (bit 3 in the NFAS) is used to tell the transmit end that the received end has detected a loss of signal or loss of frame. The remote alarm is filtered for three consecutive frames before being declared a new value. A change in its status is indicated to the microprocessor via a maskable interrupt.

#### **Output Interface**

NRZ receive data and clock are emitted on MTDx and MTCx pins. MTCx clock is synchronous with an RCLKx input clock or DRETCKREF blue clock if AIS is inserted in the receiver or if in Autotest Mode. The relative phase between output data and clock can be configured via the microprocessor (MTDx data outputs emitted on the rising or falling edge of the output clock MTCx: see global register AFH).

#### 3.1.10.7 Test Pattern Generator for Autotesting/Maintenance

#### **CRC-4 E1 Framed Test Pattern**

An internal E1 framed pattern generator may be enabled via the microprocessor for autotesting and maintenance purposes. The sequence consists of an E1 CRC-4 framed signal with the FAS, NFAS, MFAS and CRC-4 bits in the time slots 0 and a PRBS 2E15-1 sequence in the time slots 1 ->31.

If enabled (see registers 1FH and jEH), the E1 framed test pattern sequence is sent to the receiver input and then emitted on MTD data output pin, with the associated DRETCKREF blue clock emitted on MTC clock output pin. So, by looping back externally, the MTC/MTD output signals to the DTC/DTD input signals, the chip can be autotested without any external test equipment.

#### **PRBS Unframed Test Pattern**

If enabled (see registers 1FH and jEH), the internal test pattern generator can also generate the standard pseudo-random (2E15-1 sequence) unframed test signal used for E1 jitter analysis (Recommendation ITU-T O171) emitted on MTD data output pin, with the associated DRETCKREF blue clock emitted on MTC clock output pin.

#### 3.1.11 MICROCONTROLLER INTERFACE

This section contains a description of the asynchronous microprocessor interface. A microprocessor should be connected to the LXT6282 for reading and writing data via the microprocessor interface pins.

The microprocessor interface is a generic asynchronous interface, including an address bus (A [7..0]), data bus (DATA [7..0]) and handshaking pins (WRB/RWB, RDB/E, CSB, and ALE). The MCUTYPE input pin indicates the type of microprocessor interface to be used – Intel or Motorola. There is also an INT output pin that indicates status changes to the microprocessor.

This interface has the same features as Intel's LXT6051 and LXT6251A chips.

#### 3.1.11.1 Intel Interface

The Intel interface is indicated by driving the MCUTYPE input pin LOW. It uses the WRB/RWB input pin as WRB and the RDB/E input pin as RDB.

A read cycle is indicated to the LXT6282 by the uP forcing a LOW on the RDB pin with the WRB pin held HIGH.

A write cycle is indicated to the LXT6282 by the uP forcing a LOW on the WRB pin with the RDB pin held HIGH.

Both cycles require the CSB pin to be LOW and the uP to drive the A[7..0] address pins. In the case of the write cycle, the uP is also required to drive the DATA [7..0] data pins. In the case of the read cycle, the LXT6282 drives the DATA [7..0] data pins.

When a multiplexed data/address bus is used, the falling edge of the ALE input latches the address provided on the muxed bus (the muxed bus will be connected to both the A[7..0] and DATA[7..0]). If the address and data are not multiplexed the ALE pin should be tied HIGH.

#### 3.1.11.2 Motorola Interface

The Motorola interface is indicated by driving the MCUTYPE input pin HIGH. It uses the WRB/RWB input pin as RWB and the RDB/E input pin as E.

A read cycle is indicated to the LXT6282 by the uP forcing a HIGH on the RWB pin. A write cycle is indicated to the LXT6282 by the uP forcing a LOW on the RWR pin.

A LOW on the E input initiates both cycles. The E input is connected to the E output from the Motorola uP and is typically a 50% duty cycle waveform with a frequency derived from the uP clock.

Both cycles require the CSB pin to be LOW and the uP to drive the A[7..0] address pins. In the case of the write cycle, the uP is also required to drive the DATA [7..0] data pins. In the case of the read cycle, the LXT6282 drives the DATA [7..0] data pins.

When a multiplexed data/address bus is used, the falling edge of the ALE input latches the address provided on the muxed bus (the muxed bus will be connected to both the A[7..0] and DATA[7..0]). If the address and data are not multiplexed the ALE pin should be tied HIGH.

### 3.1.12 linterrupt Handling

#### 3.1.12.1 Interrupt Sources

There are three types of interrupt sources:

- Status change of a monitoring process: For example, the LXT6282 monitors the incoming E1 frame for the correct framing pattern and updates the OofSt and LofSt status bits to indicate presence or absence of Out Of Frame and Loss Of Frame conditions. When the value of these status bits change an interrupt is generated if enabled.

- Event Occurrence: For example, positive and negative slips as well as FIFO overflows are considered "events" and can generate interrupts if enabled.

- Counter overflows: For example, the LXT6282 monitors the E1 frame structure for framing errors. These errors are recorded in a counter whose overflow can cause an interrupt if enabled.

#### 3.1.12.2 Interrupt Enables

In order for an interrupt source to affect the state of the INT output pin its associated interrupt enable bit must be SET. The setting (whether it is 0 or 1) of the interrupt enables does not affect the updating of the status registers or counters.

Assuming the interrupt enable for a particular interrupt source is SET and the interrupt source is active, its interrupt bit will be SET. The primary difference between each interrupt type is the way its respective interrupt bit is cleared.

#### 3.1.12.3 Interrupt Clearing

In the discussion below it is assumed that the example interrupt sources have their interrupt enable bits SET.

Status change interrupt sources have their interrupt bits cleared when their status is read. For example, say the OofSt bit changes from zero to one (in frame to out of frame). Its interrupt bit is SET by this event. When the microprocessor reads the register containing the OofSt bit its interrupt bit will be CLEARED. If the OofSt bit subsequently changes from one to zero (out of frame to in frame) again its interrupt bit is SET by this event and then CLEARED when the status is read.

The interrupt register can be read again only after three interval clock cycles (1.47) have completed since it has been cleared (by reading its associated status registers).

It should be noted that updates to status bits are not affected by the interrupt bit state. For example, the OofSt bit could change from a one to zero (generating an interrupt) and then before the microprocessor reads OofSt it could change back to one. This would have no affect on its interrupt bit since it would already be SET. When the microprocessor reads the OofSt bit it would read a one.

Both event interrupts and counter overflow interrupts are cleared when the interrupt register containing these bits is read (since event and counters do not have any associated status registers).

#### 3.1.12.4 Status Registers Access

Due to the asynchronous nature of the microprocessor interface and timing differences during interrupt bit updates, it is possible that a status bit change can fail to SET its associated interrupt bit if the <u>AlmUpdDsbl</u> bit is not SET during a read of the status registers by the microprocessor. This situation is very difficult to achieve however, it can happen.

For this reason we encourage programmers to SET the <u>AlmUpdDsbl</u> bit before accessing the status registers during alarm processing. This effectively locks out internal processes that wish to access the status and interrupt bits during the time that the microprocessor is accessing these bits. After the microprocessor is done accessing the status registers it should CLEAR the <u>AlmUpdDsbl</u> bit so that internal processes may again update the status and interrupt bits.

#### 3.1.12.5 Counter Reading

Counters are read by first buffering their contents and then reading the buffer. They can be individually buffered or group buffered. They are group buffered by writing to register BfrAllCntrs (5FH). They are individually buffered by writing to the most significant byte of a particular buffer. After buffering the counter, the contents of the buffer are read at the address specified in the register definition.

For example, to read the contents of the transmitter #1 FrameWord counter a write to register 07H will buffer only the contents of transmitter #1's frame word counter. A read of registers 06H and 07H will give the counter value. Alternatively, all of the frame word counters for all 8 transmitters and receivers can be buffered by writing a 02H to register 5FH.

A counter can be read only after three interval clock cycles (1.47) have completed since it has been buffered (previous write operation. (JCC)

# 4.0 Microprocessor Register Description

The address mapping (8 address bits) is the following:

- addresses 0FH -> AFH: Global registers