# DALLAS SEMICONDUCTOR

# DS3100 Stratum 3/3E Timing Card IC

#### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

When paired with an external TCXO or OCXO, the DS3100 is a complete central timing and synchronization solution for SONET/SDH network elements. With two multiprotocol BITS/SSU receivers and 14 input clocks, the device directly accepts both external timing and line timing from a large number of line cards. All input clocks are continuously monitored for frequency accuracy and activity. Any two of the input clocks can be selected as the references for the two core DPLLs. The T0 DPLL complies with the stratum 3 and 3E requirements of GR1244, GR-253, and the requirements of G.812 Type III and G.813. From the output of the core DPLLs, a wide variety of output clock frequencies and frame pulses can be produced simultaneously on the 11 output clock pins. Two DS3100 devices can be configured in a master/slave arrangement for timing card equipment protection.

The DS3100 registers and I/O pins are backward compatible with Semtech's ACS8520 and ACS8530 timing card ICs.

## **APPLICATIONS**

SONET/SDH ADMs, MSPPs, and MSSPs Digital Cross-Connects DSLAMs Service Provider Routers

## FUNCTIONAL DIAGRAM

## FEATURES

Synchronization Subsystem for Stratum 3E, 3, 4E and 4, SMC and SEC

Meets Requirements of GR-1244 Stratum 3/3E, GR-253, G.812 Types I and III, and G.813 Stratum 3E Holdover Accuracy with Suitable

External Oscillator Programmable Bandwidth, 0.5MHz to 70Hz Hitless Reference Switching on Loss of Input Phase Build-Out and Transient Absorption Locks To and Generates 125MHz for Timing Over Gigabit Ethernet per ITU-T G.pactiming

#### 14 Input Clocks

10 CMOS/TTL Inputs Accept 2kHz, 4kHz, and Any Multiple of 8kHz Up to 125MHz

Two LVDS/LVPECL/CMOS/TTL Inputs Accept Nx8kHz Up to 125MHz Plus 155.52MHz Two 64kHz Composite Clock Receivers

Continuous Input Clock Quality Monitoring Separate 2/4/8kHz Frame Sync Input

11 Output Clocks

Five CMOS/TTL Outputs Drive Any Internally Produced Clock Up to 77.76MHz

Two LVDS Outputs Each Drive Any Internally Produced Clock Up to 311.04MHz One 64kHz Composite Clock Transmitter

One 1.544MHz/2.048MHz Output Clock Two Sync Pulses: 8kHz and 2kHz

Output Clock Rates Include 2kHz, 8kHz, NxDS1, NxDS2, DS3, NxE1, E3, 6.48MHz, 19.44MHz, 38.88 MHz, 51.84MHz, 62.5MHz, 77.76MHz, 125MHz, 155.52MHz, 311.04MHz

Two Multiprotocol BITS/SSU Transceivers Receive and Transmit DS1, E1, 2048kHz, and 6312kHz Timing Signals

Insert and Extract SSM Messages (DS1, E1) Automatically Invalidate Clocks on LOS, OOF, AIS, and Other Defects

- Internal Compensation for Master Clock Oscillator Frequency Accuracy

- Processor Interface: 8-Bit Parallel or SPI Serial

- 1.8V Operation with 3.3V I/O (5V Tolerant)

## ORDERING INFORMATION

| PART                        | TEMP RANGE     | PIN-PACKAGE                    |  |

|-----------------------------|----------------|--------------------------------|--|

| DS3100GN                    | -40°C to +85°C | 256 CSBGA (17mm <sup>2</sup> ) |  |

| DS3100GN+                   | -40°C to +85°C | 256 CSBGA (17mm <sup>2</sup> ) |  |

| + Depotes lead free package |                |                                |  |

+Denotes lead-free package.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <u>www.maxim-ic.com/errata</u>.

## TABLE OF CONTENTS

| 1. | STA        |                                                                | 7   |

|----|------------|----------------------------------------------------------------|-----|

| 2. | BLC        | OCK DIAGRAM                                                    | 8   |

| 3. | APP        |                                                                | 9   |

| 4. | DET        | AILED DESCRIPTION                                              | 10  |

| 5. | DET        | AILED FEATURES                                                 | 12  |

|    |            | TO DPLL FEATURES.                                              |     |

|    | 5.1<br>5.2 |                                                                |     |

|    |            | T4 DPLL FEATURES<br>INPUT CLOCK FEATURES                       |     |

|    | 5.3        |                                                                |     |

|    | 5.4        | OUTPUT CLOCK FEATURES                                          |     |

|    | 5.5        | REDUNDANCY FEATURES                                            |     |

|    | 5.6        | BITS TRANSCEIVER FEATURES                                      |     |

|    |            | 5.6.1 General<br>5.6.2 Receiver                                |     |

|    |            | 5.6.3 Transmitter                                              | -   |

|    | 5.7        | COMPOSITE CLOCK I/O FEATURES.                                  |     |

|    | 5.8        | GENERAL FEATURES                                               |     |

|    |            |                                                                |     |

| 6. | PIN        | DESCRIPTIONS                                                   | 15  |

| _  |            |                                                                | ~ . |

| 1. | FUN        |                                                                | 24  |

|    | 7.1        | OVERVIEW                                                       | 24  |

|    | 7.2        | DEVICE IDENTIFICATION AND PROTECTION                           | 25  |

|    | 7.3        | LOCAL OSCILLATOR AND MASTER CLOCK CONFIGURATION                | 25  |

|    | 7.4        | INPUT CLOCK CONFIGURATION                                      |     |

|    |            | 7.4.1 Signal Format Configuration                              |     |

|    |            | 7.4.2 Frequency Configuration                                  |     |

|    | 7.5        | INPUT CLOCK QUALITY MONITORING                                 | 29  |

|    |            | 7.5.1 Frequency Monitoring                                     |     |

|    |            | 7.5.2 Activity Monitoring                                      |     |

|    |            | 7.5.3 Selected Reference Activity Monitoring                   |     |

|    |            | 7.5.4 Composite Clock Inputs                                   |     |

|    | 7.6        | INPUT CLOCK PRIORITY, SELECTION, AND SWITCHING                 |     |

|    |            | 7.6.1 Priority Configuration                                   |     |

|    |            | 7.6.2 Automatic Selection Algorithm                            |     |

|    |            | <ul> <li>7.6.3 Forced Selection</li></ul>                      |     |

|    |            | 7.6.5 External Reference Switching Mode                        |     |

|    |            | 7.6.6 Output Clock Phase Continuity During Reference Switching |     |

|    | 7.7        | DPLL Architecture and Configuration                            |     |

|    | 1.1        |                                                                | 33  |

|    |            | 7.7.2 T4 DPLL State Machine                                    |     |

|    |            | 7.7.3 Bandwidth                                                |     |

|    |            | 7.7.4 Damping Factor                                           |     |

|    |            | 7.7.5 Phase Detectors                                          |     |

|    |            | 7.7.6 Loss of Phase Lock Detection                             |     |

|    |            | 7.7.7 Phase Monitor and Phase Build-Out                        |     |

|    |            | 7.7.8 Input to Output Phase Adjustment                         |     |

|    |            | 7.7.9 Phase Recalibration                                      |     |

|    |            | 7.7.10 Frequency and Phase Measurement                         |     |

|    |            | 7.7.11 Input Wander and Jitter Tolerance                       | 42  |

|     |       | 7.7.12 Jitter and Wander Transfer                                                                                |     |

|-----|-------|------------------------------------------------------------------------------------------------------------------|-----|

|     |       | 7.7.13 Output Jitter and Wander                                                                                  |     |

|     | 7.8   | OUTPUT CLOCK CONFIGURATION                                                                                       | 44  |

|     |       | 7.8.1 Signal Format Configuration                                                                                |     |

|     |       | 7.8.2 Frequency Configuration                                                                                    |     |

|     | 7.9   | EQUIPMENT REDUNDANCY CONFIGURATION                                                                               | 54  |

|     |       | 7.9.1 Master-Slave Pin Feature                                                                                   |     |

|     |       | 7.9.2 Master-Slave Output Clock Phase Alignment                                                                  | 55  |

|     |       | 7.9.3 Master-Slave Frame and Multi-Frame Alignment with the SYNC2K Pin                                           |     |

|     | 7.10  | MULTIPROTOCOL BITS TRANSCEIVERS                                                                                  |     |

|     |       | 7.10.1 Master Clock Connections                                                                                  |     |

|     |       | 7.10.2 Receiver Clock Connections                                                                                |     |

|     |       | 7.10.3 Transmitter Clock Connections                                                                             |     |

|     |       | 7.10.4 Line Interface Unit                                                                                       |     |

|     |       | 7.10.5 DS1 Synchronization Interface                                                                             |     |

|     |       | 7.10.6 E1 Synchronization Interface                                                                              |     |

|     |       | 7.10.7 G.703 2048kHz Synchronization Interface                                                                   |     |

|     | 7 4 4 | 7.10.8 G.703 Appendix II 6312kHz Japanese Synchronization Interface<br>COMPOSITE CLOCK RECEIVERS AND TRANSMITTER |     |

|     | 1.11  |                                                                                                                  |     |

|     |       | 7.11.1 IC1 and IC2 Receivers                                                                                     |     |

|     | 7 1 2 | 7.11.2 OC8 Transmitter                                                                                           |     |

|     | 1.12  | 7.12.1 Parallel Interface Modes                                                                                  |     |

|     |       | 7.12.1 Parallel Interface Modes                                                                                  |     |

|     | 7 12  | RESET LOGIC                                                                                                      |     |

|     |       | POWER-SUPPLY CONSIDERATIONS                                                                                      |     |

|     |       |                                                                                                                  |     |

|     |       | INITIALIZATION                                                                                                   |     |

| 8.  | REG   | GISTER DESCRIPTIONS                                                                                              | 81  |

|     | 8.1   | STATUS BITS                                                                                                      |     |

|     | 8.2   | CONFIGURATION FIELDS                                                                                             |     |

|     | 8.3   | MULTIREGISTER FIELDS                                                                                             |     |

|     | 8.4   | CORE REGISTER DEFINITIONS.                                                                                       |     |

|     | 8.5   | BITS TRANSCEIVER REGISTER DEFINITIONS                                                                            |     |

| ~   |       |                                                                                                                  |     |

| 9.  | JIA   | G TEST ACCESS PORT AND BOUNDARY SCAN                                                                             |     |

|     | 9.1   | JTAG DESCRIPTION                                                                                                 |     |

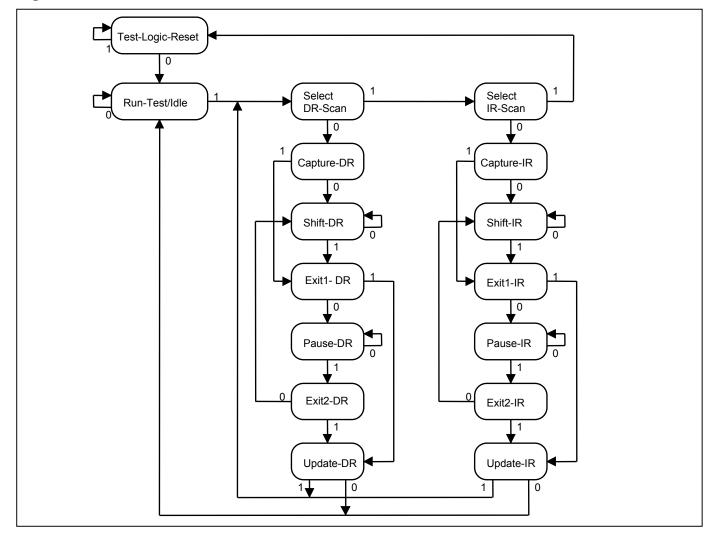

|     | 9.2   | JTAG TAP CONTROLLER STATE MACHINE DESCRIPTION                                                                    | 199 |

|     | 9.3   | JTAG INSTRUCTION REGISTER AND INSTRUCTIONS                                                                       | 201 |

|     | 9.4   | JTAG TEST REGISTERS                                                                                              | 202 |

| 10. | ELE   | CTRICAL CHARACTERISTICS                                                                                          |     |

|     |       | DC CHARACTERISTICS                                                                                               |     |

|     |       |                                                                                                                  |     |

|     |       | INPUT CLOCK TIMING                                                                                               |     |

|     |       |                                                                                                                  |     |

|     |       | BITS TRANSCEIVER TIMING                                                                                          |     |

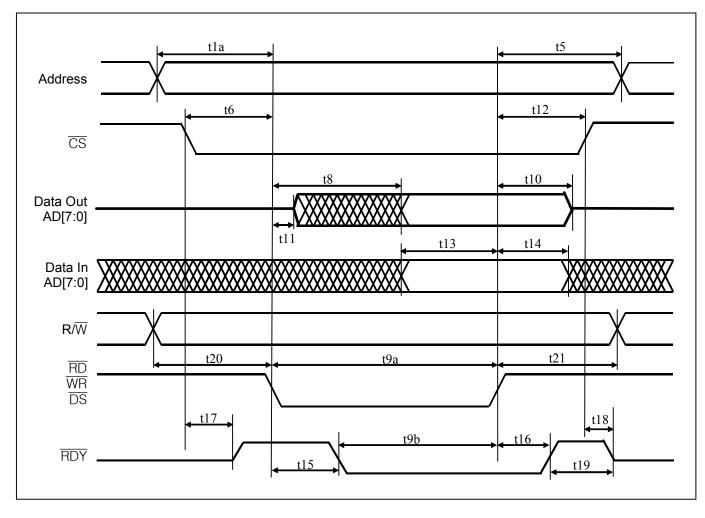

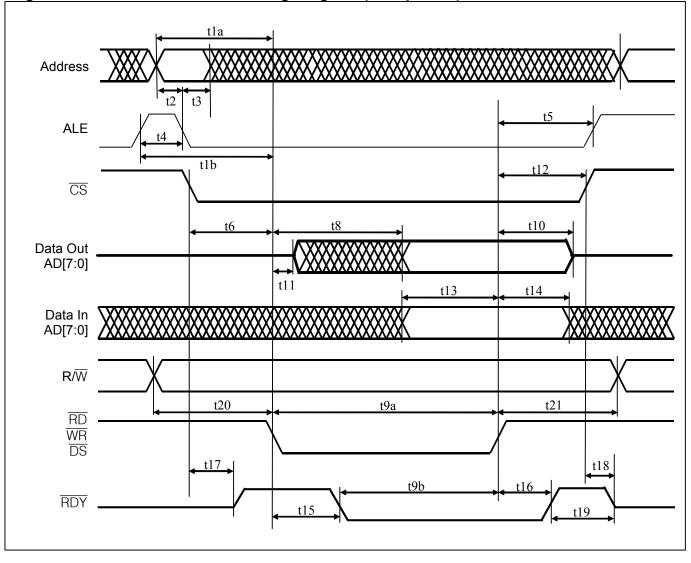

|     |       | PARALLEL INTERFACE TIMING                                                                                        |     |

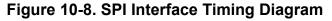

|     |       | SPI INTERFACE TIMING                                                                                             |     |

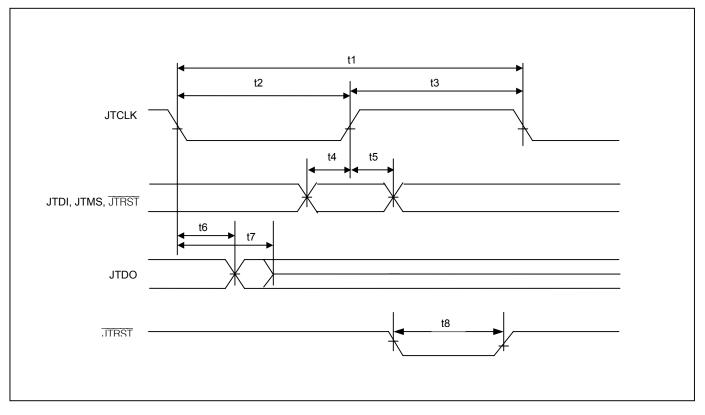

|     |       | JTAG INTERFACE TIMING                                                                                            |     |

| 11. | PIN   | ASSIGNMENTS                                                                                                      | 215 |

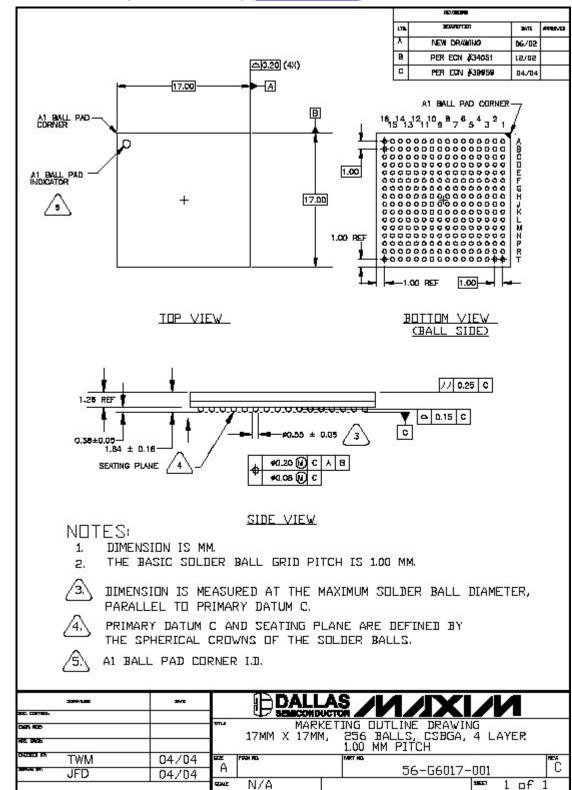

| 12  | ΡΔΟ   | KAGE INFORMATION                                                                                                 | 221 |

|     |       | 256-Pin CSBGA (17мм х 17мм) (56-G6017-001)                                                                       |     |

| 40  |       |                                                                                                                  |     |

| 13. | IHE   | RMAL INFORMATION                                                                                                 |     |

| 14. GLOSSARY                    | 223 |

|---------------------------------|-----|

| 15. ACRONYMS AND ABBREVIATIONS  | 224 |

| 16. TRADEMARK ACKNOWLEDGEMENTS  | 224 |

| 17. DATA SHEET REVISION HISTORY | 225 |

## LIST OF FIGURES

| Figure 2-1. DS3100 Block Diagram                                          | 8   |

|---------------------------------------------------------------------------|-----|

| Figure 3-1. Typical Application Example                                   |     |

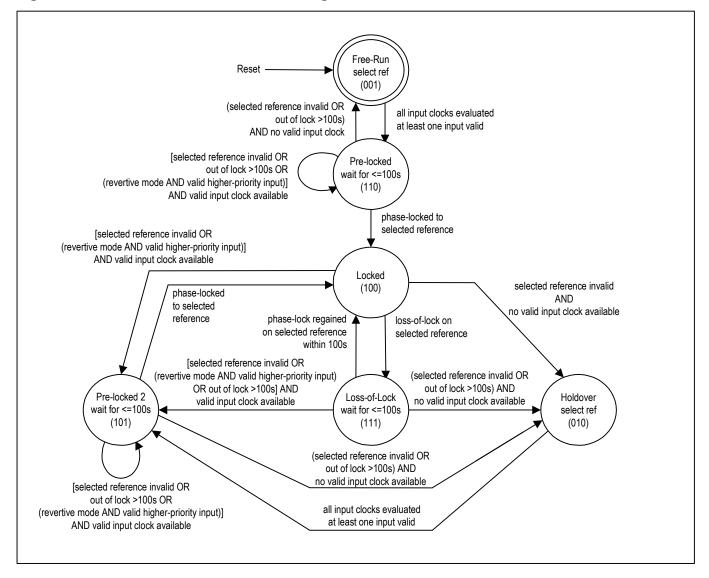

| Figure 7-1. T0 DPLL State Transition Diagram                              |     |

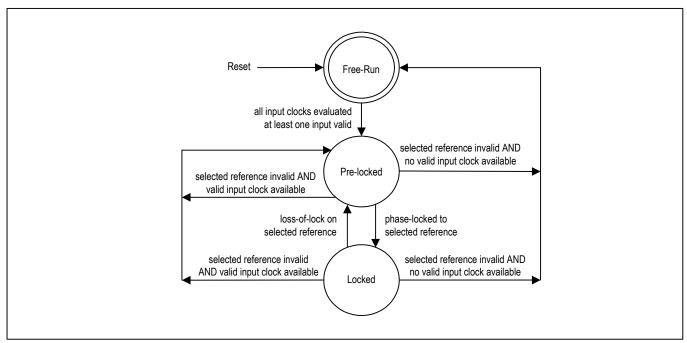

| Figure 7-2. T4 DPLL State Transition Diagram                              |     |

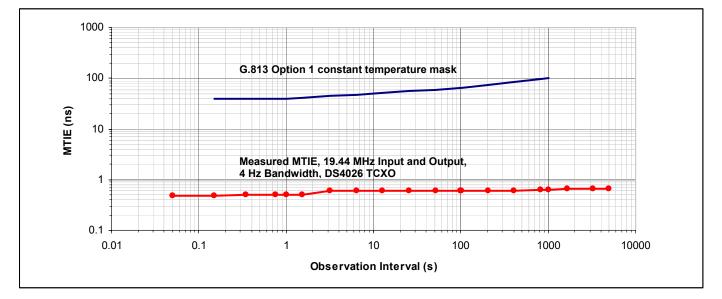

| Figure 7-3. Typical MTIE for T0 DPLL Output                               | 43  |

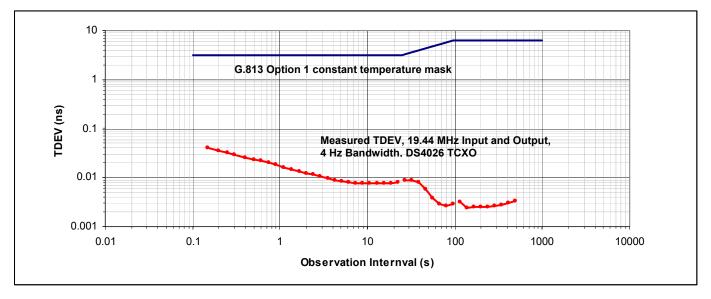

| Figure 7-4. Typical TDEV for T0 DPLL Output                               | 44  |

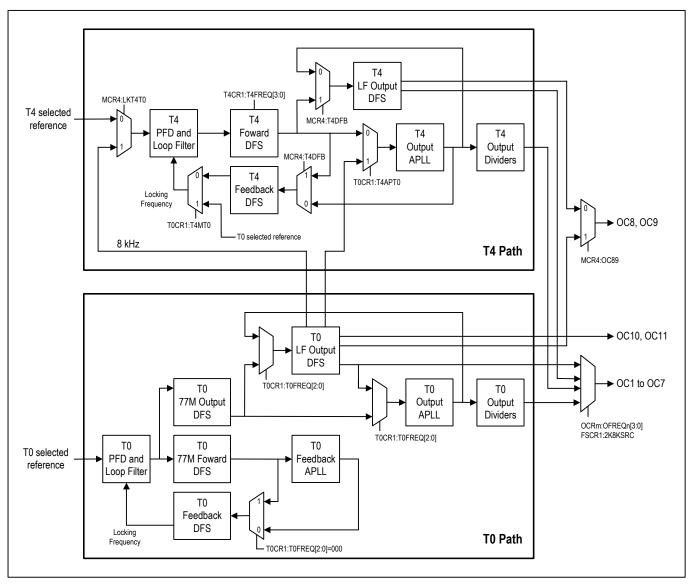

| Figure 7-5. DPLL Block Diagram                                            |     |

| Figure 7-6. OC10 8kHz Options                                             |     |

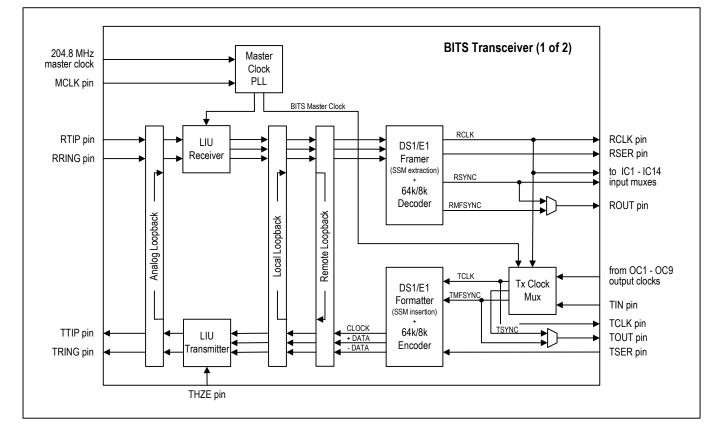

| Figure 7-7. BITS Transceiver Block Diagram                                | 58  |

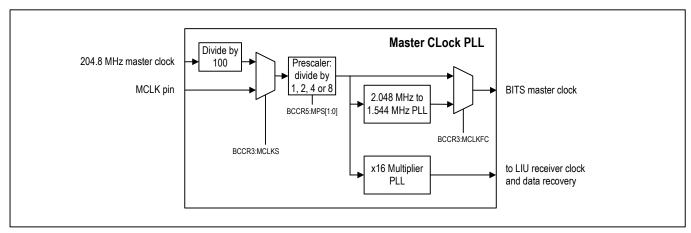

| Figure 7-8. BITS Transceiver Master Clock PLL Block Diagram               | 59  |

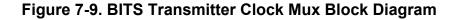

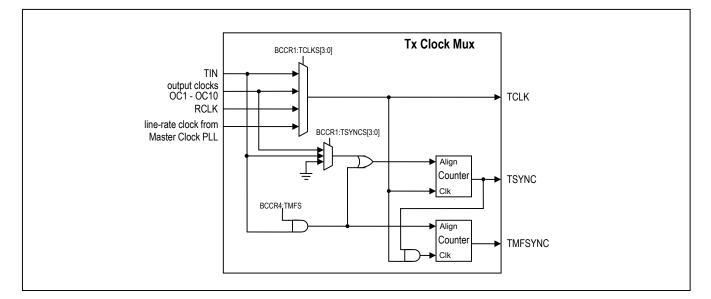

| Figure 7-9. BITS Transmitter Clock Mux Block Diagram                      | 60  |

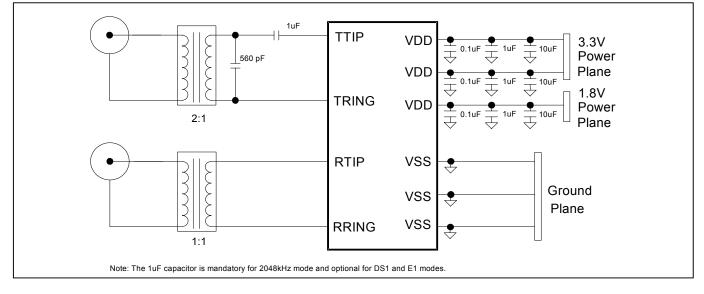

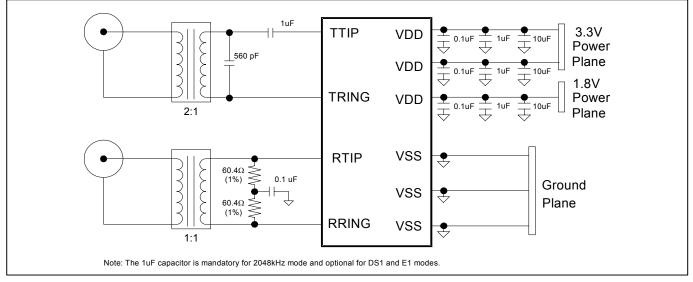

| Figure 7-10. BITS Transceiver External Components                         | 62  |

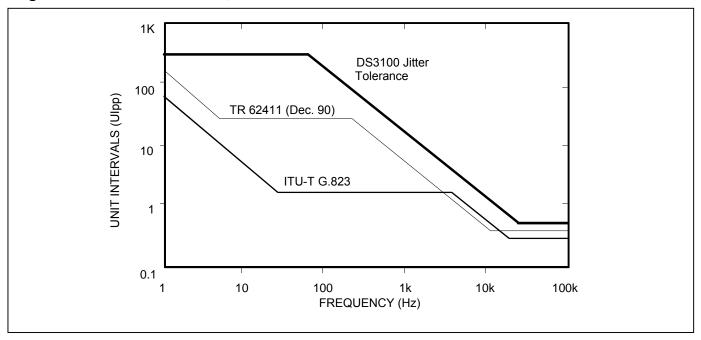

| Figure 7-11. Jitter Tolerance, DS1 Mode                                   |     |

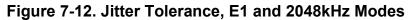

| Figure 7-12. Jitter Tolerance, E1 and 2048kHz Modes                       | 64  |

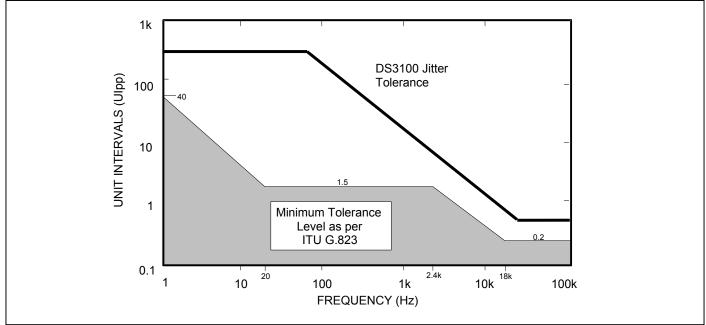

| Figure 7-13. Transmit Pulse Template, DS1 Mode                            |     |

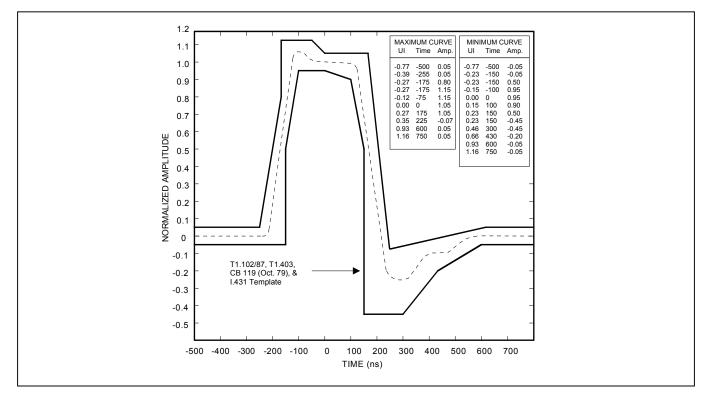

| Figure 7-14. Transmit Pulse Template, E1 Mode                             | 66  |

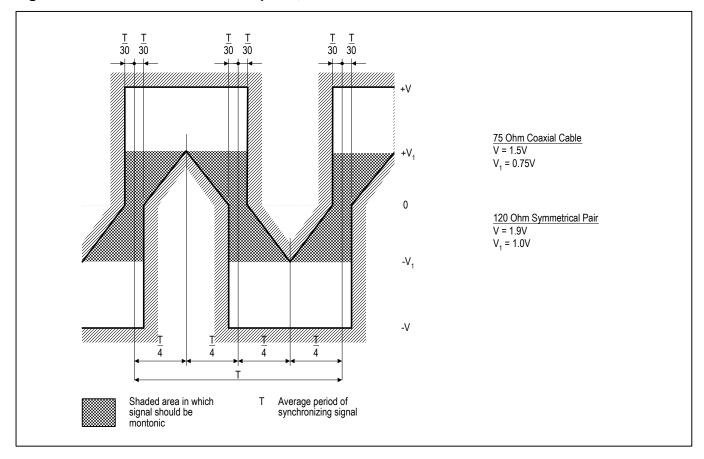

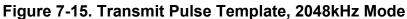

| Figure 7-15. Transmit Pulse Template, 2048kHz Mode                        |     |

| Figure 7-16. FAS/Si/RAI/Sa Source Logic                                   |     |

| Figure 7-17. GR-378 Composite Clock Pulse Mask                            |     |

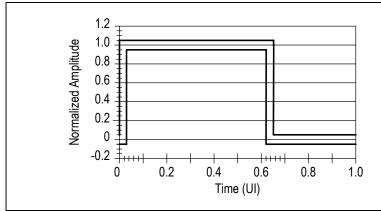

| Figure 7-18. SPI Clock Polarity and Phase Options                         |     |

| Figure 7-19. SPI Bus Transactions                                         |     |

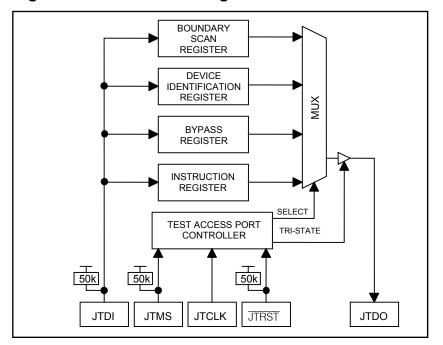

| Figure 9-1. JTAG Block Diagram                                            | 198 |

| Figure 9-2. JTAG TAP Controller State Machine                             | 200 |

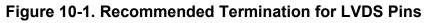

| Figure 10-1. Recommended Termination for LVDS Pins                        |     |

| Figure 10-2. Recommended Termination for LVPECL Pins                      |     |

| Figure 10-3. Recommended External Components for AMI Composite Clock Pins |     |

| Figure 10-4. BITS Receiver Timing Diagram                                 |     |

| Figure 10-5. BITS Transmitter Timing Diagram                              |     |

| Figure 10-6. Parallel Interface Timing Diagram (Nonmultiplexed)           |     |

| Figure 10-7. Parallel Interface Timing Diagram (Multiplexed)              |     |

| Figure 10-8. SPI Interface Timing Diagram                                 |     |

| Figure 10-9. JTAG Timing Diagram                                          |     |

| Figure 11-1. DS3100 Pin Assignment—Left Half                              |     |

| Figure 11-2. DS3100 Pin Assignment—Right Half                             | 220 |

## LIST OF TABLES

| Table 1-1. Applicable Telecom Standards                                                                                       |       |

|-------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 6-1. Input Clock Pin Descriptions                                                                                       | 15    |

| Table 6-2. Output Clock Pin Descriptions                                                                                      | 16    |

| Table 6-3. BITS Receiver Pin Descriptions                                                                                     | 17    |

| Table 6-4. BITS Transmitter Pin Descriptions                                                                                  | 18    |

| Table 6-5. Global Pin Descriptions                                                                                            | 19    |

| Table 6-6. Parallel Interface Pin Descriptions                                                                                | 20    |

| Table 6-7. SPI Bus Mode Pin Descriptions                                                                                      | 21    |

| Table 6-8. JTAG Interface Pin Descriptions                                                                                    |       |

| Table 6-9. General-Purpose I/O Pin Descriptions                                                                               |       |

| Table 6-10. Power-Supply Pin Descriptions                                                                                     |       |

| Table 7-1. GR-1244 Stratum 3E/3 Stability Requirements                                                                        |       |

| Table 7-2. Input Clock Capabilities                                                                                           |       |

| Table 7-3. Locking Frequency Modes                                                                                            | 28    |

| Table 7-4. Default Input Clock Priorities                                                                                     |       |

| Table 7-5. Damping Factors and Peak Jitter/Wander Gain                                                                        |       |

| Table 7-6. T0 Adaptation for T4 Phase Measurement Mode                                                                        |       |

| Table 7-7. Output Clock Capabilities                                                                                          |       |

| Table 7-8. Digital1 and Digital2 Frequencies.                                                                                 |       |

| Table 7-9. APLL Frequency to Output Frequencies (T0 and T4)                                                                   |       |

| Table 7-10. TO APLL Frequency to TO Path Configuration                                                                        |       |

| Table 7-11. T4 APLL Frequency to T4 Path Configuration                                                                        |       |

| Table 7-12. OC1 to OC7 Output Frequency Selection                                                                             |       |

| Table 7-13. Possible Frequencies for OC1 to OC7                                                                               |       |

| Table 7-14. Equipment Redundancy Methodology                                                                                  |       |

| Table 7-15. Transformer Specifications                                                                                        | 67    |

| Table 7-16. DS1 Alarm Criteria.                                                                                               |       |

| Table 7-17. E1 Alarm Criteria                                                                                                 |       |

| Table 7-17. ET Alarm Chiena                                                                                                   |       |

| Table 7-19. 2048kHz Synchronization Interface Specification                                                                   |       |

| Table 7-19. 2040k12 Synchronization Interface Specification       Table 7-20. 6312kHz Synchronization Interface Specification | 12    |

| Table 7-20. 05 12kHz Synchronization interface Specification                                                                  | 73    |

| Table 7-21. Composite Clock Variations                                                                                        |       |

| Table 7-22. GR-370 Composite Clock Interfaces Specification                                                                   | 70    |

| Table 7-23. G.703 Synchronization Interfaces Specification                                                                    | 70    |

| Table 8-1. Top-Level Memory Map                                                                                               |       |

|                                                                                                                               |       |

| Table 8-2. Core Register Map                                                                                                  |       |

| Table 8-3. BITS Transceiver Register Map                                                                                      |       |

| Table 9-1. JTAG Instruction Codes                                                                                             |       |

| Table 9-2. JTAG ID Code                                                                                                       | . 202 |

| Table 10-1. Recommended DC Operating Conditions                                                                               |       |

| Table 10-2. DC Characteristics                                                                                                |       |

| Table 10-3. CMOS/TTL Pins                                                                                                     |       |

| Table 10-4. LVDS Pins                                                                                                         |       |

|                                                                                                                               | . 205 |

|                                                                                                                               | . 206 |

| Table 10-7. Recommended External Components for Output Clock OC8                                                              |       |

| Table 10-8. Input Clock Timing                                                                                                |       |

| Table 10-9. Input Clock to Output Clock Delay                                                                                 | . 207 |

| Table 10-10. Output Clock Phase Alignment, Frame Sync Alignment Mode                                                          |       |

| Table 10-11. BITS Receiver Timing                                                                                             |       |

| Table 10-12. BITS Transmitter Timing                                                                                          |       |

| Table 10-13. Parallel Interface Timing                                                                                        |       |

| Table 10-14. SPI Interface Timing                                                                                             |       |

| Table 10-15. JTAG Interface Timing                                                                                            |       |

| Table 11-1. Pin Assignments Sorted by Signal Name                                                                             |       |

| Table 13-1. Thermal Properties, Natural Convection                                                                            | . 222 |

## 1. STANDARDS COMPLIANCE

## Table 1-1. Applicable Telecom Standards

| SPECIFICATION  | SPECIFICATION TITLE                                                                              |

|----------------|--------------------------------------------------------------------------------------------------|

| ANSI           |                                                                                                  |

| T1.101         | Synchronization Interface Standard, 1999                                                         |

| T1.102         | Digital Hierarchy—Electrical Interfaces, 1993                                                    |

| T1.107         | Digital Hierarchy—Formats Specification, 1995                                                    |

| T1.231.02      | Digital Hierarchy—Layer 1 In-Service Digital Transmission Performance Monitoring, 2003           |

| T1.403         | Network and Customer Installation Interfaces—DS1 Electrical Interface, 1999                      |

| TIA/EIA-644-A  | Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits, 2001 |

| AT&T           |                                                                                                  |

| TR62411        | ACCUNET® T1.5 Service Description and Interface Specification (12/1990)                          |

| ETSI           |                                                                                                  |

|                | Transmission and Multiplexing (TM); Generic Requirements of Transport Functionality of           |

| EN 300 417-6-1 | Equipment; Part 6-1: Synchronization Layer Functions, v1.1.3 (1999-05)                           |

| EN 200 400 0 4 | Transmission and Multiplexing (TM); Generic Requirements for Synchronization Networks;           |

| EN 300 462-3-1 | Part 3-1: The Control of Jitter and Wander within Synchronization Networks, v1.1.1 (1998-05)     |

|                | Transmission and Multiplexing (TM); Generic Requirements for Synchronization Networks;           |

| EN 300 462-5-1 | Part 5-1: Timing Characteristics of Slave Clocks Suitable for Operation in Synchronous Digital   |

|                | Hierarchy (SDH) Equipment, v1.1.1 (1998-05)                                                      |

| IEEE           |                                                                                                  |

| IEEE 1149.1    | Standard Test Access Port and Boundary-Scan Architecture, 1990                                   |

| IEEE 1596.3    | Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interface (SCI), 1996              |

| ITU-T          |                                                                                                  |

| G.703          | Physical/Electrical Characteristics of Hierarchical Digital Interfaces (11/2001)                 |

| G.704          | Synchronous Frame Structures Used at 1544, 6312, 2048, 8448 and 44736 kbit/s                     |

| G.704          | Hierarchical Levels (10/1998)                                                                    |

| G.706          | Frame Alignment and Cyclic Redundancy Check (CRC) Procedures Relating to Basic Frame             |

| 0.700          | Structures Defined in Recommendation G.704 (1991)                                                |

| G.775          | Loss of Signal (LOS) and Alarm Indication Signal (AIS) and Remote Defect Indication (RD)         |

|                | Defect Detection and Clearance Criteria for PDH Signals (10/1998)                                |

| G.781          | Synchronization Layer Functions (06/1999)                                                        |

| G.783          | ITU G.783 Characteristics of Synchronous Digital Hierarchy (SDH) Equipment Functional            |

| 0.700          | Blocks (10/2000 plus Amendment 1 06/2002 and Corrigendum 2 03/2003)                              |

| G.812          | Timing Requirements of Slave Clocks Suitable for Use as Node Clocks in Synchronization           |

|                | Networks (06/1998)                                                                               |

| G.813          | Timing characteristics of SDH equipment slave clocks (SEC) (03/2003)                             |

| G.823          | The Control of Jitter and Wander within Digital Networks which are Based on the 2048kbps         |

| 0.020          | Hierarchy (03/2000)                                                                              |

| G.824          | The Control of Jitter and Wander within Digital Networks which are Based on the 1544kbps         |

| 0.021          | Hierarchy (03/2000)                                                                              |

| G.825          | The Control of Jitter and Wander within Digital Networks which are Based on the                  |

|                | Synchronous Digital Hierarchy (SDH) (03/2000)                                                    |

| O.162          | Equipment to Perform In-Service Monitoring on 2048, 8448, 34,368 and 139,264 kbit/s              |

|                | Signals (10/1992)                                                                                |

| TELCORDIA      |                                                                                                  |

| GR-253-CORE    | SONET Transport Systems: Common Generic Criteria, Issue 3, September 2000                        |

| GR-378-CORE    | Generic Requirements for Timing Signal Generators, Issue 2, February 1999                        |

| GR-499-CORE    | <i>Transport Systems Generic Requirements (TSGR) Common Requirements,</i> Issue 2, December 1998 |

| GR-1244-CORE   | Clocks for the Synchronized Network: Common Generic Criteria, Issue 2, December 2000             |

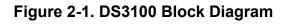

## 2. BLOCK DIAGRAM

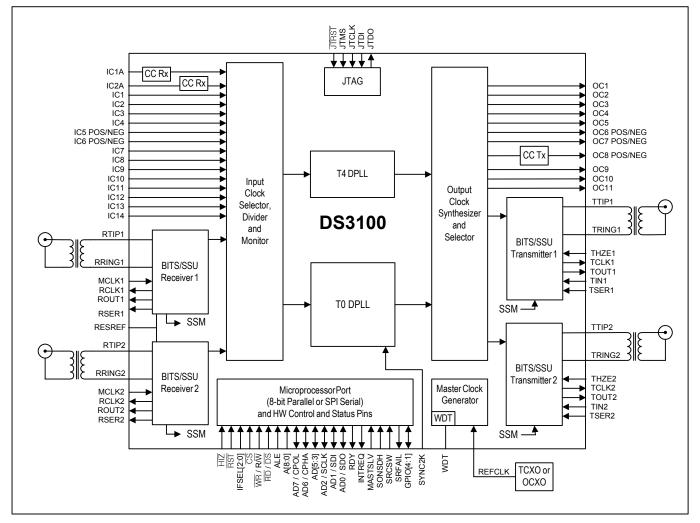

## 3. APPLICATION EXAMPLE

## 4. DETAILED DESCRIPTION

Figure 2-1 illustrates the blocks described in this section and how they relate to one another. Section 5 provides a detailed feature list.

The DS3100 is a complete timing card IC for systems with SONET/SDH ports. At the core of this device are two digital phase-locked loops (DPLLs) labeled T0 and T4<sup>1</sup>. DPLL technology makes uses of digital-signal processing (DSP) and digital-frequency synthesis (DFS) techniques to implement PLLs that are precise, flexible, and have consistent performance over voltage, temperature, and manufacturing process variations. The DS3100's DPLLs are digitally configurable for input and output frequencies, loop bandwidth, damping factor, pull-in/hold-in range, and a variety of other factors. Both DPLLs can directly lock to many common telecom frequencies and also can lock at 8kHz to any multiple of 8kHz up to 155.52MHz. The DPLLs can also tolerate and filter significant amounts of jitter and wander.

The T0 DPLL is responsible for generating the system clocks used to time the outgoing traffic interfaces of the system (SONET/SDH, synchronous Ethernet, etc.). To perform this role in a variety of systems with diverse performance requirements, the T0 DPLL has a sophisticated feature set and is highly configurable. T0 can automatically transition among free-run, locked and holdover states all without software intervention. In free-run, TO generates a stable, low-noise clock with the same frequency accuracy as the external oscillator connected to the REFCLK pin. With software calibration the DS3100 can even improve the accuracy to within ±0.02 ppm. When an input reference has been validated. T0 transitions to the locked state in which its output clock accuracy is equal to the accuracy of the input reference. While in the locked state, T0 acquires a high-accuracy (3.85 x10<sup>-11</sup>) long-term average frequency value to use as the holdover frequency. When its selected reference fails, T0 can very quickly detect the failure and enter the holdover state to avoid affecting its output clock. From holdover it can automatically switch to the next highest priority input reference, again without affecting its output clock (hitless switching). Switching among input references can be either revertive or nonrevertive. When all input references are lost, T0 stays in holdover in which it generates a stable low-noise clock with initial frequency accuracy equal to its stored holdover value and drift performance determined by the quality of the external oscillator. With a suitable local oscillator the T0 DPLL provides holdover performance suitable for all applications up to and including Stratum 3E. T0 can also perform phase build-outs and fine-granularity output clock phase adjustments.

The T4 DPLL has a much less demanding role to play and therefore is much simpler than T0. Often T4 is used as a frequency converter to create a derived DS1- or E1-rate clock (frequency locked to an incoming SONET/SDH port) to be sent to a nearby BITS Timing Signal Generator (TSG, Telcordia terminology) or Synchronization Supply Unit (SSU, ITU-T terminology). In other cases T4 is phase-locked to T0 and used as a frequency converter to produce additional output clock rates for use within the system, such as NxDS1, NxE1, NxDS2, DS3, E3, or 125MHz for synchronous Ethernet. T4 can also be configured as a measuring tool to measure the frequency of an input reference or the phase difference between two input references.

At the front end of both the T0 and T4 DPLLs is the Input Clock Selector, Divider, and Monitor (ICSDM) block. This block continuously monitors as many as 14 different input clocks of various frequencies for activity and frequency accuracy. In addition, ICSDM maintains separate input clock priority tables for the T0 and T4 DPLLs and can automatically select and provide the highest priority valid clock to each DPLL without any software intervention. The ICSDM block can also divide the selected clock down to 8kHz if required by the DPLL.

In addition to digital clock signals from system line cards, the DS3100 can also directly receive up to two 64kHz composite clock signals on its IC1A and IC2A pins and up to two DS1, E1, 2048kHz, or 6312kHz synchronization signals using its BITS receivers. These signals typically come from a nearby BITS Timing Signal Generator or SSU to provide external timing to the system. The BITS receivers are full-featured LIU receivers and framers capable of recovering clock and data from both short-haul and long-haul signals, finding DS1/E1 frame, extracting incoming SSM messages, and reporting both SSMs and performance defects (LOS, OOF, AIS, RAI) to system software. The recovered clock from each BITS receiver can be connected to any of the 14 input clocks of the ICSDM block for monitoring, optional dividing, and selection as the reference for either of the DPLLs. The BITS receivers are tightly coupled to the ICSDM block, and the DS3100 can be configured to automatically disqualify input clocks from BITS receivers are detected. The analog front-ends of the BITS receivers are state-

<sup>&</sup>lt;sup>1</sup> These names are adapted from output ports of the SETS function specified in ITU and ETSI standards such as ETSI EN 300 462-2-1.

of-the-art LIU receivers with software-selectable termination and high-impedance inputs to support redundant timing cards without relays in the signal path.

The Output Clock Synthesizer and Selector (OCSS) block shown in Figure 2-1 contains the T0 output APLL, the T4 output APLL, clock divider logic, and additional output DFS blocks. The T0 and T4 APLLs multiply the clock rates from the DPLLs by four and simulataneously attenuate jitter. Using the different settings of the T0 and T4 DPLLs and the output divider logic, the DS3100 can produce more than 60 different output frequencies including common SONET/SDH, PDH and synchronous Ethernet rates plus 2kHz and 8kHz frame pulses.

In addition to creating digital clock signals for use within the system, the DS3100 can also directly transmit one composite clock signal on its OC8 pin and up to two DS1, E1, or 2048kHz synchronization signals using its BITS transmitters. These signals typically convey the recovered timing from one SONET/SDH port to a nearby BITS timing-signal generator or SSU which in turn distributes timing to the whole central office. The BITS transmitters are full-featured frame formatters and LIU transmitters capable of generating DS1/E1 frames, inserting incoming SSM messages, and driving both short-haul and long-haul signals. Any of the output clock signals can be connected to either of the BITS transmitters for use as the transmission clock. The analog front-ends of the BITS transmitters are state-of-the-art LIU transmitters with software-selectable termination and high-impedance outputs to support redundant timing cards without relays in the signal path.

The entire chip is clocked from the external oscillator connected to the REFCLK pin. Thus the free-run and holdover stability of the DS3100-based timing card is entirely a function of the stability of the external oscillator, the performance of which can be selected to match the application: TCXO, OCXO, double-oven OCXO, etc. The 12.8MHz clock from the external oscillator is multiplied by sixteen by the Master Clock Generator block to create the 204.8MHz master clock used by the rest of the device. Since every block on the device depends on the master clock and therefore the local oscillator clock for proper operation, the master clock generator has a watchdog timer (WDT) function that can be used to signal a local microprocessor in the event of a local oscillator clock failure.

The DS3100 also has several features to support master/slave timing card redundancy and protection. Two DS3100 devices on redundant cards can be configured to maintain the same priority tables, choose the same input references, and generate output clocks and frame syncs with the same frequency and phase.

## 5. DETAILED FEATURES

### 5.1 T0 DPLL Features

- High-resolution DPLL plus low-jitter output APLL

- Sophisticated state machine automatically transitions between free-run, locked, and holdover states

- Revertive or nonrevertive reference selection algorithm

- Programmable bandwidth in 18 steps from 0.5MHz to 70Hz

- Separately configurable acquisition bandwidth and locked bandwidth

- Programmable damping factor to balance lock time with peaking: 1.2, 2.5, 5, 10, or 20

- Multiple phase detectors: phase/frequency, early/late, and multicycle

- Phase/frequency locking (±360° capture) or nearest-edge phase locking (±180° capture)

- Multi-cycle phase detection and locking (up to ±8191UI) improves jitter tolerance and lock time

- Phase build-out in response to input phase transients (1 to 3.5µs)

- Phase build-out in response to reference switching

- Less than 5ns output clock phase transient during phase build-out

- Output phase adjustment up to ±200ns in 6ps steps with respect to selected input reference

- High-resolution frequency and phase measurement

- Holdover frequency averaging with 8- or 110-minute intervals

- APLL frequency options suitable for N x 19.44MHz, N x DS1, and N x E1

- Low-jitter frame sync (8kHz) and multiframe sync (2kHz) outputs on OC10 and OC11

- 2kHz and 8kHz clocks available on OC1 through OC7 with programmable polarity and pulse width

## 5.2 T4 DPLL Features

- High-resolution DPLL plus low-jitter output APLL

- Programmable bandwidth: 18Hz, 35Hz, or 70Hz

- Programmable damping factor to balance lock time with peaking: 1.2, 2.5, 5, 10, or 20

- Multiple phase detectors: phase/frequency, early/late, and multicycle

- Phase/frequency locking (±360° capture) or nearest-edge phase locking (±180° capture)

- Multi-cycle phase detection and locking (up to ±8191UI) improves jitter tolerance and lock time

- APLL frequency options suitable for N x 19.44MHz, N x DS1, N x E1, DS3, E3, 6312kHz, and N x 62.5MHz (for Gigabit Ethernet)

- 2kHz and 8kHz clocks available on OC1 through OC7 with programmable polarity and pulse width

- Can operate independently or locked to T0 DPLL

- Phase detector can be used to measure phase difference between two input clocks

### 5.3 Input Clock Features

- 14 input clocks

- 10 programmable-frequency CMOS/TTL input clocks accept any multiple of 8kHz up to 125MHz

- Two LVDS/LVPECL/CMOS/TTL input clocks accept any multiple of 8kHz up to 125MHz plus 155.52MHz

- Two 64kHz composite clock receivers (AMI format) that can also be configured as programmable-frequency CMOS/TTL input clocks if needed

- All 14 input clocks are constantly monitored by programmable frequency monitors and activity monitors

- Fast activity monitor can disqualify the selected reference after two missing clock cycles

- Separate 2/4/8kHz sync input

## 5.4 Output Clock Features

- 11 output clocks

- Five programmable-frequency CMOS/TTL output clocks drive any internally produced clock up 77.76MHz

- Two programmable-frequency LVDS output clocks drive any internally produced clock up to 311.04MHz

- Two sync pulses, 2kHz and 8kHz, can be disciplined by a 2kHz or 8kHz sync input

- One 1.544MHz/2.048MHz output clock

- One 64kHz composite clock output (AMI format)

- Output clock rates include 2kHz, 8kHz, NxDS1, NxDS2, DS3, NxE1, E3, 19.44MHz, 38.88MHz, 51.84MHz, 62.5MHz, 77.76MHz, 125.0MHz, 155.52MHz, and 311.04MHz

- Outputs at even divisors of 311.04MHz have less than 0.5ns peak-to-peak output jitter

## 5.5 Redundancy Features

- Devices on redundant timing cards can be configured for master/slave operation

- Clocks and frame syncs can be cross-wired between devices to ensure that slave always tracks master

- Master/slave mode pin can auto-configure slave to track master with no phase build-out and wider bandwidth

- Input clock priority tables can easily be kept synchronized between master and slave

- BITS transceivers have high-impedance receive inputs and transmit outputs for redundancy without relays

### 5.6 BITS Transceiver Features

#### 5.6.1 General

- Two independent transceivers with fully independent transmitter and receiver

- DS1 synchronization interface in SF or ESF format

- E1 synchronization interface with FAS, CAS, and/or CRC-4 framing

- J1 support (DS1 with Japanese CRC-6 and RAI)

- 2048kHz synchronization interface (G.703)

- 6312kHz Japanese synchronization interface (G.703 Appendix II)

- Short-haul and long-haul line interface unit

- Internal software-selectable termination (75Ω, 100Ω, 110Ω, or 120Ω) or external termination

- High-impedance receive inputs and transmit outputs for relay-less master/slave redundancy

- Local and remote loopbacks

#### 5.6.2 Receiver

- Each receiver can be connected to any of fourteen input clocks

- Automatic receive sensitivity adjustment

- DS1 receive sensitivity configurable for 0 to -36dB (long haul) or 0 to -15dB (short haul)

- E1 receive sensitivity configurable for 0 to -43dB (long haul) or 0 to -12dB (short haul)

- Receive signal level indication in 2.5dB steps from -2.5dB to -34dB (DS1) and -2.5dB to -43dB (E1)

- Monitor-mode gain settings of 14dB, 20dB, 26dB, and 32dB

- LOS, OOF, RAI, and AIS status

- Extraction and validation of SSM messages from DS1 ESF data link or E1 Sa bits

- Receiver data output pin (RSER) for access to DS1/E1 payload

- Optional receiver clock and frame sync output pins (RCLK and ROUT) for special applications

- Receiver power-down control

- Short-circuit detection

#### 5.6.3 Transmitter

- Each transmitter can be connected to any of eight output clocks

- Transmitter data input pin (TSER) for access to DS1/E1 payload

- Optional transmitter clock pins (TIN, TCLK, TOUT) for special applications

- Insertion of SSM messages into DS1 ESF data link or E1 Sa bits

- Flexible transmit waveform generation

- DSX-1 line build-outs

- E1 waveforms include G.703 waveshapes for both 75Ω coax and 120Ω twisted pair cables

- AIS and alternating ones and zeros generation

- Transmitter power-down control

- Short-circuit detection/limit

- Open-circuit detection

## 5.7 Composite Clock I/O Features

- Two composite clock receivers and one composite clock transmitter (all AMI format)

- Compliant with Telcordia GR-378 composite clock, G.703 centralized clock, and G.703 Appendix II.1 Japanese synchronization interfaces

- Configurable for 50% or 5/8 duty cycle, 1V or 3V pulse amplitude, and  $110\Omega/120\Omega/133\Omega$  termination

- Received signals are monitored for LOS, AMI violations, presence/absence of the 8 kHz component, and presence/absence of the 400Hz component (for G.703 Appendix II.1 option b)

- Transmitter can generate or suppress the 8kHz component and/or the 400 Hz component (for G.703 Appendix II.1 option b)

- Composite clock receiver inputs can be configured as programmable-frequency CMOS/TTL inputs if composite clock support is not needed

## 5.8 General Features

- Operates from a single external 12.800MHz local oscillator (TCXO or OCXO)

- On-chip local oscillator watchdog circuit

- Microprocessor interface can be 8-bit parallel (Intel or Motorola, multiplexed or nonmultiplexed) or SPI serial

- Register set can be write-protected

## 6. **PIN DESCRIPTIONS**

| PIN | NAME <sup>(1)</sup> | TYPE <sup>(2)</sup>               | FUNCTION                                                                                                                                   |

|-----|---------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| H1  | REFCLK              | I                                 | <b>Reference Clock.</b> Connect to a 12.800MHz, high-accuracy, high-stability, low-noise local oscillator (TCXO or OCXO). See Section 7.3. |

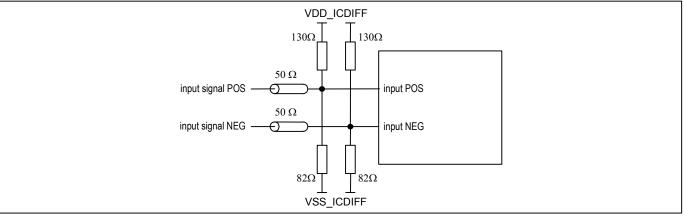

| P6  | IC1A                | I                                 | <b>Input Clock 1 AMI.</b> AMI 64kHz composite clock. Enabled when MCR5:IC1SF = 0.<br>See Section 7.11.1, Table 10-6, and Figure 10-3.      |

| A10 | IC1                 | I <sub>PD</sub>                   | <b>Input Clock 1.</b> CMOS/TTL. Programmable frequency (default 8kHz). Enabled when MCR5:IC1SF = 1. See Section 7.11.1.                    |

| P7  | IC2A                | I                                 | <b>Input Clock 2 AMI.</b> AMI 64kHz composite clock. Enabled when MCR5:IC2SF = 0.<br>See Section 7.11.1, Table 10-6, and Figure 10-3.      |

| B10 | IC2                 | I <sub>PD</sub>                   | <b>Input Clock 2.</b> CMOS/TTL. Programmable frequency (default 8kHz). Enabled when MCR5:IC2SF = 1. See Section 7.11.1.                    |

| C10 | IC3                 | I <sub>PD</sub>                   | Input Clock 3. CMOS/TTL. Programmable frequency (default 8kHz).                                                                            |

| A11 | IC4                 | I <sub>PD</sub>                   | Input Clock 4. CMOS/TTL. Programmable frequency (default 8kHz).                                                                            |

| B5  | IC5POS              | - I <sub>A</sub> , I <sub>A</sub> | Input Clock 5. LVDS/LVPECL. Programmable frequency (default 19.44MHz LVDS). LVDS: See Table 10-4 and Figure 10-1.                          |

| A5  | IC5NEG              | ΙΑ, ΙΑ                            | LVPECL: See Table 10-5 and Figure 10-2.                                                                                                    |

| B4  | IC6POS              | 1. 1.                             | Input Clock 6. LVDS/LVPECL. Programmable frequency (default 19.44MHz LVPECL).                                                              |

| A4  | IC6NEG              | I <sub>A</sub> , I <sub>A</sub>   | LVDS: See Table 10-4 and Figure 10-1.<br>LVPECL: See Table 10-5 and Figure 10-2.                                                           |

| B11 | IC7                 | I <sub>PD</sub>                   | Input Clock 7. CMOS/TTL. Programmable frequency (default 19.44MHz).                                                                        |

| C11 | IC8                 | I <sub>PD</sub>                   | Input Clock 8. CMOS/TTL. Programmable frequency (default 19.44MHz).                                                                        |

| A12 | IC9                 | I <sub>PD</sub>                   | Input Clock 9. CMOS/TTL. Programmable frequency (default 19.44MHz).                                                                        |

| B12 | IC10                | I <sub>PD</sub>                   | Input Clock 10. CMOS/TTL. Programmable frequency (default 19.44MHz).                                                                       |

| A13 | IC11                | I <sub>PD</sub>                   | <b>Input Clock 11.</b> CMOS/TTL. Programmable frequency (default 19.44MHz in master mode, 6.48MHz in slave mode).                          |

| C12 | IC12                | I <sub>PD</sub>                   | Input Clock 12. CMOS/TTL. Programmable frequency (default 1.544/2.048MHz).                                                                 |

| B13 | IC13                | I <sub>PD</sub>                   | Input Clock 13. CMOS/TTL. Programmable frequency (default 1.544/2.048MHz).                                                                 |

| A14 | IC14                | I <sub>PD</sub>                   | Input Clock 14. CMOS/TTL. Programmable frequency (default 1.544/2.048MHz).                                                                 |

| B14 | SYNC2K              | I <sub>PD</sub>                   | Frame Sync Input. 2kHz, 4kHz, or 8kHz.                                                                                                     |

| PIN | NAME <sup>(1)</sup> | TYPE <sup>(2)</sup> | FUNCTION                                                                        |

|-----|---------------------|---------------------|---------------------------------------------------------------------------------|

| C6  | OC1                 | O <sub>3</sub>      | Output Clock 1. CMOS/TTL. Programmable frequency (default 6.48MHz).             |

| A7  | OC2                 | O <sub>3</sub>      | Output Clock 2. CMOS/TTL. Programmable frequency (default 38.88MHz).            |

| B7  | OC3                 | O <sub>3</sub>      | Output Clock 3. CMOS/TTL. Programmable frequency (default 19.44MHz).            |

| C7  | OC4                 | O <sub>3</sub>      | Output Clock 4. CMOS/TTL. Programmable frequency (default 38.88MHz).            |

| A8  | OC5                 | O <sub>3</sub>      | Output Clock 5. CMOS/TTL. Programmable frequency (default 77.76MHz).            |

| B3  | OC6POS              | - O <sub>3</sub>    | Output Clock 6. LVDS. Programmable frequency (default 38.88MHz LVDS).           |

| A3  | OC6NEG              |                     | See Table 10-4 and Figure 10-1.                                                 |

| C2  | OC7POS              | 0                   | Output Clock 7. LVDS. Programmable frequency (default 19.44MHz LVDS).           |

| C1  | OC7NEG              | O <sub>3</sub>      | See Table 10-4 and Figure 10-1.                                                 |

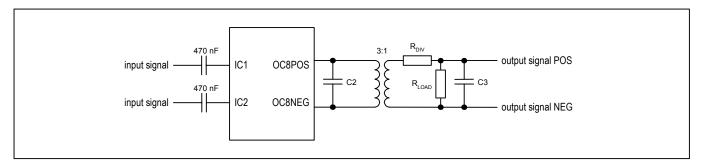

| C8  | OC8POS              | 0                   | Output Clock 8. AMI. 64kHz composite clock. See Section 7.11.2, Table 10-6, and |

| B8  | OC8NEG              | O <sub>3</sub>      | Figure 10-3.                                                                    |

| A9  | OC9                 | O <sub>3</sub>      | Output Clock 9. CMOS/TTL. 1.544/2.048MHz.                                       |

| B9  | OC10                | O <sub>3</sub>      | Output Clock 10. CMOS/TTL. 8kHz frame sync or clock.                            |

| C9  | OC11                | O <sub>3</sub>      | Output Clock 11. CMOS/TTL. 2kHz multiframe sync or clock.                       |

## Table 6-2. Output Clock Pin Descriptions

## Table 6-3. BITS Receiver Pin Descriptions

| PIN | NAME <sup>(1)</sup> | TYPE <sup>(2)</sup> | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|---------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F2  | MCLK1               | IPD                 | <b>Master Clock for BITS Transceiver 1.</b> In most applications, the device's 204.8MHz master clock (see Section 7.3) is divided by 100 to get the BITS transceiver master clock. For special applications, BCCR3:MCLKS can be set to 1 to source the master clock for BITS transceiver 1 from the MCLK1 pin. The clock applied to MCLK1 can be 1X, 2X, 4X or 8X 2.048MHz for any BITS transceiver mode. For DS1 mode only, MCLK1 can be 1X, 2X, 4X, or 8X 1.544MHz. When BCCR3:MCLKS = 0, the MCLK1 pin is ignored and should be wired high or low. See Section 7.10.1. |

| T10 | MCLK2               | I <sub>PD</sub>     | <b>Master Clock for BITS Transceiver 2.</b> In most applications, the device's 204.8MHz master clock (see Section 7.3) is divided by 100 to get the BITS transceiver master clock. For special applications, BCCR3:MCLKS can be set to 1 to source the master clock for BITS transceiver 2 from the MCLK2 pin. The clock applied to MCLK2 can be 1X, 2X, 4X or 8X 2.048MHz for any BITS transceiver mode. For DS1 mode only, MCLK1 can be 1X, 2X, 4X or 8X 1.544MHz. When BCCR3:MCLKS = 0, the MCLK2 pin is ignored and should be wired high or low. See Section 7.10.1.  |

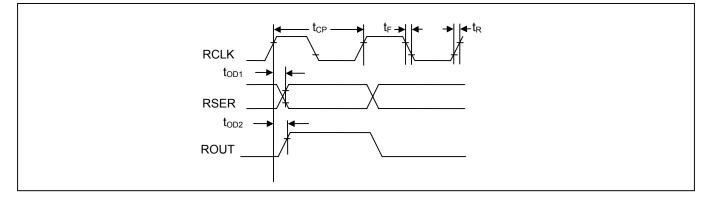

| K1  | RCLK1               | O <sub>3</sub>      | <b>Receiver Clock Output for BITS Transceiver 1.</b> This pin presents the recovered clock from BITS receiver 1. This output is enabled/disabled by BCCR3:RCEN. When this pin is disabled, the recovered clock can still be forwarded to one of input clocks IC1 to IC14, as specified by BCCR2:RCLKD. When disabled, RCLK1 can function as a general-purpose output whose value is controlled by BCCR3:RCINV. See Section 7.10.2.                                                                                                                                        |

| R10 | RCLK2               | O <sub>3</sub>      | <b>Receiver Clock Output for BITS Transceiver 2.</b> This pin presents the recovered clock from BITS receiver 2. This output is enabled/disabled by BCCR3:RCEN. When this pin is disabled, the recovered clock can still be forwarded to one of input clocks IC1 to IC14, as specified by BCCR2:RCLKD. When disabled, RCLK2 can function as a general-purpose output whose value is controlled by BCCR3:RCINV. See Section 7.10.2.                                                                                                                                        |

| K2  | ROUT1               | O <sub>3</sub>      | <b>Receiver Multipurpose Output Pin for BITS Transceiver 1.</b> This output is<br>enabled/disabled by BCCR3:ROEN. Its signal source is specified by BCCR3:ROUTS.<br>Possible sources are the DS1/E1 frame sync and the DS1/E1 multiframe sync. When<br>disabled, ROUT1 can function as a general-purpose output whose value is controlled<br>by BCCR3:ROINV. See Section 7.10.2.                                                                                                                                                                                          |

| P10 | ROUT2               | O <sub>3</sub>      | <b>Receiver Multipurpose Output Pin for BITS Transceiver 2.</b> This output is<br>enabled/disabled by BCCR3:ROEN. Its signal source is specified by BCCR3:ROUTS.<br>Possible sources are the DS1/E1 frame sync and the DS1/E1 multiframe sync. When<br>disabled, ROUT2 can function as a general-purpose output whose value is controlled<br>by BCCR3:ROINV. See Section 7.10.2.                                                                                                                                                                                          |

| J3  | RSER1               | O <sub>3</sub>      | <b>Receiver Serial Data Output for BITS Transceiver 1.</b> When BITS receiver 1 is in DS1 or E1 mode (i.e., when BMCR:RMODE = 0x), this pin presents the received DS1/E1 data stream in NRZ format. RSER1 is updated on the RCLK1 edge specified by BCCR3:RCINV. RSER1 is enabled/disabled by the BCCR3:RSEN control bit. This pin is disabled (low) in other BITS receiver modes. See Sections 7.10.5.1 and 7.10.6.1.                                                                                                                                                    |

| T11 | RSER2               | O <sub>3</sub>      | <b>Receiver Serial Data Output for BITS Transceiver 2.</b> When BITS receiver 2 is in DS1 or E1 mode (i.e., when BMCR:RMODE = 0x), this pin presents the received DS1/E1 data stream in NRZ format. RSER2 is updated on the RCLK2 edge specified by BCCR3:RCINV. RSER2 is enabled/disabled by the BCCR3:RSEN control bit. This pin is disabled (low) in other BITS receiver modes. See Sections 7.10.5.1 and 7.10.6.1.                                                                                                                                                    |

| Т5  | RTIP1               | I.                  | <b>Differential Receiver Inputs for BITS Transceiver 1.</b> These pins connect to the receive cable through a 1:1 transformer. These pins are high impedance when the                                                                                                                                                                                                                                                                                                                                                                                                     |

| R5  | RRING1              | – I <sub>A</sub>    | receiver is powered down (BLCR4:RPD = 1). See Section 7.10.4 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| L16 | RTIP2               |                     | <b>Differential Receiver Inputs for BITS Transceiver 2.</b> These pins connect to the receive cable through a 1:1 transformer. These pins are high impedance when the                                                                                                                                                                                                                                                                                                                                                                                                     |

| L15 | RRING2              |                     | receive cable through a 1:1 transformer. These pins are high impedance when the receiver is powered down (BLCR4:RPD = 1). See Section 7.10.4 for details.                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Table 6-4. BITS Transmitter Pin Descriptions

| PIN         | NAME <sup>(1)</sup> | TYPE <sup>(2)</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

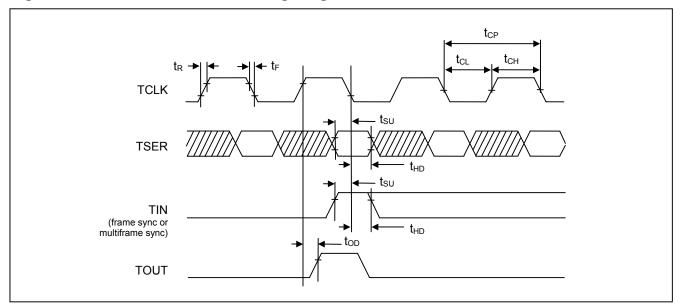

| L2          | TCLK1               | O <sub>3</sub>      | <b>Transmit Clock Output for BITS Transceiver 1.</b> This pin presents the TCLK signal output from the Tx Clock Mux block. This output is enabled/disabled by BCCR4:TCEN. The TSER1 pin is sampled on the TCLK1 edge specified by BCCR4:TCINV. See Section 7.10.3.                                                                                                                                                                                                                                                           |

| T12         | TCLK2               | O <sub>3</sub>      | <b>Transmit Clock Output for BITS Transceiver 2.</b> This pin presents the TCLK signal output from the Tx Clock Mux block. This output is enabled/disabled by BCCR4:TCEN. The TSER2 pin is sampled on the TCLK2 edge specified by BCCR4:TCINV. See Section 7.10.3.                                                                                                                                                                                                                                                           |

| M1          | TOUT1               | O <sub>3</sub>      | <b>Transmit Multipurpose Output Pin for BITS Transceiver 1.</b> This output is enabled/disabled by BCCR4:TOEN. Its signal source is specified by BCCR4:TOUTS. Possible sources are the DS1/E1 frame sync and the DS1/E1 multiframe sync. See Section 7.10.3.                                                                                                                                                                                                                                                                 |

| P11         | TOUT2               | O <sub>3</sub>      | <b>Transmit Multipurpose Output Pin for BITS Transceiver 2.</b> This output is enabled/disabled by BCCR4:TOEN. Its signal source is specified by BCCR4:TOUTS. Possible sources are the DS1/E1 frame sync and the DS1/E1 multiframe sync. See Section 7.10.3.                                                                                                                                                                                                                                                                 |

| L1          | TIN1                | I <sub>PD</sub>     | <b>Transmitter Multipurpose Input for BITS Transceiver 1.</b> In most applications, the BITS transmitter clock is sourced from one of output clocks OC1–OC7 or OC9, as specified by BCCR1:TCLKS. For special applications, TCLKS can be set to 0000 to the enable the transmitter clock to be sourced from the TIN1 pin. Optionally TIN1 can source the frame or multiframe sync in DS1 and E1 modes. In these latter cases, TIN1 is sampled on the TCLK1 edge specified by BCCR4:TCINV. See Section 7.10.3.                 |

| R12         | TIN2                | IPD                 | <b>Transmitter Multipurpose Input for BITS Transceiver 2.</b> In most applications, the BITS transmitter clock is sourced from one of output clocks OC1-OC7 or OC9, as specified by BCCR1:TCLKS. For special applications, TCLKS can be set to 0000 to the enable the transmitter clock to be sourced from the TIN2 pin. Optionally TIN2 can source the frame or multiframe sync in DS1 and E1 modes. In these latter cases, TIN2 is sampled on the TCLK2 edge specified by BCCR4:TCINV. See Section 7.10.3.                 |

| L3          | TSER1               | I <sub>PU</sub>     | <b>Transmitter Serial Data Input for BITS Transceiver 1.</b> When the BITS transmitter is in DS1 or E1 mode (i.e., when BMCR:TMODE = 0x), this pin is the source for the DS1/E1 data stream in NRZ format. TSER1 is sampled on the TCLK1 edge specified by BCCR4:TCINV. Payload bits and optionally some overhead bits are sampled. Normally, this pin is wired high to achieve an all-ones payload. This pin is ignored in other BITS transmitter modes and should be held high or low. See Sections 7.10.5.2 and 7.10.6.2. |

| T13         | TSER2               | IPU                 | <b>Transmitter Serial Data Input for BITS Transceiver 2.</b> When the BITS transmitter is in DS1 or E1 mode (i.e., when BMCR:TMODE = 0x), this pin is the source for the DS1/E1 data stream in NRZ format. TSER2 is sampled on the TCLK2 edge specified by BCCR4:TCINV. Payload bits and optionally some overhead bits are sampled. Normally, this pin is wired high to achieve an all-ones payload. This pin is ignored in other BITS transmitter modes and should be held high or low. See Sections 7.10.5.2 and 7.10.6.2. |

| R3,<br>T3   | TTIP1               |                     | <b>Differential Transmitter Outputs for BITS Transceiver 1.</b> These pins drive the outgoing signal onto the transmit cable through a 1:2 step-up transformer. They can be placed in a                                                                                                                                                                                                                                                                                                                                      |

| R2,<br>T2   | TRING1              | ΟΑ                  | high-impedance state by pulling the THZE1 pin high or setting BLCR4:TE = 0 in BITS transceiver 1. These pins are also high impedance when the transmitter is powered down (BLCR4:TPD = 1). See Section 7.10.4.                                                                                                                                                                                                                                                                                                               |

| N15,<br>N16 | TTIP2               | OA                  | <b>Differential Transmitter Outputs for BITS Transceiver 2.</b> These pins drive the outgoing signal onto the transmit cable through a 1:2 step-up transformer. They can be placed in a                                                                                                                                                                                                                                                                                                                                      |

| P15,<br>P16 | TRING2              |                     | high-impedance state by pulling the THZE2 pin high or setting BLCR4:TE = 0 in BITS transceiver 2. These pins are also high impedance when the transmitter is powered down (BLCR4:TPD = 1). See Section 7.10.4.                                                                                                                                                                                                                                                                                                               |

| КЗ          | THZE1               | I <sub>PU</sub>     | <b>Transmit High-Impedance Enable for BITS Transceiver 1.</b> See Section 7.10.4.2.3.<br>0 = TTIP1/TRING1 transmit data normally (must also have BLCR4:TE = 1 in BITS transceiver 1)<br>1 = TTIP1/TRING1 high impedance                                                                                                                                                                                                                                                                                                      |

| T14         | THZE2               | I <sub>PU</sub>     | <b>Transmit High-Impedance Enable for BITS Transceiver 2.</b> See Section 7.10.4.2.3.<br>0 = TTIP2/TRING2 transmit data normally (must also have BLCR4:TE = 1 in BITS transceiver 2)<br>1 = TTIP2/TRING2 high impedance                                                                                                                                                                                                                                                                                                      |

| PIN | NAME <sup>(1)</sup> | TYPE <sup>(2)</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                           |  |

|-----|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B6  | RST                 | I <sub>PU</sub>     | Active-Low Reset. When this global asynchronous reset is pulled low, all internal circuitry is reset to default values. The device is held in reset as long as $\overrightarrow{\text{RST}}$ is low. $\overrightarrow{\text{RST}}$ should be held low for at least two REFCLK cycles.                                              |  |

| R14 | HIZ                 | I <sub>PU</sub>     | Acitve-Low High-Z Enable Input. The JTRST pin must be low to activate this function.<br>0 = Put all output pins in a high-impedance state<br>1 = Normal operation                                                                                                                                                                  |  |

| N1  | IFSEL0              |                     | <b>Microprocessor Interface Select.</b> During reset, the value on these pins is latched into the IFSEL field of the IFCR register. See Section 7.12.<br>010 = Intel bus mode (multiplexed)                                                                                                                                        |  |

| N2  | IFSEL1              | I <sub>PD</sub>     | 011 = Intel bus mode (nonmultiplexed)<br>100 = Motorola mode (nonmultiplexed)<br>101 = SPI mode (address and data transmitted LSB first)                                                                                                                                                                                           |  |

| P1  | IFSEL2              |                     | 110 = Motorola mode (multiplexed)<br>111 = SPI mode (address and data transmitted MSB first)<br>000, 001 = {unused value}                                                                                                                                                                                                          |  |

| R11 | MASTSLV             | I <sub>PU</sub>     | Master/Slave Select Input. Sets the state of the MASTSLV bit in the MCR3 register.<br>0 = slave mode<br>1 = master mode                                                                                                                                                                                                            |  |

| Τ7  | RESREF              | IA                  | <b>Resistor Reference.</b> This pin must be tied to V <sub>SS</sub> through a 10k $\Omega \pm 1\%$ resistor. The BITS transceivers use this reference resistor to tune internal termination impedance values. The resistor should be placed as close as possible to the device, and capacitance on the RESREF node must be < 10pF. |  |

| M3  | SONSDH              | I <sub>PD</sub>     | <b>SONET/SDH Frequency Select Input.</b> Sets the reset-default state of the SONSDH bit in MCR3, the DIG1SS and DIG2SS bits in MCR6, and the OC9SON bit in T4CR1.<br>0 = SDH rates (N x 2.048MHz)<br>1 = SONET rates (N x 1.544MHz)                                                                                                |  |

| M2  | SRCSW               | I <sub>PD</sub>     | Source Switching. Fast source switching control input. See Section 7.6.5.                                                                                                                                                                                                                                                          |  |

| J2  | SRFAIL              | O <sub>3</sub>      | <b>SRFAIL Status.</b> When MCR10:SRFPIN = 1, this pin follows the state of the SRFAIL status bit in the MSR2 register. This gives the system a very fast indication of the failure of the current reference. When MCR10:SRFPIN = 0, SRFAIL is disabled (low).                                                                      |  |