# **General Description**

The MAX9492 frequency synthesizer is designed to generate multiple clocks for clock distribution in network routers or switches. The device provides a total of six buffered clock outputs (CLK1 to CLK6). CLK1 is the buffered output of the reference clock. CLK2 through CLK6 are independently programmable to generate eight different frequencies based on a 25MHz input crystal: 133, 125, 83, 66, 62.5, 50, 33, and 25MHz. All the outputs are LVCMOS single-ended signals. Either a 25MHz crystal or an external clock can serve as the input reference clock. The MAX9492 incorporates two phase-locked loops (PLLs) with two internal loop filters.

Select the MAX9492's output clock frequency by programming on-chip registers through the MAX9492's I<sup>2</sup>C\* interface. The device also features spread-spectrum capability to reduce electromagnetic interference (EMI). This technique allows spreading the fundamental energy over a wider frequency range, hence reducing the respective energy amplitude. The output frequency spectrum is downspread by -1.25% or -2.5%.

The MAX9492 operates from a 3.3V supply and is guaranteed over the extended temperature range (-40°C to +85°C). The device is available in a space-saving, 20-pin, TQFN, 5mm x 5mm package.

# **Applications**

Network Routers

Telecom/Networking Equipment

Storage Area Networks/Network Attached Storage

- Five LVCMOS Outputs with Independent Frequency Selections

- One Buffered Reference Clock Output

- Eight Selectable Frequencies: 133, 125, 83, 66, 62.5, 50, 33, and 25MHz

- Crystal or an Input-Clock-Based Clock Reference

- Output Frequency Programmed Through I<sup>2</sup>C Interface

- ♦ 0, -1.25%, or -2.5% Selectable Downspreading Rate

- Low Output Period Jitter (Without Spread Spectrum) < 10psRMS</li>

- <220ps Output-to-Output Skew</p>

- Available in 20-Lead, 5mm x 5mm, TQFN Package

- +3.3V Supply

- ♦ -40°C to +85°C Extended Temperature Range

# **Ordering Information**

| PART       | TEMP RANGE     | PIN-<br>PACKAGE                          | PKG<br>CODE |

|------------|----------------|------------------------------------------|-------------|

| MAX9492ETP | -40°C to +85°C | 20 Thin QFN-EP**<br>5mm x 5mm x<br>0.8mm | T2055-3     |

\*\*EP = Exposed pad.

Typical Operating Circuit and Pin Configuration appear at end of data sheet.

\*Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc., or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3V to +4.0V                      |

|----------------------------------------------------------|

| All Other Pins to GND $0.3V$ to (V <sub>DD</sub> + 1.0V) |

| Short-Circuit Duration (all LVCMOS outputs)Continuous    |

| ESD Protection (Human Body Model) ±2kV                   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )    |

| 20-Pin TQFN (derate 20.8mW/°C above +70°C)1667mW         |

| Storage Temperature Range         | 65°C to +165°C |

|-----------------------------------|----------------|

| Maximum Junction Temperature      | +150°C         |

| Operating Temperature Range       | 40°C to +85°C  |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = V_{DDA} = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values at } V_{DD} = V_{DDA} = +3.3V, T_A = +25^{\circ}C, \text{ with CLK1 at 25MHz, and all other CLK_ outputs at 133MHz.}$  (Note 1)

| PARAMETER                      | SYMBOL                              | CONDITIONS                                 | MIN                      | ТҮР | МАХ                      | UNITS |

|--------------------------------|-------------------------------------|--------------------------------------------|--------------------------|-----|--------------------------|-------|

| CLOCK INPUT (X1)               |                                     | •                                          |                          |     |                          | •     |

| Input High Level               | VIH1                                |                                            | 2.0                      |     |                          | V     |

| Input Low Level                | VIL1                                |                                            |                          |     | 0.8                      | V     |

| Input Current                  | li∟1, liH1                          | $V_{X} = 0$ to $V_{DD}$                    | -20                      |     | +20                      | μA    |

| CLOCK OUTPUTS (CLK_)           |                                     |                                            |                          |     |                          |       |

| Output High Level              | V <sub>OH</sub>                     | I <sub>OH</sub> = -100μA                   | V <sub>DD</sub> -<br>0.2 |     |                          | V     |

|                                |                                     | I <sub>OH</sub> = -4mA                     | 2.4                      |     |                          |       |

| Output Low Level               |                                     | I <sub>OL</sub> = 100μA                    |                          |     | 0.2                      | V     |

| Output Low Level               | V <sub>OL</sub>                     | $I_{OL} = 4mA$                             |                          |     | 0.4                      | v     |

| Output Short-Circuit Current   | IOS                                 | $CLK_ = V_{DD}$ or $GND$                   | -60                      |     | +69                      | mA    |

| Output Capacitance             | Co                                  | (Note 2)                                   |                          |     | 5                        | pF    |

| THREE-LEVEL INPUTS (SSC, S     | A0, SA1)                            |                                            |                          |     |                          |       |

| Input High Level               | V <sub>IH2</sub>                    |                                            | 2.5                      |     |                          | V     |

| Input Low Level                | VIL2                                |                                            |                          |     | 0.8                      | V     |

| Input Open Level               | V <sub>IO2</sub>                    |                                            | 1.35                     |     | 1.90                     | V     |

| Input Current                  | I <sub>IL2</sub> , I <sub>IH2</sub> | $V_{IL2} = 0 \text{ or } V_{IH2} = V_{DD}$ | -15                      |     | +15                      | μΑ    |

| SERIAL INTERFACE (SCL, SDA     | (Note 3)                            |                                            |                          |     |                          |       |

| Input High Level               | VIH                                 |                                            | 0.7 x<br>V <sub>DD</sub> |     |                          | V     |

| Input Low Level                | VIL                                 |                                            |                          |     | 0.3 x<br>V <sub>DD</sub> | V     |

| Input Leakage Current          | lıµ, lı∟                            |                                            | -1                       |     | +1                       | μA    |

| Low-Level Output               | Vol                                 | I <sub>SINK</sub> = 4mA                    |                          |     | 0.4                      | V     |

| Input Capacitance              | Ci                                  | (Note 2)                                   |                          |     | 10                       | pF    |

| POWER SUPPLIES                 |                                     |                                            |                          |     |                          |       |

| Digital Power-Supply Voltage   | V <sub>DD</sub>                     |                                            | 3.0                      |     | 3.6                      | V     |

| Analog Power-Supply Voltage    | V <sub>DDA</sub>                    |                                            | 3.0                      |     | 3.6                      | V     |

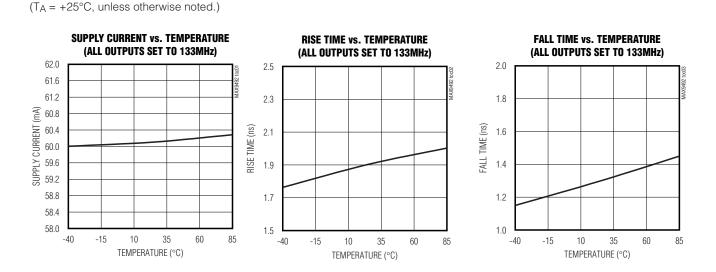

| Total Supply Current           | IDC                                 | $C_L = 10 pF$                              |                          | 60  | 76                       | mA    |

| Output Disabled Supply Current | IOD                                 | All clock registers = 0x0F                 |                          | 18  | 24                       | mA    |

# **AC ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{DDA} = +3.0V \text{ to } +3.6V, C_L = 10\text{pF}, \text{ unless otherwise noted}. Typical values at V_{DD} = V_{DDA} = +3.3V, T_A = +25^{\circ}C$ , with CLK1 at 25MHz and all other CLK\_ outputs at 133MHz.) (Note 2)

| PARAMETER                   | SYMBOL          | CONDITIONS                                        | MIN | TYP   | MAX | UNITS |  |

|-----------------------------|-----------------|---------------------------------------------------|-----|-------|-----|-------|--|

| OUTPUTS (CLK_)              | •               | •                                                 |     |       |     | •     |  |

| Crystal Frequency           |                 |                                                   | 10  |       | 35  | MHz   |  |

| Input Frequency Range       |                 | External clock                                    | 15  |       | 35  | MHz   |  |

| Crystal Frequency Tolerance | Δf <sub>A</sub> |                                                   | -50 |       | +50 | ppm   |  |

| Output-to-Output Skew       | tsко            | Any two CLK_ outputs                              |     |       | 220 | ps    |  |

| Rise Time                   | t <sub>R1</sub> | 20% V <sub>DD</sub> to 80% V <sub>DD</sub>        |     | 1.9   | 2.5 | ns    |  |

| Fall Time                   | tF1             | 80% V <sub>DD</sub> to 20% V <sub>DD</sub>        |     | 1.3   | 2.5 | ns    |  |

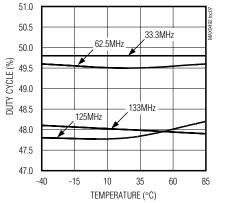

| Duty Cycle                  |                 |                                                   | 40  |       | 60  | %     |  |

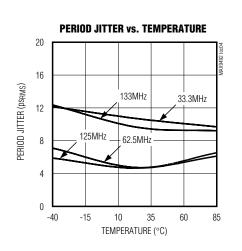

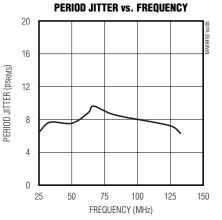

| Output Period Jitter        | JP              | RMS (SSC = 0), CLK1 is disabled to high impedance |     | 10    | 15  | ps    |  |

| Power-Up Time               | tpo             | V <sub>DD</sub> > 2.8V to PLL lock                |     | 2     |     | ms    |  |

| Frequency Spread            |                 | SSC = high                                        |     | -2.5  |     | 0/    |  |

| Frequency Spread            |                 | SSC = floating                                    |     | -1.25 |     | %     |  |

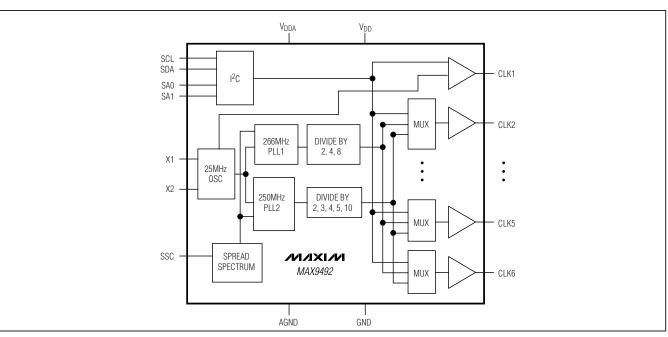

# SERIAL INTERFACE TIMING

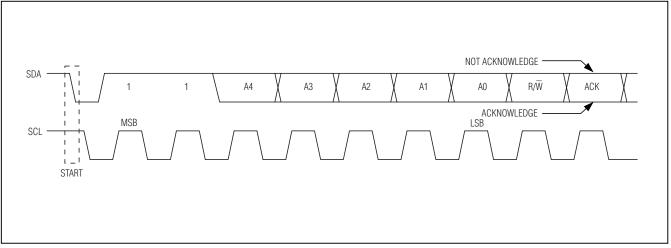

$(V_{DD} = V_{DDA} = +3.3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$  (Note 1, Figure 1)

| PARAMETER                                          | SYMBOL              | CONDITIONS   | MIN                       | ТҮР | МАХ | UNITS |

|----------------------------------------------------|---------------------|--------------|---------------------------|-----|-----|-------|

| Serial Clock                                       | fscl                |              |                           |     | 400 | kHz   |

| Bus Free Time Between STOP<br>and START Conditions | tBUF                |              | 1.3                       |     |     | μs    |

| Hold Time, Repeated START<br>Condition             | <sup>t</sup> hd,sta |              | 0.6                       |     |     | μs    |

| Repeated START Condition<br>Setup Time             | tsu,sta             |              | 0.6                       |     |     | μs    |

| STOP Condition Setup Time                          | tsu,sto             |              | 0.6                       |     |     | μs    |

| Data Hold Time                                     | thd,dat             | (Note 4)     | 15                        |     | 900 | ns    |

| Data Hold Time Slave                               | thd,dat             | (Note 4)     | 15                        |     | 900 | ns    |

| Data Setup Time                                    | tsu,dat             |              | 100                       |     |     | ns    |

| SCL Clock Low Period                               | tLOW                |              | 1.3                       |     |     | μs    |

| SCL Clock High Period                              | thigh               |              | 0.7                       |     |     | μs    |

| Rise Time of SDA and SCL,<br>Receiving             | t <sub>R</sub>      | (Notes 2, 5) | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| Fall Time of SDA and SCL,<br>Receiving             | t⊨                  | (Notes 2, 5) | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

# **MAX9492**

# SERIAL INTERFACE TIMING (continued)

(V\_DD = V\_DDA = +3.3V, T\_A = -40°C to +85°C.) (Note 1, Figure 1)

| PARAMETER                            | SYMBOL | CONDITIONS   | MIN                       | ТҮР | MAX | UNITS |

|--------------------------------------|--------|--------------|---------------------------|-----|-----|-------|

| Fall Time of SDA, Transmitting       | tf,tx  | (Notes 2, 6) | 20 +<br>0.1C <sub>B</sub> |     | 250 | ns    |

| Pulse Width of Spike Suppressed      | tsp    | (Notes 2, 7) | 0                         |     | 50  | ns    |

| Capacitive Load for Each Bus<br>Line | Св     | (Note 2)     |                           |     | 400 | рF    |

**Note 1:** All DC parameters tested at  $T_A = +25^{\circ}$ C. Specifications over temperature are guaranteed by design.

Note 2: Guaranteed by design.

Note 3: No high output level is specified but only the output resistance to the bus. For I<sup>2</sup>C, the high-level voltage is provided by pullup resistors on the bus.

Note 4: The device provides a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) to bridge the undefined region of SCL's falling edge.

Note 5: CB = total capacitance of one bus line in pF. tR and tF measured between 0.3 x VDD and 0.7 x VDD.

Note 6: Bus sink current is less than 6mA. C<sub>B</sub> is the total capacitance of one bus line in pF. t<sub>R</sub> and t<sub>F</sub> are measured between 0.3 x V<sub>DD</sub> and 0.7 x V<sub>DD</sub>.

Note 7: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

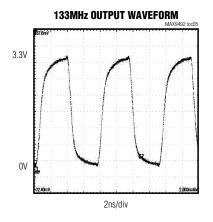

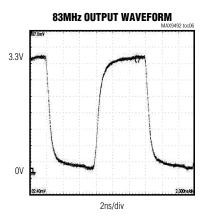

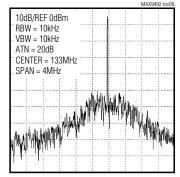

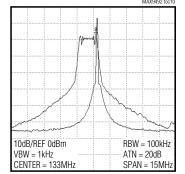

# **Typical Operating Characteristics**

# **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

**MAX9492**

DUTY CYCLE vs. TEMPERATURE

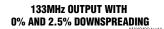

**133MHz OUTPUT 0% DOWNSPREADING**

133MHz OUTPUT WITH 0% AND 1.25% DOWNSPREADING

naracteri

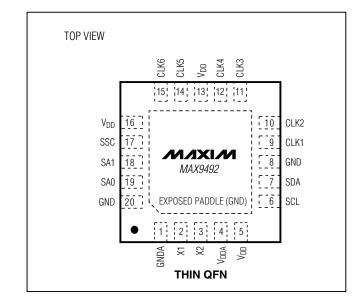

**Pin Description**

| PIN       | NAME             | FUNCTION                                                                                                                                                                                                                       |

|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | GNDA             | Analog Ground                                                                                                                                                                                                                  |

| 2         | X1               | Crystal Connection or Clock Input. If using a 25MHz crystal, connect it to X1 and X2. If using a reference                                                                                                                     |

| 3         | X2               | clock, connect the clock signal to X1 and leave X2 floating. See the Typical Operating Circuit.                                                                                                                                |

| 4         | V <sub>DDA</sub> | Power-Supply Input for Analog Circuits. Bypass to GNDA with a 0.1µF capacitor.                                                                                                                                                 |

| 5, 13, 16 | V <sub>DD</sub>  | Power-Supply Input for Digital Circuits. Bypass to GND with a 0.1µF capacitor.                                                                                                                                                 |

| 6         | SCL              | Serial Clock Input. Serial interface clock.                                                                                                                                                                                    |

| 7         | SDA              | Serial Data I/O. Data I/O of serial interface.                                                                                                                                                                                 |

| 8, 20     | GND              | Digital Ground                                                                                                                                                                                                                 |

| 9         | CLK1             | Clock 1 Output. Buffered reference clock output.                                                                                                                                                                               |

| 10        | CLK2             | Clock 2 Output. Frequency-selectable clock output.                                                                                                                                                                             |

| 11        | CLK3             | Clock 3 Output. Frequency-selectable clock output.                                                                                                                                                                             |

| 12        | CLK4             | Clock 4 Output. Frequency-selectable clock output.                                                                                                                                                                             |

| 14        | CLK5             | Clock 5 Output. Frequency-selectable clock output.                                                                                                                                                                             |

| 15        | CLK6             | Clock 6 Output. Frequency-selectable clock output.                                                                                                                                                                             |

| 17        | SSC              | Spread-Spectrum-Select Input. Selects the spectrum-spread percentage. When SSC is low, spread spectrum is disabled. When SSC is floating, spread spectrum is set to -1.25%. When SSC is high, spread spectrum is set to -2.5%. |

| 18        | SA1              | Address-Select Inputs for Serial Interface. SA0 and SA1 select the serial interface address, as shown in                                                                                                                       |

| 19        | SA0              | Table 1. SA0 and SA1 are three-level inputs, making nine possible address combinations.                                                                                                                                        |

| EP        | GND              | Exposed pad. Connect to GND.                                                                                                                                                                                                   |

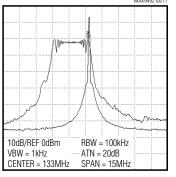

# Block Diagram

6

# **Detailed Description**

The MAX9492 frequency synthesizer is designed to generate multiple clocks for clock distribution in network routers or switches. The device provides a total of six buffered clock outputs (CLK1 to CLK6). CLK1 is the buffered output of the reference clock. CLK2 through CLK6 are independently programmable to generate eight different frequencies based on a 25MHz input crystal: 133, 125, 83, 66, 62.5, 50, 33, and 25MHz. All the outputs are LVCMOS single-ended signals.

Select the MAX9492's output frequency by programming on-chip registers through the I<sup>2</sup>C interface. The MAX9492 also features spread-spectrum capability to reduce EMI. Output frequency spectrum can be downspread by -2.5% or -1.25%. The 25MHz reference comes from either a crystal or an external clock. The MAX9492 incorporates two PLLs with two internal loop filters. The MAX9492 operates from a 3.3V supply.

#### **Reference Frequency Input**

The MAX9492 requires a reference frequency. The reference can be a 25MHz crystal or an external clock signal. If using a 25MHz crystal, connect it across X1 and X2, and connect loading capacitors from X1 and X2 to GND (refer to the crystal manufacturer's specification). If using an external clock, connect the signal to X1 and leave X2 floating.

#### **Power-Up State**

At power-up, the CLK1 output is enabled and free running, the CLK2 to CLK4 outputs are set at 33.3MHz, and the other CLK outputs are disabled at logic-low. The output states can be overridden by writing to the registers through the I<sup>2</sup>C interface.

#### **Serial Interface**

The MAX9492 is programmed through its I<sup>2</sup>C serial interface. This interface has a clock, SCL, and a bidirectional data line, SDA. In an I<sup>2</sup>C system, a master, typically a microcontroller, initiates all data transfers to and from slave devices, and generates the clock to synchronize the data transfers.

The MAX9492 operates as a slave device. The timing of the SDA and SCL signals is detailed in Figure 1. SDA operates as both an input and an open-drain output. A pullup resistor, typically 4.7k $\Omega$ , is required on SDA. SCL operates only as an input. A pullup resistor, typically 4.7k $\Omega$ , is required on SCL.

#### START and STOP Conditions

A master signals the beginning of a transmission with a START condition by transitioning SDA from high to low while SCL is high (Figure 2). When communication is complete, a master issues a STOP condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission.

Figure 1. Serial-Interface Timing Diagram

Figure 2. I<sup>2</sup>C Address and Acknowledge

#### Bit Transfer

One data bit is transferred during each SCL clock cycle. SDA must remain stable during the high period of SCL, as changes in SDA while SCL is high are START and STOP control signals. Idle the interface by pulling both SDA and SCL high.

After 8 bits are transferred, the receiving device generates an acknowledge signal by pulling SDA low for the entire duration of the 9th clock pulse. If the receiving device does not pull SDA low, a not acknowledge is indicated (Figure 2).

| SA0  | SA1  | DEVICE ADDRESS |

|------|------|----------------|

| Open | Open | 110 1000       |

| Low  | Open | 110 0100       |

| High | Open | 110 0010       |

| Open | Low  | 110 1100       |

| Low  | Low  | 110 1001       |

| High | Low  | 111 0000       |

| Open | High | 111 0001       |

| Low  | High | 111 0010       |

| High | High | 111 0100       |

#### Table 1. Device I<sup>2</sup>C Address Selection

## **Device Address**

The MAX9492 features a 7-bit device address, configured by the two three-level address inputs, SA1 and SA0. To select the device address, connect SA1 and SA0 to V<sub>DD</sub>, GND, or leave floating, as indicated in Table 1. The MAX9492 has nine possible addresses, allowing up to nine MAX9492 devices to share the same interface bus.

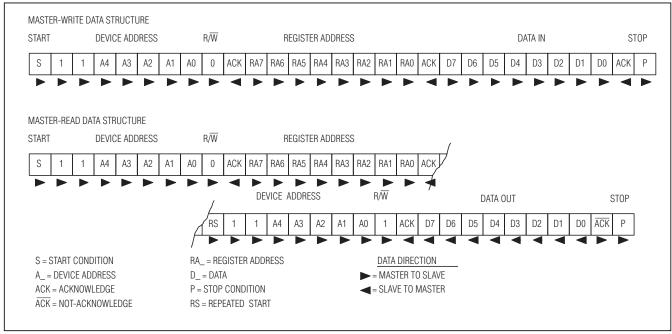

## Writing to the MAX9492

Writing to the MAX9492 begins with a START condition (Figure 3). Following the START condition, each pulse on SCL transfers 1 bit of data. The first 7 bits comprise the device address (see the Device Address section). The 8th bit is low to indicate a write operation. An acknowledge bit is then generated by the MAX9492, signaling that it recognizes its address. The next 8 bits form the register address byte (Table 2) and determine which control register receives the following data byte. The MAX9492 then generates another acknowledge bit. The data byte is then written into the addressed register of the MAX9492. An acknowledge bit by the MAX9492 followed by a required STOP condition by the master completes the communication. To write to the device again, the entire write procedure is repeated; I<sup>2</sup>C burstwrite mode is not supported by the MAX9492.

Figure 3. I<sup>2</sup>C Interface Data Structure

# Reading from the MAX9492

Reading from the MAX9492 registers begins with a START condition and a device address with the write bit set low, then the register address that is to be read, followed by a repeated START condition and a device address with the write bit set high, and finally the data are shifted out (Figure 3). Following a START condition, the first 7 bits comprise the device address. The 8th bit is low to indicate a write operation (to write in the following register address). An acknowledge bit is then generated by the MAX9492, signaling that it recognizes its address. The next 8 bits form the register address, indicating the location of the data to be read, followed by another acknowledge, again generated by the MAX9492. The master then produces a repeated START condition and readdresess the device, with the R/W bit high to indicate a read operation (Figure 3). The MAX9492 generates an acknowledge bit, signaling that it recognizes its address. The data byte is then clocked out of the MAX9492. A final not-acknowledge bit, generated by the master (not required), and a STOP condition, also generated by the master, complete the communication. To read from the device again, the entire read procedure is repeated; I<sup>2</sup>C burst-read mode is not supported by the MAX9492.

# **Device Control Registers**

The MAX9492 has eight control registers. The register addresses and functions are shown in Table 2. The first seven registers are used to set the six outputs, with register 0x00 controlling all outputs simultaneously, and the rest are mapped to individual outputs. All other addresses are reserved and are not to be used.

## Table 2. Register Address Mapping

| REGISTER<br>ADDRESS | OUTPUT PORT                    |  |

|---------------------|--------------------------------|--|

| 00                  | Broadcast to all CLK registers |  |

| 01                  | CLK1                           |  |

| 02                  | CLK2                           |  |

| 03                  | CLK3                           |  |

| 04                  | CLK4                           |  |

| 05                  | CLK5                           |  |

| 06                  | CLK6                           |  |

| All others          | Reserved                       |  |

**MAX9492**

# \_Setting the Clock Frequencies

Each CLK\_ output has an associated control register. The contents of the registers determine the frequencies of their associated outputs. Table 3 provides the frequency mapping for the registers. CLK1 only responds to the 25MHz and high-impedance settings in Table 3. For example, writing 03h to the CLK1 control register does not change CLK1's output frequency to 133.3MHz. The CLK1 output continues to output a buffered reference clock signal.

# Table 3. Output Frequency Selection for CLK1–CLK6

| BITS IN CLKn<br>REGISTERS | OUTPUT FREQUENCY<br>(MHz) |

|---------------------------|---------------------------|

| 00                        | Logic-Low                 |

| 01                        | 133.3                     |

| 02                        | 125                       |

| 03                        | 83.3                      |

| 04                        | 66.6                      |

| 05                        | 62.5                      |

| 06                        | 50                        |

| 07                        | 33.3                      |

| 08                        | 25                        |

| 0F                        | High Impedance            |

# **Spread-Spectrum Control**

The MAX9492 features spread-spectrum output structures to spread radiated emissions over the frequency band. A programmable triangle-wave generator injects an offset element into the master oscillator to dither its output by -1.25% or -2.5%. The dither is controlled by the SSC input. When SSC is low, spread spectrum is disabled. When SSC is floating, spread spectrum is set to -1.25%. When SSC is high, spread spectrum is set to -2.5%.

# Power Supply

The MAX9492 uses a 3.0V to 3.6V power supply connected to V<sub>DD</sub>, and 3.0V to 3.6V connected to V<sub>DDA</sub>. Bypass V<sub>DDA</sub> and V<sub>DD</sub> at the device with a 0.1 $\mu$ F capacitor. Additionally, use bulk bypass capacitors of 10 $\mu$ F where power enters the circuit board.

# Applications Information

#### **Board Layout Considerations**

As with all high-frequency devices, board layout is critical to proper operation. Place the crystal as close as possible to X1 and X2, and minimize parasitic capacitance around the crystal leads. Ensure that the exposed pad makes good contact with GND.

# **Chip Information**

PROCESS: BICMOS

# **Pin Configuration**

#### +3.3V +3.3V 0.1µF 0.1µF VDD VDDA 0.1µF VDD 0 X1 $V_{\text{DD}}$ Opf 25MHz /VI/IXI/VI MAX9492 χ2 CLK1 CLOCK ٠ SFRIAL O SDA OUTPUTS INTERFACE O-SCL CLK6 SA0 SA1 SSC AGND GND Ē 느

# \_Typical Operating Circuit

**MAX9492**

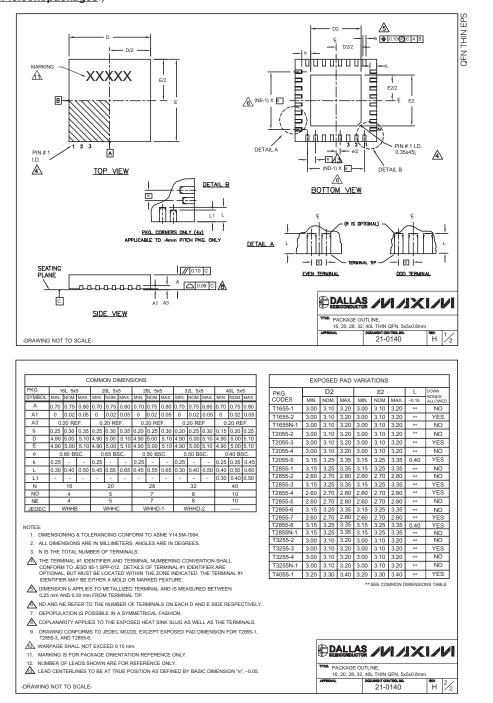

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2005 Maxim Integrated Products Printed USA MAXIM is a registered trademark of Maxim Integrated Products, Inc.