#### 172-pin Unbuffered DDR MicroDIMM Based on DDR333/266 16Mx16 SDRAM

#### Features

- 172-pin Micro Dual In-Line Memory Module (MicroDIMM)

- 16Mx64 Double Unbuffered DDR MicroDIMM based on 16Mx16 DDR SDRAM.

- Performance:

|                         | PC2700 | PC2100 |      |

|-------------------------|--------|--------|------|

| Speed Sort              | -6K    | -75B   | Unit |

| DIMM CAS Latency        | 2.5    | 2.5    |      |

| f CK Clock Frequency    | 166    | 133    | MHz  |

| t CK Clock Cycle        | 6      | 7.5    | ns   |

| f DQ DQ Burst Frequency | 333    | 266    | MHz  |

- Intended for 133 MHz and 166 MHz applications

- Inputs and outputs are SSTL-2 compatible

- VDD = 2.5Volt  $\pm$  0.2, VDDQ = 2.5Volt  $\pm$  0.2

- SDRAMs have 4 internal banks for concurrent operation

- Module has two physical banks

- Differential clock inputs

- Data is read or written on both clock edges

- DRAM DLL aligns DQ and DQS transitions with clock transitions.

- Address and control signals are fully synchronous to positive clock edge

- Programmable Operation:

- DIMM CAS Latency: 2, 2.5

- Burst Type: Sequential or Interleave

- Burst Length: 2, 4, 8

- Operation: Burst Read and Write

- Auto Refresh (CBR) and Self Refresh Modes

- Automatic and controlled precharge commands

- 13/9/1 Addressing (row/column/bank)

- 7.8 μs Max. Average Periodic Refresh Interval

- Serial Presence Detect

- Gold contacts

- SDRAMs in 66-pin TSOP Type II Package

# Description

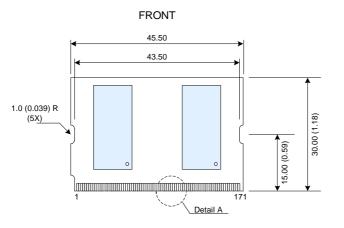

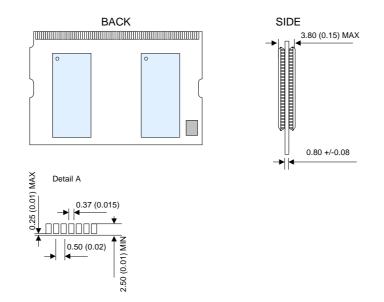

NT128D64SH4B0GA is an unbuffered 172-pin Double Data Rate (DDR) Synchronous DRAM Micro Dual In-Line Memory Module (MicroDIMM), organized as a one-bank 16Mx64 high-speed memory array. The module uses four 16Mx16 DDR SDRAMs in 400 mil TSOP-II packages. All NANYA DDR SDRAM DIMMs provide a high-performance, flexible 8-byte interface in a 45.5mm long space-saving footprint.

The DIMM is intended for use in applications operating up to 166 MHz clock speeds and achieves high-speed data transfer rates of up to 333 MHz. Prior to any access operation, the device CAS latency and burst type/ length/operation type must be programmed into the DIMM by address inputs A0-A12 and I/O inputs BA0 and BA1 using the mode register set cycle.

The DIMM uses serial presence-detect implemented via a serial 2,048-bit EEPROM using a standard IIC protocol. The first 128 bytes of serial PD data are programmed and locked during module assembly. The remaining 128 bytes are available for use by the customer.

# **Ordering Information**

| Part Number         | Spe                       | ed      |                | Organization | Leads | Power |

|---------------------|---------------------------|---------|----------------|--------------|-------|-------|

|                     | 166MHz (6ns @ CL = 2.5)   |         | <b>D</b> 00700 |              |       |       |

| NT128D64SH4B0GA-6K  | 133MHz (7.5ns @ CL = 2)   | DDR333  | PC2700         |              | Gold  | 0.51/ |

|                     | 133MHz (7.5ns @ CL = 2.5) |         | <b>DO</b> 0400 | 16Mx64       |       | 2.5V  |

| NT128D64SH4B0GA-75B | 100MHz (10ns @ CL = 2)    | DDR266B | PC2100         |              |       |       |

# **Pin Description**

| CK0, CK1,<br>CK0, CK1 | Differential Clock Inputs                           | DQ0-DQ63  | Data input/output                          |

|-----------------------|-----------------------------------------------------|-----------|--------------------------------------------|

| CKE0                  | Clock Enable                                        | DQS0-DQS7 | Bi-directional data strobes                |

| RAS                   | Row Address Strobe                                  | DM0-DM7   | Input Data Mask                            |

| CAS                   | Column Address Strobe                               | VDD       | Power (2.5V)                               |

| WE                    | Write Enable                                        | Vddq      | Supply voltage for DQs (2.5V)              |

| SO                    | Chip Selects                                        | Vss       | Ground                                     |

| A0-A9, A11, A12       | Address Inputs                                      | NC        | No Connect                                 |

| A10/AP                | Address Input/Autoprecharge                         | SCL       | Serial Presence Detect Clock Input         |

| BA0, BA1              | SDRAM Bank Address Inputs                           | SDA       | Serial Presence Detect Data input/output   |

| VREF                  | Ref. Voltage for SSTL_2 inputs                      | SA0-2     | Serial Presence Detect Address Inputs      |

| Vddd                  | VDD Identification flag<br>(Not used when VDD=VDDQ) | VDDSPD    | Serial EEPROM positive power supply (2.5V) |

### Pinout

| Pin | Front           | Pin | Back            | Pin | Front           | Pin | Back            | Pin | Front           | Pin | Back            | Pin | Front                     | Pin | Back            |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|-----|---------------------------|-----|-----------------|

| 1   | $V_{REF}$       | 2   | $V_{REF}$       | 45  | $V_{\text{DD}}$ | 46  | $V_{\text{DD}}$ | 89  | $V_{DD}$        | 90  | $V_{\text{DD}}$ | 133 | V <sub>SS</sub>           | 134 | CK1             |

| 3   | $V_{SS}$        | 4   | $V_{\text{SS}}$ | 47  | DQS2            | 48  | DM2             | 91  | BA0             | 92  | RAS             | 135 | V <sub>SS</sub>           | 136 | $V_{SS}$        |

| 5   | DQ0             | 6   | DQ4             | 49  | DQ18            | 50  | DQ22            | 93  | WE              | 94  | CAS             | 137 | DQ48                      | 138 | DQ52            |

| 7   | DQ1             | 8   | DQ5             | 51  | Vss             | 52  | $V_{\text{SS}}$ | 95  | SO              | 96  | NC              | 139 | DQ49                      | 140 | DQ53            |

| 9   | $V_{\text{DD}}$ | 10  | $V_{\text{DD}}$ | 53  | DQ19            | 54  | DQ23            | 97  | A13             | 98  | RFU             | 141 | $V_{DD}$                  | 142 | $V_{\text{DD}}$ |

| 11  | DQS0            | 12  | DM0             | 55  | DQ24            | 56  | DQ28            | 99  | Vss             | 100 | $V_{SS}$        | 143 | DQS6                      | 144 | DM6             |

| 13  | DQ2             | 14  | DQ6             | 57  | $V_{DD}$        | 58  | $V_{\text{DD}}$ | 101 | DQ32            | 102 | DQ36            | 145 | DQ50                      | 146 | DQ54            |

| 15  | $V_{\text{SS}}$ | 16  | $V_{\text{SS}}$ | 59  | DQ25            | 60  | DQ29            | 103 | DQ33            | 104 | DQ37            | 147 | Vss                       | 148 | $V_{\text{SS}}$ |

| 17  | DQ3             | 18  | DQ7             | 61  | DQS3            | 62  | DM3             | 105 | $V_{\text{DD}}$ | 106 | $V_{\text{DD}}$ | 149 | DQ51                      | 150 | DQ55            |

| 19  | DQ8             | 20  | DQ12            | 63  | V <sub>ss</sub> | 64  | $V_{\text{SS}}$ | 107 | DQS4            | 108 | DM4             | 151 | DQ56                      | 152 | DQ60            |

| 21  | $V_{\text{DD}}$ | 22  | $V_{\text{DD}}$ | 65  | DQ26            | 66  | DQ30            | 109 | DQ34            | 110 | DQ38            | 153 | $V_{DD}$                  | 154 | $V_{\text{DD}}$ |

| 23  | DQ9             | 24  | DQ13            | 67  | DQ27            | 68  | DQ31            | 111 | $V_{\text{SS}}$ | 112 | $V_{\text{SS}}$ | 155 | DQ57                      | 156 | DQ61            |

| 25  | DQS1            | 26  | DM1             | 69  | $V_{DD}$        | 70  | $V_{\text{DD}}$ | 113 | DQ35            | 114 | DQ39            | 157 | DQS7                      | 158 | DM7             |

| 27  | $V_{\text{SS}}$ | 28  | $V_{\text{SS}}$ | 71  | NC              | 72  | CKE0            | 115 | DQ40            | 116 | DQ44            | 159 | V <sub>ss</sub>           | 160 | $V_{\text{SS}}$ |

| 29  | DQ10            | 30  | DQ14            | 73  | A12             | 74  | A11             | 117 | $V_{\text{DD}}$ | 118 | $V_{\text{DD}}$ | 161 | DQ58                      | 162 | DQ62            |

| 31  | DQ11            | 32  | DQ15            | 75  | A9              | 76  | A8              | 119 | DQ41            | 120 | DQ45            | 163 | DQ59                      | 164 | DQ63            |

| 33  | $V_{\text{DD}}$ | 34  | $V_{\text{DD}}$ | 77  | A7              | 78  | A6              | 121 | DQS5            | 122 | DM5             | 165 | V <sub>DD</sub>           | 166 | $V_{\text{DD}}$ |

| 35  | CK0             | 36  | $V_{\text{DD}}$ | 79  | $V_{SS}$        | 80  | $V_{SS}$        | 123 | $V_{\text{SS}}$ | 124 | $V_{\text{SS}}$ | 167 | SDA                       | 168 | SA0             |

| 37  | <u>CK0</u>      | 38  | $V_{SS}$        | 81  | A5              | 82  | A4              | 125 | DQ42            | 126 | DQ46            | 169 | SCL                       | 170 | SA1             |

| 39  | $V_{\text{SS}}$ | 40  | $V_{SS}$        | 83  | A3              | 84  | A2              | 127 | DQ43            | 128 | DQ47            | 171 | $V_{\text{DD}}\text{SPD}$ | 172 | SA2             |

| 41  | DQ16            | 42  | DQ20            | 85  | A1              | 86  | A0              | 129 | $V_{\text{DD}}$ | 130 | $V_{\text{DD}}$ |     |                           |     |                 |

| 43  | DQ17            | 44  | DQ21            | 87  | A10/AP          | 88  | BA1             | 131 | $V_{\text{DD}}$ | 132 | CK1             |     |                           |     |                 |

Note: All pin assignments are consistent for all 8-byte unbuffered versions.

# Input/Output Functional Description

| Symbol                        | Туре   | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK0, CK1                      | (SSTL) | Positive<br>Edge | The positive line of the differential pair of system clock inputs. All the DDR SDRAM address and control inputs are sampled on the rising edge of their associated clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CKO, CK1                      | (SSTL) | Negative<br>Edge | The negative line of the differential pair of system clock inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CKE0                          | (SSTL) | Active<br>High   | Activates the SDRAM CK signal when high and deactivates the CK signal when low. By deactivating the clocks, CKE low initiates the Power Down mode, or the Self-Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SO                            | (SSTL) | Active<br>Low    | Enables the associated SDRAM command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RAS, CAS, WE                  | (SSTL) | Active<br>Low    | When sampled at the positive rising edge of the clock, $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ define the operation to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VREF                          | Supply |                  | Reference voltage for SSTL-2 inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDDQ                          | Supply |                  | Isolated power supply for the DDR SDRAM output buffers to provide improved noise immunity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BA0, BA1                      | (SSTL) | -                | Selects which SDRAM bank is to be active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A0 - A9<br>A10/AP<br>A11, A12 | (SSTL) | -                | During a Bank Activate command cycle, A0-A12 defines the row address (RA0-RA12) when sampled at the rising clock edge.<br>During a Read or Write command cycle, A0-A8 defines the column address (CA0-CA8) when sampled at the rising clock edge. In addition to the column address, AP is used to invoke Auto-precharge operation at the end of the Burst Read or Write cycle. If AP is high, auto-precharge is selected and BA0/BA1 define the bank to be precharged. If AP is low, auto-precharge command cycle, AP is used in conjunction with BA0/BA1 to control which bank(s) to precharge. If AP is high all 4 banks will be precharged regardless of the state of BA0/BA1. If AP is low, then BA0/BA1 are used to define which bank to pre-charge. |

| DQ0 - DQ63                    | (SSTL) | -                | Data and Check Bit input/output pins operate in the same manner as on conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DQS0 - DQS7                   | (SSTL) | Active<br>High   | Data strobes: Output with read data, input with write data. Edge aligned with read data, centered on write data. Used to capture write data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DM0 - DM7                     | Input  | Active<br>High   | The data write masks, associated with one data byte. In Write mode, DM operates as a byte mask by allowing input data to be written if it is low but blocks the write operation if it is high. In Read mode, DM lines have no effect. DM8 is associated with check bits CB0-CB7, and is not used on x64 modules.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD, VSS                      | Supply |                  | Power and ground for the DDR SDRAM input buffers and core logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SA0 - SA2                     |        | -                | Address inputs. Connected to either VDD or VSS on the system board to configure the Serial Presence Detect EEPROM address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SDA                           |        | -                | This bi-directional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be connected from the SDA bus line to V DD to act as a pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SCL                           |        | -                | This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected from the SCL bus time to V DD to act as a pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V DDSPD                       | Supply |                  | Serial EEPROM positive power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

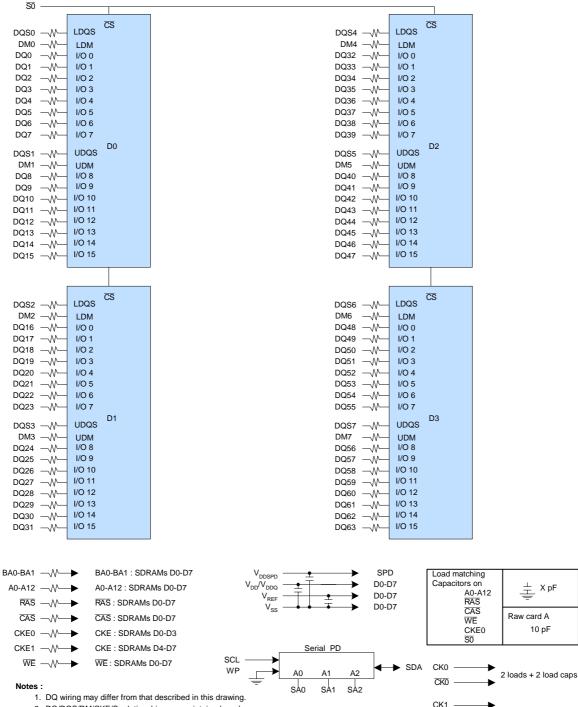

#### Functional Block Diagram (1 Bank, 16Mx16 DDR SDRAMs)

- 2. DQ/DQS/DM/CKE/S relationships are maintained as shown.

- 3. DQ/DQS/DM/DQS resistors are 22+/- 5% Ohms.

CK1

2 loads + 2 load caps

#### Serial Presence Detect -- Part 1 of 2

16Mx64 SDRAM DIMM based on 16Mx16, 4Banks, 8K Refresh, 2.5V DDR SDRAMs with SPD

| Byte     | Description                                                | SPD Er        | trv Value       |                            | Data Entry<br>lecimal) | Note |  |  |

|----------|------------------------------------------------------------|---------------|-----------------|----------------------------|------------------------|------|--|--|

| Буте     | Description                                                | DDR333<br>-6K | DDR266B<br>-75B | DDR333 DDR266B<br>-6K -75B |                        |      |  |  |

| 0        | Number of Serial PD Bytes Written during Production        | 1             | 28              | 80                         |                        |      |  |  |

| 1        | Total Number of Bytes in Serial PD device                  | 256           |                 | 08                         |                        | 08   |  |  |

| 2        | Fundamental Memory Type                                    | SDRAM DDR     |                 | 07                         |                        | 07   |  |  |

| 3        | Number of Row Addresses on Assembly                        | 13            |                 | 0D                         |                        |      |  |  |

| 4        | Number of Column Addresses on Assembly                     | 9             |                 | 09                         |                        |      |  |  |

| 5        | Number of DIMM Bank                                        |               | 1               | C                          | )1                     |      |  |  |

| 6        | Data Width of Assembly                                     | ×             | (64             | 40                         |                        |      |  |  |

| 7        | Data Width of Assembly (cont')                             | ×             | (64             | C                          | 00                     |      |  |  |

| 8        | Voltage Interface Level of this Assembly                   | SSTL 2.5V     |                 | C                          | )4                     |      |  |  |

| 9        | DDR SDRAM Device Cycle Time at CL=2.5                      | 6ns           | 7.5ns           | 60                         | 75                     |      |  |  |

| 10       | DDR SDRAM Device Access Time from Clock at CL=2.5          | 0.7ns         | 0.75ns          | 70                         | 75                     |      |  |  |

| 11       | DIMM Configuration Type                                    | Non           | -Parity         | C                          | 00                     |      |  |  |

| 12       | Refresh Rate/Type                                          |               | (7.8us)         | 82                         |                        |      |  |  |

| 13       | Primary DDR SDRAM Width                                    |               | (16             | 10                         |                        | ,    |  |  |

| 14       | Error Checking DDR SDRAM Device Width                      |               | J/A             | 00                         |                        |      |  |  |

| 15       | DDR SDRAM Device Attr: Min CLK Delay, Random Col<br>Access |               | Clock           |                            | )1                     |      |  |  |

| 16       | DDR SDRAM Device Attributes: Burst Length Supported        | 2             | 4,8             | 0                          | )E                     |      |  |  |

| 17       | DDR SDRAM Device Attributes: Number of Device Banks        |               | 4               | 04                         |                        |      |  |  |

| 18       | DDR SDRAM Device Attributes: CAS Latencies Supported       | 2/2.5         | 2/2.5           | 0C                         | 0C                     |      |  |  |

| 19       | DDR SDRAM Device Attributes: CS Latency                    |               | 0               | 01                         |                        |      |  |  |

| 20       | DDR SDRAM Device Attributes: WE Latency                    |               | 1               | 02                         |                        |      |  |  |

| 21       | DDR SDRAM Device Attributes:                               | Differen      | tial Clock      | 20                         |                        |      |  |  |

| 22       | DDR SDRAM Device Attributes: General                       |               | age Tolerance   |                            |                        |      |  |  |

| 23       | Minimum Clock Cycle at CL=2                                | 7.5ns         | 10ns            | 75                         | A0                     |      |  |  |

| 24       | Maximum Data Access Time from Clock at CL=2                | 0.70ns        | 0.75ns          | 70                         | 75                     |      |  |  |

| 25       | Minimum Clock Cycle Time at CL=1                           |               | V/A             |                            | 00                     |      |  |  |

| 26       | Maximum Data Access Time from Clock at CL=1                |               | V/A             |                            | 00                     |      |  |  |

| 27       | Minimum Row Precharge Time (tRP)                           | 18ns          | 20ns            | 48                         | 50                     |      |  |  |

| 28       | Minimum Row Active to Row Active delay (tRRD)              | 12ns          | 15ns            | 30                         | 3C                     |      |  |  |

| 29       | Minimum RAS to CAS delay (tRCD)                            | 12/13<br>18ns | 20ns            | 48                         | 50                     | -    |  |  |

| 30       | Minimum RAS Pulse Width (tRAS)                             | 42ns          | 45ns            | 40<br>2A                   | 2D                     | -    |  |  |

| 31       | Module Bank Density                                        |               | 8MB             |                            | 20                     | -    |  |  |

| 32       | Address and Command Setup Time Before Clock                | 0.75ns        | 0.9ns           | 75                         | 90                     | -    |  |  |

| 33       | Address and Command Hold Time After Clock                  | 0.75ns        | 0.9ns           | 75                         | 90                     | -    |  |  |

| 34       | Data Input Setup Time Before Clock                         | 0.45ns        | 0.5ns           | 45                         | 50                     |      |  |  |

| 35       | Data Input Hold Time After Clock                           | 0.45hs        | 0.5hs           | 45                         | 50                     | -    |  |  |

| 36-61    | Reserved                                                   |               | efined          |                            | )0                     |      |  |  |

| 62       | SPD Revision                                               | Initial       |                 | 00                         | 00                     |      |  |  |

| 62<br>63 | Checksum Data                                              | IIIIudi       | Initial         | <br>F1                     | A6                     |      |  |  |

#### Serial Presence Detect -- Part 2 of 2

16Mx64 SDRAM DIMM based on 16Mx16, 4Banks, 8K Refresh, 2.5V DDR SDRAMs with SPD

| 33 DDR266B<br>-75B<br>NANYA<br>N/A | -                                 | DDR266B<br>-75B<br>300000000              | Note                                          |

|------------------------------------|-----------------------------------|-------------------------------------------|-----------------------------------------------|

| NANYA                              | 7F7F7F0                           | 300000000                                 |                                               |

|                                    | -                                 |                                           |                                               |

| N/A                                | C                                 |                                           |                                               |

|                                    | 00                                |                                           |                                               |

| N/A                                | 00                                | 00                                        |                                               |

| N/A                                |                                   | 00                                        |                                               |

| r/Week Code                        | yy/ww                             |                                           | 1, 2                                          |

| rial Number                        | (                                 | 00                                        |                                               |

| Undefined 00                       |                                   |                                           |                                               |

| r                                  | N/A<br>r/Week Code<br>rial Number | N/A (<br>r/Week Code yy,<br>rial Number ( | N/A 00<br>r/Week Code yy/ww<br>rial Number 00 |

2. ww= Binary coded decimal year code, 01-52(Decimal), 01-34(Hex)

#### **Absolute Maximum Ratings**

| Symbol                             | Parameter                              | Rating           | Units |

|------------------------------------|----------------------------------------|------------------|-------|

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on I/O pins relative to Vss    | -0.5 to VDDQ+0.5 | V     |

| V <sub>IN</sub>                    | Voltage on Input relative to Vss       | -0.5 to +3.6     | V     |

| V <sub>DD</sub>                    | Voltage on VDD supply relative to Vss  | -0.5 to +3.6     | V     |

| V <sub>DDQ</sub>                   | Voltage on VDDQ supply relative to Vss | -0.5 to +3.6     | V     |

| T <sub>A</sub>                     | Operating Temperature (Ambient)        | 0 to +70         | °C    |

| T <sub>STG</sub>                   | Storage Temperature (Plastic)          | -55 to +150      | °C    |

| PD                                 | Power Dissipation                      | 4                | W     |

| IOUT                               | Short Circuit Output Current           | 50               | mA    |

**Note:** Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## Capacitance

| Parameter                                                   | Symbol | Max. | Units | Notes |

|-------------------------------------------------------------|--------|------|-------|-------|

| Input Capacitance: CK0, CK0, CK1, CK1, CK2, CK2             | CI1    | TBD  | pF    | 1     |

| Input Capacitance: A0-A12, BA0, BA1, WE, RAS, CAS, CKE0, SO | CI2    | TBD  | pF    | 1     |

| Input Capacitance: SA0-SA2, SCL                             | CI4    | TBD  | pF    | 1     |

| Input/Output Capacitance: DQ0-63; DQS0-7                    | CIO1   | TBD  | pF    | 1, 2  |

| Input/Output Capacitance: SDA                               | Сюз    | TBD  | pF    |       |

1. VDDQ = VDD = 2.5V ± 0.2V, f = 100 MHz, TA = 25 °C, VOUT (DC) = VDDQ/2, VOUT (Peak to Peak) = 0.2V.

2. DQS inputs are grouped with I/O pins reflecting the fact that they are matched in loading to DQ and DQS to facilitate trace matching at the board level.

### **DC Electrical Characteristics and Operating Conditions**

(TA = 0 °C ~ 70 °C;  $V_{DDQ}$  = 2.5V ± 0.2V;  $V_{DD}$  = 2.5V ± 0.2V, See AC Characteristics)

| Symbol    | Parameter                                                                                   | Min         | Max         | Units | Notes |

|-----------|---------------------------------------------------------------------------------------------|-------------|-------------|-------|-------|

| Vdd       | Supply Voltage                                                                              | 2.3         | 2.7         | V     | 1     |

| Vddq      | I/O Supply Voltage                                                                          | 2.3         | 2.7         | V     | 1     |

| VSS, VSSQ | Supply Voltage, I/O Supply Voltage                                                          | 0           | 0           | V     |       |

| Vref      | I/O Reference Voltage                                                                       | 0.49 x Vddq | 0.51 x Vddq | V     | 1, 2  |

| VTT       | I/O Termination Voltage (System)                                                            | Vref - 0.04 | Vref + 0.04 | V     | 1, 3  |

| VIH (DC)  | Input High (Logic1) Voltage                                                                 | Vref + 0.15 | Vddq + 0.3  | V     | 1     |

| VIL (DC)  | Input Low (Logic0) Voltage                                                                  | -0.3        | Vref - 0.15 | V     | 1     |

| VIN (DC)  | Input Voltage Level, CK and CK Inputs                                                       | -0.3        | Vddq + 0.3  | V     | 1     |

| VID (DC)  | Input Differential Voltage, CK and CK Inputs                                                | 0.30        | V ddq + 0.6 | V     | 1, 4  |

| lı        | Input Leakage Current Any input $0V \le VIN \le VDD$ ; (All other pins not under test = 0V) | -5          | 5           | uA    | 1     |

| loz       | Output Leakage Current (DQs are disabled; $0V \le V_{out} \le V_{DDQ}$                      | -5          | 5           | uA    | 1     |

| Іон       | Output High Current<br>(VOUT = VDDQ -0.373V, min VREF, min VTT)                             | -16.8       | -           | mA    | 1     |

| IOL       | Output Low Current<br>(VOUT = 0.373, max VREF, max VTT)                                     | 16.8        | -           | mA    | 1     |

1. Inputs are not recognized as valid until VREF stabilizes.

2. VREF is expected to be equal to 0.5 V DDQ of the transmitting device, and to track variations in the DC level of the same.

Peak-to-peak noise on VREF may not exceed 2% of the DC value.

3. VTT is not applied directly to the DIMM. VTT is a system supply for signal termination resistors, is expected to be set equal to VREF, and must track variations in the DC level of VREF.

4. VID is the magnitude of the difference between the input level on CK and the input level on CK.

### **AC Characteristics**

(Notes 1-5 apply to the following Tables; Electrical Characteristics and DC Operating Conditions, AC Operating Conditions, Operating, Standby, and Refresh Currents, and Electrical Characteristics and AC Timing.)

- Conditions, Operating, Standby, and Refresh Currents, and Electrical Characteristics and

- 1. All voltages referenced to Vss.

- 2. Tests for AC timing, IDD, and electrical, AC and DC characteristics, may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

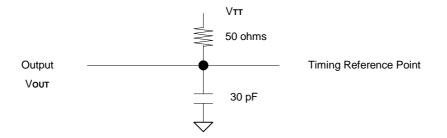

- 3. Outputs measured with equivalent load. Refer to the AC Output Load Circuit below.

- 4. AC timing and IDD tests may use a VIL to VIH swing of up to 1.5V in the test environment, but input timing is still referenced to VREF (or to the crossing point for CK,  $\overline{CK}$ ), and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals is 1V/ns in the range between VIL (AC) and VIH (AC) unless otherwise specified.

- 5. The AC and DC input level specifications are as defined in the SSTL\_2 Standard (i.e. the receiver effectively switches as a result of the signal crossing the AC input level, and remains in that state as long as the signal does not ring back above (below) the DC input LOW (HIGH) level.

# **AC Output Load Circuits**

# **AC Operating Conditions**

(TA = 0 °C ~ 70 °C;  $V_{DDQ}$  = 2.5V ± 0.2V;  $V_{DD}$  = 2.5V ± 0.2V, See AC Characteristics)

| Symbol   | Parameter/Condition                                                               | Min              | Max              | Unit | Notes   |

|----------|-----------------------------------------------------------------------------------|------------------|------------------|------|---------|

| VIH (AC) | Input High (Logic 1) Voltage                                                      | V ref + 0.31     |                  | V    | 1, 2    |

| VIL (AC) | Input Low (Logic 0) Voltage                                                       |                  | V ref - 0.31     | V    | 1, 2    |

| VID (AC) | Input Differential Voltage, CK and CK Inputs                                      | 0.62             | V DDQ + 0.6      | V    | 1, 2, 3 |

| VIX (AC) | Input Differential Pair Cross Point Voltage, CK and $\overline{\text{CK}}$ Inputs | (0.5*VDDQ) - 0.2 | (0.5*VDDQ) + 0.2 | V    | 1, 2, 4 |

1. Input slew rate = 1V/ns.

2. Inputs are not recognized as valid until V REF stabilizes.

3. V ID is the magnitude of the difference between the input level on CK and the input level on CK.

4. The value of V IX is expected to equal 0.5\*V DDQ of the transmitting device and must track variations in the DC level of the same.

## **Operating, Standby, and Refresh Currents**

(TA = 0 °C ~ 70 °C;  $V_{DDQ}$  = 2.5V ± 0.2V;  $V_{DD}$  = 2.5V ± 0.2V, See AC Characteristics)

| Operating Current: one bank; active/precharge; tRC = tRC (MIN); tCK = tCK<br>MIN); DQ, DM, and DQS inputs changing twice per clock cycle; address<br>nd control inputs changing once per clock cycle<br>Operating Current: one bank; active/read/precharge; Burst = 2; tRC = tRC<br>MIN); CL=2.5; tCK = tCK (MIN); IOUT = 0mA; address and control inputs | 460                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 380                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIN); CL=2.5; tCK = tCK (MIN); IOUT = 0mA; address and control inputs                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ., 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| hanging once per clock cycle                                                                                                                                                                                                                                                                                                                              | 700                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 520                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| recharge Power-Down Standby Current: all banks idle; power-down node; CKE $\leq$ VIL (MAX); tCK = tCK (MIN)                                                                                                                                                                                                                                               | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| dle Standby Current: CS $\geq$ VIH (MIN); all banks idle; CKE $\geq$ VIH (MIN); tCK = CK (MIN); address and control inputs changing once per clock cycle                                                                                                                                                                                                  | 220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |