### **LP3972**

# Power Management Unit for Advanced Application Processors

### **General Description**

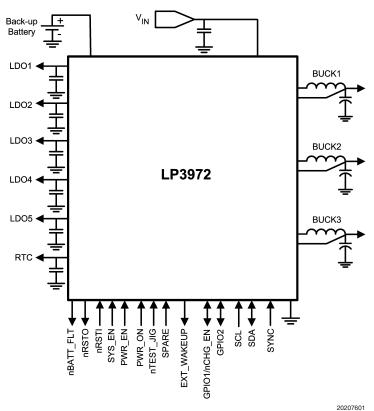

The LP3972 is a multi-function, programmable Power Management Unit, designed especially for advanced application processors. The LP3972 is optimized for low power handheld applications and provides 6 low dropout, low noise linear regulators, three DC/DC magnetic buck regulators, a back-up battery charger and two GPIO's. A high speed serial interface is included to program individual regulator output voltages as well as on/off control.

### **Key Specifications**

#### **Buck Regulators**

- Programmable V<sub>OUT</sub> from 0.725 to 3.3V

- Up to 95% efficiency

- Up to 1.6A output current

- ±3% output voltage accuracy

#### LDO's

- Programmable V<sub>OUT</sub> of 1.0V-3.3V

- ±3% output voltage accuracy

- 150/300/400 mA output currents

- LDO RTC 30 mA

- LDO 1 300 mA

- LDO 2 150 mA

- LDO 3 150 mALDO 4 150 mA

- LDO 4 130 mA

- 100 mV (typ) dropout

#### **Features**

- Compatible with advanced applications processors requiring DVM (Dynamic Voltage Management)

- Three buck regulators for powering high current processor functions or I/O's

- 6 LDO's for powering RTC, peripherals, and I/O's

- Backup battery charger with automatic switch for lithium-manganese coin cell batteries and Super capacitors

- I<sup>2</sup>C compatible high speed serial interface

- Software control of regulator functions and settings

- Precision internal reference

- Thermal overload protection

- Current overload protection

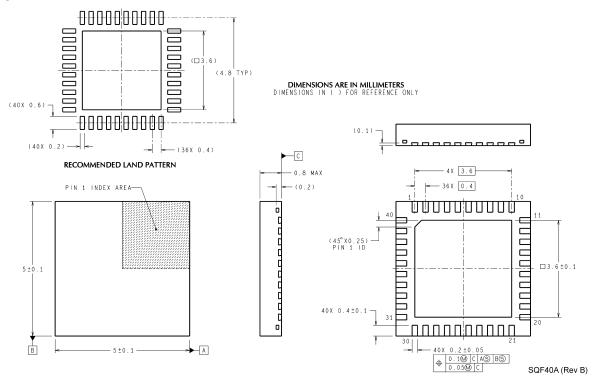

- Tiny 40-pin 5x5 mm LLP package

### **Applications**

- PDA phones

- Smart phones

- Personal Media Players

- Digital cameras

- Application processors

- Intel Xscale

- Freescale

- Samsung

# **Simplified Application Circuit**

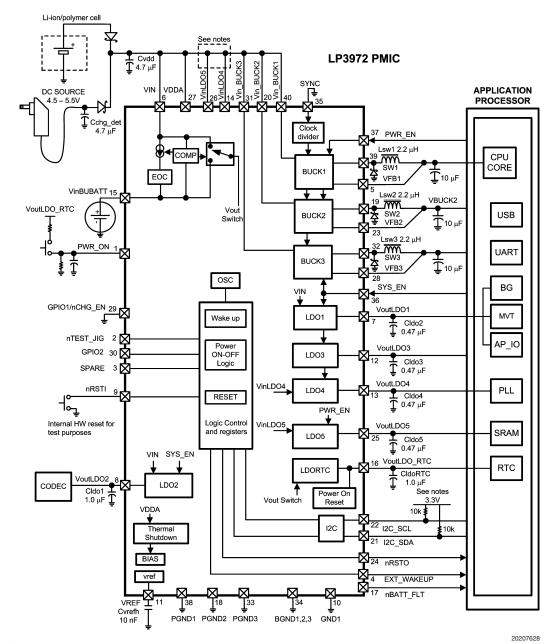

### Simplified Application Circuit (Continued)

- The I<sup>2</sup>C lines are pulled up via a I/O source

- V<sub>IN</sub>LDO4, 5 can either be powered from main battery source, or by a buck regulator or V<sub>IN</sub>.

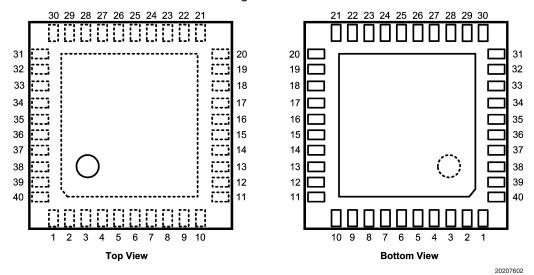

### **Connection Diagrams and Package Mark Information**

40-Pin Leadless Leadframe Package NS Package Number SQF40A

Note: Circle marks pin 1 position.

#### Package Mark

Note: The actual physical placement of the package marking will vary from part to part.

(\*) UZTTYY format: 'U' — wafer fab code; 'Z' — assembly code; 'XY' 2 digit date code; 'TT' — die run code. See http://www.national.com/quality/marking\_convertion.html for more information on marking information.

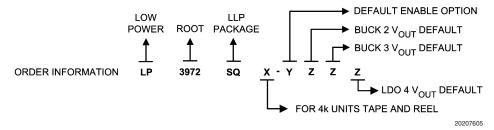

# **Ordering Information**

| Voltage Option | Order Number   | Package Type | NSC Package | Package Marking | Supplied As      |

|----------------|----------------|--------------|-------------|-----------------|------------------|

|                |                |              | Drawing     |                 |                  |

| Voltage A514   | LP3972SQ-A514  | 40 lead LLP  | SQF040A     | 72-A514         | 1000 tape & reel |

| Voltage A514   | LP3972SQX-A514 | 40 lead LLP  | SQF040A     | 72-A514         | 4500 tape & reel |

| Voltage A413   | LP3972SQ-A413  | 40 lead LLP  | SQF040A     | 72-A413         | 1000 tape & reel |

| Voltage A413   | LP3972SQX-A413 | 40 lead LLP  | SQF040A     | 72-A413         | 4500 tape & reel |

| Voltage E514   | LP3972SQ-E514  | 40 lead LLP  | SQF040A     | 72-E514         | 1000 tape & reel |

| Voltage E514   | LP3972SQX-E514 | 40 lead LLP  | SQF040A     | 72-E514         | 4500 tape & reel |

| Voltage I514   | LP3972SQ-I514  | 40 lead LLP  | SQF040A     | 72-I514         | 1000 tape & reel |

| Voltage I514   | LP3972SQX-I514 | 40 lead LLP  | SQF040A     | 72-1514         | 4500 tape & reel |

# Default $V_{\rm OUT}$ Coding

| Z | Default V <sub>OUT</sub> |

|---|--------------------------|

| 0 | 1.3                      |

| 1 | 1.8                      |

| 2 | 2.5                      |

| 3 | 2.8                      |

| 4 | 3.0                      |

| 5 | 3.3                      |

| 6 | 1.0                      |

| 7 | 1.4                      |

| 8 | 1.2                      |

| 9 | 1.25                     |

# **Pin Descriptions**

| Pin #                                        | Name                                                                          | I/O           | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------|-------------------------------------------------------------------------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

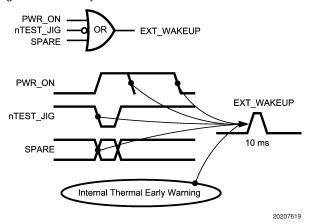

| 1                                            | PWR_ON                                                                        | I             | D                     | CPU Wakeup input, this can be a push button event to indicate the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                              |                                                                               |               |                       | device has been turned on. Phone / PDA main power button. Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              |                                                                               |               |                       | is debounced internally on the PMIC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                              |                                                                               |               |                       | If the POWER_ON is held low this will indicate to the PMIC to turn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                              |                                                                               |               |                       | off. Active high Polarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2                                            | nTEST_JIG                                                                     | I             | D                     | This is a input signal used for a turn on event coming from the bed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                              |                                                                               |               |                       | of nails tester during production. Active low polarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3                                            | SPARE                                                                         | I             | D                     | CPU Wakeup input to indicate that a HW external event has                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                              |                                                                               |               |                       | occurred, i.e. flipping the cell phone to power up the display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4                                            | EXT_WAKEUP                                                                    | 0             | D                     | This signal is asserted when DC POWER source has been                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              |                                                                               |               |                       | asserted, or when the PWR_ON button is held down to turn off the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              |                                                                               |               |                       | PMIC. Wake up on power detection, and power down detection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5                                            | FB1                                                                           | I             | Α                     | Buck1 input feedback terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6                                            | V <sub>IN</sub>                                                               | ı             | PWR                   | Battery Input (Internal circuitry and LDO1-3 power input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7                                            | V <sub>OUT</sub> LDO1                                                         | 0             | PWR                   | LDO1 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8                                            | V <sub>OUT</sub> LDO2                                                         | 0             | PWR                   | LDO2 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9                                            | nRSTI                                                                         |               | D                     | Active low Reset pin. Signal used to reset the IC (by default is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ü                                            |                                                                               | ·             |                       | pulled high internally). Typically a push button reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10                                           | GND1                                                                          | G             | G                     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11                                           | VREF                                                                          | 0             | A                     | Bypass Cap. for the high internal impedance reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12                                           | V <sub>OUT</sub> LDO3                                                         | 0             | PWR                   | LDO3 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                              |                                                                               | 0             |                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13                                           | V <sub>OUT</sub> LDO4                                                         |               | PWR                   | LDO4 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 14                                           | V <sub>IN</sub> LDO4                                                          | I             | PWR                   | Power input to LDO4, this can be connected to either from a 1.8V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              | V DUDATT                                                                      |               | DWD                   | supply to main Battery supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15                                           | V <sub>IN</sub> BUBATT                                                        | <u> </u>      | PWR                   | Back Up Battery input supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16                                           | V <sub>OUT</sub><br>LDO_RTC                                                   | 0             | PWR                   | LDO_RTC output supply to the RTC of the application processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17                                           | nBATT_FLT                                                                     | 0             | D                     | Main Battery fault output, indicates the main battery is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                              |                                                                               |               |                       | (discharged) or the dc source has been removed from the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                              |                                                                               |               |                       | This gives the processor an indicator that the power will shut down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                              |                                                                               |               |                       | During this time the processor will operate from the back up coin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                              |                                                                               |               |                       | cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18                                           | PGND2                                                                         | G             | G                     | Buck2 NMOS Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19                                           | SW2                                                                           | 0             | PWR                   | Buck2 switcher output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 20                                           | V <sub>IN</sub> Buck2                                                         |               | PWR                   | Battery input power to Buck2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20                                           | VIN DUCKZ                                                                     |               | 1                     | Battery input power to Back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21                                           | SDA                                                                           | I/O           | D                     | I <sup>2</sup> C Data (Bidirectional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              | + " +                                                                         | I/O           |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21                                           | SDA                                                                           | I/O<br>I<br>I | D                     | I <sup>2</sup> C Data (Bidirectional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21<br>22                                     | SDA<br>SCL<br>FB2                                                             | I/O<br>I<br>I | D<br>D                | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21<br>22<br>23<br>24                         | SDA<br>SCL<br>FB2<br>nRSTO                                                    |               | D D A D               | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21<br>22<br>23<br>24<br>25                   | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5                                       | <br>          | D D A D PWR           | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor LDO5 output                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21<br>22<br>23<br>24                         | SDA<br>SCL<br>FB2<br>nRSTO                                                    |               | D D A D               | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor LDO5 output Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separat                                                                                                                                                                                                                                                                                                                                     |

| 21<br>22<br>23<br>24<br>25<br>26             | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5 V <sub>IN</sub> LDO5                  |               | D D A D PWR PWR       | I <sup>2</sup> C Data (Bidirectional)  I <sup>2</sup> C Clock  Buck2 input feedback terminal  Reset output from the PMIC to the processor  LDO5 output  Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separat 1.8V supply.                                                                                                                                                                                                                                                                                                                   |

| 21<br>22<br>23<br>24<br>25<br>26             | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5 V <sub>IN</sub> LDO5                  |               | D D A D PWR PWR       | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor LDO5 output Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separal 1.8V supply. Analog Power for VREF, BIAS                                                                                                                                                                                                                                                                                            |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28 | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5 V <sub>IN</sub> LDO5 VDDA FB3         |               | D D A D PWR PWR PWR A | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor LDO5 output Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separal 1.8V supply. Analog Power for VREF, BIAS Buck3 Feedback                                                                                                                                                                                                                                                                             |

| 21<br>22<br>23<br>24<br>25<br>26             | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5 V <sub>IN</sub> LDO5 VDDA FB3 GPIO1 / |               | D D A D PWR PWR       | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor LDO5 output Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separat 1.8V supply. Analog Power for VREF, BIAS Buck3 Feedback General Purpose I/O / Ext. backup battery charger enable pin. This                                                                                                                                                                                                          |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28 | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5 V <sub>IN</sub> LDO5 VDDA FB3         |               | D D A D PWR PWR PWR A | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor LDO5 output Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separat 1.8V supply. Analog Power for VREF, BIAS Buck3 Feedback General Purpose I/O / Ext. backup battery charger enable pin. This pin enables the main battery / DC source power to charge the                                                                                                                                             |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28 | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5 V <sub>IN</sub> LDO5 VDDA FB3 GPIO1 / |               | D D A D PWR PWR PWR A | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor LDO5 output Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separat 1.8V supply. Analog Power for VREF, BIAS Buck3 Feedback General Purpose I/O / Ext. backup battery charger enable pin. This pin enables the main battery / DC source power to charge the backup battery. This pin toggled via the application processor. By                                                                          |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28 | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5 V <sub>IN</sub> LDO5 VDDA FB3 GPIO1 / |               | D D A D PWR PWR PWR A | I <sup>2</sup> C Data (Bidirectional)  I <sup>2</sup> C Clock  Buck2 input feedback terminal  Reset output from the PMIC to the processor  LDO5 output  Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separal 1.8V supply.  Analog Power for VREF, BIAS  Buck3 Feedback  General Purpose I/O / Ext. backup battery charger enable pin. This pin enables the main battery / DC source power to charge the backup battery. This pin toggled via the application processor. By grounding this pin the DC source continuously charges the backup |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28 | SDA SCL FB2 nRSTO V <sub>OUT</sub> LDO5 V <sub>IN</sub> LDO5 VDDA FB3 GPIO1 / |               | D D A D PWR PWR PWR A | I <sup>2</sup> C Data (Bidirectional) I <sup>2</sup> C Clock Buck2 input feedback terminal Reset output from the PMIC to the processor LDO5 output Power input to LDO5, this can be connected to V <sub>IN</sub> or to a separat 1.8V supply. Analog Power for VREF, BIAS Buck3 Feedback General Purpose I/O / Ext. backup battery charger enable pin. This pin enables the main battery / DC source power to charge the                                                                                                                                             |

# Pin Descriptions (Continued)

| Pin # | Name      | I/O | Туре | Description                                                                                                        |

|-------|-----------|-----|------|--------------------------------------------------------------------------------------------------------------------|

| 32    | SW3       | 0   | PWR  | Buck3 switcher output                                                                                              |

| 33    | PGND3     | G   | G    | Buck3 NMOS Power Ground                                                                                            |

| 34    | BGND1,2,3 | G   | G    | Bucks 1, 2 and 3 analog Ground                                                                                     |

| 35    | SYNC      | I   | D    | Frequency Synchronization: Connection to an external clock signal PLL to synchronize the PMIC internal oscillator. |

|       |           |     |      | Input Digital enable pin for the high voltage power domain supplies.                                               |

| 36    | SYS_EN    | I   | D    | Output from the Monahans processor.                                                                                |

|       |           |     |      | Digital enable pin for the Low Voltage domain supplies. Output                                                     |

| 37    | PWR_EN    | I   | D    | signal from the Monahans processor                                                                                 |

| 38    | PGND1     | G   | G    | Buck1 NMOS Power Ground                                                                                            |

| 39    | SW1       | 0   | PWR  | Buck1 Switcher output                                                                                              |

| 40    | VIN Buck1 | I   | PWR  | Battery input power to Buck1                                                                                       |

A: Analog Pin D: Digital Pin G: Ground Pin P: Power Pin I: Input Pin I/O: Input/Output Pin O: Output Pin Note: In this document active low logic items are prefixed with a lowercase "n"

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-0.3V to +6.5VAll Inputs GND to GND SLUG ±0.3V 150°C Junction Temperature (T<sub>J-MAX</sub>) Storage Temperature -65°C to +150°C Power Dissipation  $(T_A = 70^{\circ}C)$  (Note 3) 3.2W

Junction-to-Ambient Thermal

Resistance  $\theta_{JA}$  (Note 3) 25°C/W Maximum Lead Temp (Soldering) 260°C

ESD Rating (Note 5) Human Body Model 2 kV Machine Model 200V

### **Operating Ratings**

V<sub>IN</sub> LDO 4,5 2.7V to 5.5V  $V_{EN}$ 1.74 to (V<sub>IN</sub> -40°C to +125°C Junction Temperature (T<sub>J</sub>) Operating Temperature  $(T_A)$ -40°C to +85°C Maximum Power Dissipation

$(T_A = 70^{\circ}C)$  (Notes 3, 4) 2.2W

General Electrical Characteristics Typical values and limits appearing in normal type apply for  $T_{\rm J} = 25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $-40^{\circ}$ C to  $+125^{\circ}$ C. (Notes 2, 6)

| Symbol                                                 | Parameter                    | Conditions  | Min  | Тур | Max | Units |

|--------------------------------------------------------|------------------------------|-------------|------|-----|-----|-------|

| V <sub>IN</sub> , VDDA, V <sub>IN</sub> Buck1, 2 and 3 | Battery Voltage              |             | 2.7  | 3.6 | 5.5 | V     |

| V <sub>IN</sub> LDO4, V <sub>IN</sub> LDO5             | Power Supply for LDO 4 and 5 |             | 1.74 | 3.6 | 5.5 | V     |

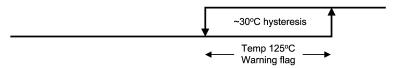

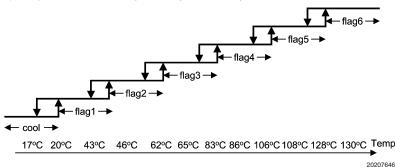

| T <sub>SD</sub>                                        | Thermal Shutdown (Note 14)   | Temperature |      | 160 |     | °C    |

|                                                        |                              | Hysteresis  |      | 20  |     | C     |

<sup>\*\*</sup>No input supply should be higher then VDDA

### Supply Specifications (Notes 2, 5)

|                               |                     |        | I <sub>MAX</sub>             |

|-------------------------------|---------------------|--------|------------------------------|

| Supply                        | V <sub>OUT</sub> (V | olts)  | Maximum Current              |

| Supply                        | Range Resolution    |        | Current (mA)                 |

|                               | (V)                 | (mV)   | Current (IIIA)               |

|                               |                     |        | 30 mA dc source 10 mA backup |

| LDO_RTC                       | 2.8V                | N/A    | source                       |

| LDO1 (V <sub>CC</sub> MVT)    | 1.7 to 2.0          | 25     | 300                          |

| LDO2                          | 1.8 to 3.3          | 100    | 150                          |

| LDO3                          | 1.8 to 3.3          | 100    | 150                          |

| LDO4                          | 1.0 to 3.3          | 50-600 | 150                          |

| LDO5 (V <sub>CC</sub> SRAM)   | 0.850 to 1.5        | 25     | 400                          |

| BUCK 1 (V <sub>CC</sub> APPS) | 0.725 to 1.5        | 25     | 1600                         |

| BUCK 2                        | 0.8 to 3.3          | 50-600 | 1600                         |

| BUCK 3                        | 0.8 to 3.3          | 50-600 | 1600                         |

# **General Electrical Characteristics** Typical values and limits appearing in normal type apply for $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation, $-40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ . (Notes 2, 6) (Continued)

# **Default Voltage Option** (Notes 2, 5)

| Version | LP3972SQ-A514 |      | LP3972S0  | Q-A413 |

|---------|---------------|------|-----------|--------|

| Enable  | Version A     |      | Version A |        |

| LDO_RTC | _             | 2.8  | _         | 2.8    |

| LDO1    | SYS_EN        | 1.8  | SYS_EN    | 1.8    |

| LDO2    | SYS_EN        | 1.8D | SYS_EN    | 1.8D   |

| LDO3    | SYS_EN        | 3D   | SYS_EN    | 3D     |

| LDO4    | SYS_EN        | 3D   | SYS_EN    | 2.8D   |

| LDO5    | PWR_EN        | 1.4  | PWR_EN    | 1.4    |

| BUCK1   | PWR_EN        | 1.4  | PWR_EN    | 1.4    |

| BUCK2   | SYS_EN        | 3.3  | SYS_EN    | 3      |

| BUCK3   | SYS_EN        | 1.8  | SYS_EN    | 1.8    |

| Version | LP3972SQ-E514 |      | LP3972    | SQ-1514 |  |  |  |

|---------|---------------|------|-----------|---------|--|--|--|

| Enable  | Version E     |      | Version I |         |  |  |  |

| LDO_RTC | _             | 2.8  | _         | 2.8     |  |  |  |

| LDO1    | SYS_EN        | 1.8  | SYS_EN    | 1.8     |  |  |  |

| LDO2    | SYS_EN        | 1.8E | SYS_EN    | 1.8E    |  |  |  |

| LDO3    | SYS_EN        | 3D   | SYS_EN    | 3E      |  |  |  |

| LDO4    | SYS_EN        | 3D   | SYS_EN    | 3E      |  |  |  |

| LDO5    | PWR_EN        | 1.4  | PWR_EN    | 1.4     |  |  |  |

| BUCK1   | PWR_EN        | 1.4  | PWR_EN    | 1.4     |  |  |  |

| BUCK2   | SYS_EN        | 3.3  | SYS_EN    | 3.3     |  |  |  |

| BUCK3   | SYS_EN        | 1.8  | SYS_EN    | 1.8     |  |  |  |

Note : E = Regulator is ENABLED during startup

D = Regulator is DISABLED during startup

### **LDO RTC**

Unless otherwise noted,  $V_{IN}=3.6V$ ,  $C_{IN}=1.0~\mu\text{F}$ ,  $C_{OUT}=0.47~\mu\text{F}$ ,  $C_{OUT}~(V_{RTC})=1.0~\mu\text{F}$  ceramic. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}\text{C}$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ . (Notes 2, 6, 7) and (Note 10)

| Symbol                             | Parameter                                                     | Conditions                                                                                | Min   | Тур | Max   | Units |

|------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| V <sub>OUT</sub><br>Accuracy       | Output Voltage Accuracy                                       | V <sub>IN</sub> Connected, Load Current = 1 mA                                            | 2.632 | 2.8 | 2.968 | V     |

| $\Delta V_{OUT}$                   | Line Regulation                                               | $V_{IN} = (V_{OUT} \text{ nom} + 1.0V) \text{ to } 5.5V$<br>(Note 11) Load Current = 1 mA |       |     | 0.15  | %/V   |

|                                    | Load Regulation                                               | From Main Battery Load Current = 1 mA to 30 mA                                            |       |     | 0.05  |       |

|                                    |                                                               | From Backup Battery $V_{IN} = 3.0V$<br>Load Current = 1 mA to 10 mA                       |       |     | 0.5   | %/mA  |

| I <sub>SC</sub>                    | Short Circuit Current Limit                                   | From Main Battery $V_{IN} = V_{OUT} + 0.3V \text{ to } 5.5V$                              |       | 100 |       | mA    |

| V <sub>IN</sub> - V <sub>OUT</sub> | Dropout Voltage                                               | From Backup Battery  Load Current = 10 mA                                                 |       | 30  | 375   | mV    |

| I <sub>Q</sub> _Max                | Maximum Quiescent Current                                     | I <sub>OUT</sub> = 0 mA                                                                   |       | 30  |       | μA    |

| TP1                                | RTC LDO Input Switched from<br>Main Battery to Backup Battery | V <sub>IN</sub> Falling                                                                   |       | 2.9 |       | V     |

| TP2                                | RTC LDO Input Switched from<br>Backup Battery to Main Battery | V <sub>IN</sub> Rising                                                                    |       | 3.0 |       | V     |

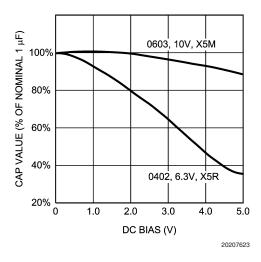

| Co                                 | Output Capacitor                                              | Capacitance for Stability                                                                 | 0.7   | 1.0 |       | μF    |

|                                    |                                                               | ESR                                                                                       | 5     |     | 500   | mΩ    |

### LDO 1 to 5

Unless otherwise noted,  $V_{IN}=3.6V$ ,  $C_{IN}=1.0~\mu F$ ,  $C_{OUT}=0.47~\mu F$ ,  $C_{OUT}~(V_{BTC})=1.0~\mu F$  ceramic. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $-40^{\circ}C$  to  $+125^{\circ}C$ . (Notes 2, 6, 7, 10, 11, 15) and (Note 16).

| Symbol            | Parameter                        | Conditions                                    | Min  | Тур  | Max   | Units |

|-------------------|----------------------------------|-----------------------------------------------|------|------|-------|-------|

| V <sub>OUT</sub>  | Output Voltage Accuracy (Default | Load Current = 1 mA                           | -3   |      | 3     | %     |

| Accuracy          | V <sub>OUT</sub> )               |                                               |      |      |       |       |

| $\Delta V_{OUT}$  | Line Regulation                  | V <sub>IN</sub> =3.1V to 5.0V, (Note 11) Load |      |      | 0.15  | %/V   |

|                   |                                  | Current = 1 mA                                |      |      |       |       |

|                   | Load Regulation                  | $V_{IN} = 3.6V,$                              |      |      | 0.011 | %/mA  |

|                   |                                  | Load Current = 1 mA to I <sub>MAX</sub>       |      |      |       |       |

| I <sub>SC</sub>   | Short Circuit Current Limit      | LDO1-4, V <sub>OUT</sub> = 0V                 |      | 400  |       | m A   |

|                   |                                  | LDO5, V <sub>OUT</sub> = 0V                   |      | 500  |       | mA    |

| V <sub>IN</sub> - | Dropout Voltage                  | Load Current = 50 mA (Note 7)                 |      |      | 150   | mV    |

| $V_{OUT}$         |                                  |                                               |      |      |       |       |

| PSRR              | Power Supply Ripple Rejection    | f = 10 kHz, Load Current = I <sub>MAX</sub>   |      | 45   |       | dB    |

| Ι <sub>Q</sub>    | Quiescent Current "On"           | I <sub>OUT</sub> = 0 mA                       |      | 40   |       |       |

|                   | Quiescent Current "On"           | $I_{OUT} = I_{MAX}$                           |      | 60   |       | μA    |

|                   | Quiescent Current "Off"          | EN is de-asserted                             |      | 0.03 |       | 1     |

| T <sub>ON</sub>   | Turn On Time                     | Start up from Shut-down                       |      | 300  |       | µsec  |

| Соит              | Output Capacitor                 | Capacitance for Stability                     | 0.33 | 0.47 |       |       |

|                   |                                  | 0°C ≤ T <sub>J</sub> ≤ 125°C                  |      |      |       | μF    |

|                   |                                  | –40°C ≤ T <sub>J</sub> ≤ 125°C                | 0.68 | 1.0  |       | 1     |

|                   |                                  | ESR                                           | 5    |      | 500   | mΩ    |

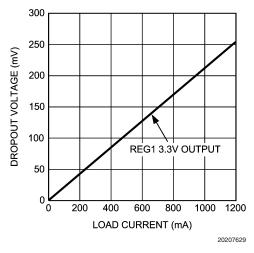

#### LDO dropout voltage vs. Load Current collect data for all LDO's

#### **Dropout Voltage vs. Load Current**

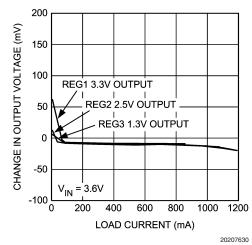

#### Change in Output Voltage vs. Load Current

### LDO 1 to 5 (Continued)

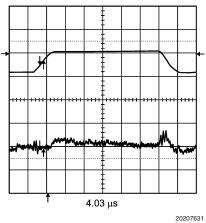

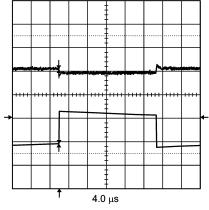

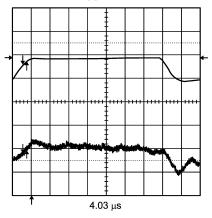

LDO1 Line Regulation  $V_{OUT} = 1.8 \text{ volts } V_{IN} \text{ 3 to 4 volts Load} = 100 \text{ mA}$

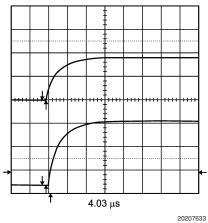

Enable Start-up time (LDO1)

LDO1 channel 2 LDO4 Channel 1 Sys\_enable from 0

volts Load = 100mA

20207632

### **Buck Converters SW1, SW2, SW3**

Unless otherwise noted,  $V_{IN}$  = 3.6V,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 10  $\mu$ F,  $L_{OUT}$  = 2.2  $\mu$ H ceramic. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40°C to +125°C. (Notes 2, 6, 12) and (Note 13).

| Symbol                | Parameter                     | Conditions                            | Min  | Тур | Max  | Units |

|-----------------------|-------------------------------|---------------------------------------|------|-----|------|-------|

| V <sub>OUT</sub>      | Output Voltage Accuracy       | Default V <sub>OUT</sub>              | -3   |     | +3   | %     |

| Eff                   | Efficiency                    | Load Current = 500 mA                 |      | 95  |      | %     |

| I <sub>SHDN</sub>     | Shutdown Supply Current       | EN is de-asserted                     |      | 0.1 |      | μA    |

|                       | Sync Mode Clock Frequency     | Synchronized from 13 MHz System Clock | 10.4 | 13  | 15.6 | MHz   |

| f <sub>osc</sub>      | Internal Oscillator Frequency |                                       |      | 2.0 |      | MHz   |

| I <sub>PEAK</sub>     | Peak Switching Current Limit  |                                       |      | 2.1 | 2.4  | А     |

| I <sub>Q</sub>        | Quiescent Current "On"        | No Load PFM Mode                      |      | 21  |      |       |

|                       |                               | No Load PWM Mode                      |      | 200 |      | μΑ    |

| R <sub>DSON</sub> (P) | Pin-Pin Resistance PFET       |                                       |      | 240 |      | mΩ    |

| R <sub>DSON</sub> (N) | Pin-Pin Resistance NFET       |                                       |      | 200 |      | mΩ    |

| T <sub>ON</sub>       | Turn On Time                  | Start up from Shut-down               |      | 500 |      | µsec  |

| C <sub>IN</sub>       | Input Capacitor               | Capacitance for Stability             | 8    |     |      | μF    |

| Co                    | Output Capacitor              | Capacitance for Stability             | 8    |     |      | μF    |

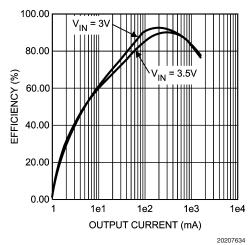

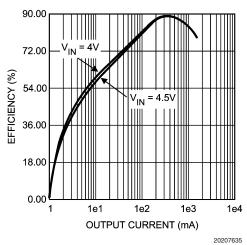

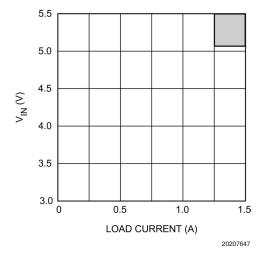

Buck 1 Output Efficiency vs. Load Current Varied from 1mA to 1.5 Amps

$V_{IN}$  = 3, 3.5 volts  $V_{OUT}$  = 1.4 volts Forced PWM

$V_{IN}$  = 3, 3.5 volts  $V_{OUT}$  = 1.4 volts Forced PWM

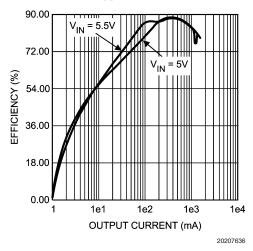

$V_{IN}$  = 4.0-4.5 volts  $V_{OUT}$  = 1.4 volts Forced PWM

20207637

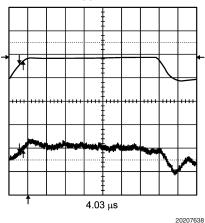

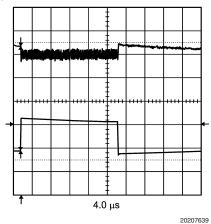

# Buck Converters SW1, SW2, SW3 (Continued)

20207638

14

### **Back-Up Charger Electrical Characteristics**

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $-40^{\circ}C$  to  $+125^{\circ}C$ . (Notes 2, 6) and (Note 8).

| Symbol           | Parameter                                       | Conditions                                                                                                        | Min  | Тур | Max | Units |

|------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| V <sub>IN</sub>  | Operational Voltage Range                       | Voltage at V <sub>IN</sub>                                                                                        | 3.3  |     | 5.5 | V     |

| Гоит             | Backup Battery Charging Current                 | V <sub>IN</sub> = 3.6V, Backup_Bat = 2.5V,<br>Backup Battery Charger Enabled<br>(Note 8)                          |      | 190 |     | μА    |

| V <sub>OUT</sub> | Charger Termination Voltage                     | V <sub>IN</sub> = 5.0V Backup Battery Charger<br>Enabled. Programmable                                            | 2.91 | 3.1 |     | V     |

|                  | Backup Battery Charger Short<br>Circuit Current | Backup_Bat = 0V, Backup Battery<br>Charger Enabled                                                                |      | 9   |     | mA    |

| PSRR             | Power Supply Ripple Rejection<br>Ratio          | $I_{OUT} \le 50 \ \mu A, \ V_{OUT} = 3.15 V$<br>$V_{OUT} + 0.4 \le V_{BATT} = V_{IN} \le 5.0 V$<br>$f < 10 \ kHz$ |      | 15  |     | dB    |

| IQ               | Quiescent Current                               | I <sub>OUT</sub> < 50 μA                                                                                          |      | 25  |     | μA    |

| C <sub>OUT</sub> | Output Capacitance                              | 0 μA ≤ I <sub>OUT</sub> ≤ 100 μA                                                                                  |      | 0.1 |     | μF    |

|                  | Output Capacitor ESR                            | 1                                                                                                                 | 5    |     | 500 | mΩ    |

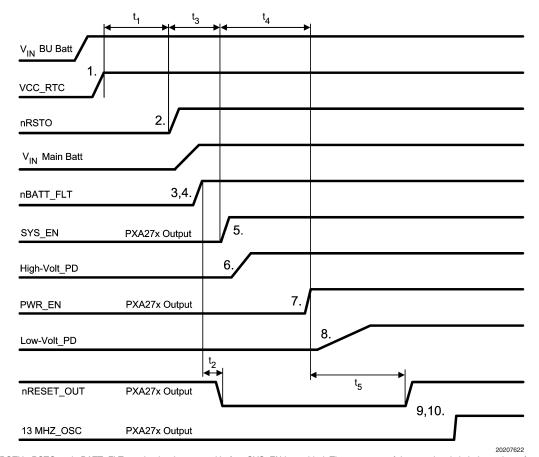

#### LP3972 BATTERY SWITCH OPERATION

The LP3972 has provisions for two battery connections, the main battery Vbat and Backup Battery

The function of the battery switch is to connect power to the RTC LDO from the appropriate battery, depending on conditions described below:

- If only the backup battery is applied, the switch will automatically connect the RTC LDO power to this battery.

- · If only the main battery is applied, the switch will automatically connect the RTC LDO power to this battery

- If both batteries are applied, and the main battery is sufficiently charged (Vbat > 3.1V), the switch will automatically connect the RTC LDO power to the main battery.

- As the main battery is discharged a separate circuit called nBATT\_FLT will warn the system. Then if no action is taken to restore the charge on the main battery, and discharging is continued the battery switch will disconnect the input of the RTC\_LDO from the main battery and connect to the backup battery.

- The main battery voltage at which the RTC LDO is switched over from main to backup battery is 2.8V typically.

- There is a hysteric voltage in this switch operation so; the RTC LDO will not be reconnected to main battery until main battery voltage is greater than 3.1V typically.

- The system designer may wish to disable the battery switch when only a main battery is used. This is accomplished by setting the "no back up battery bit" in the control register 8h'0B bit 7 NBUB. With this bit set to "1", the above described switching will not occur, that is the RTC LDO will remain connected to the main battery even as it is discharged below the 2.9V threshold. The Backup battery input should also be connected to main battery.

# Logic Inputs and Outputs DC Operating Conditions (Note 2)

Logic Inputs (SYS\_EN, PWR\_EN, SYNC, nRSTI, PWR\_ON, nTEST\_JIG, SPARE and GPI's)

| Symbol            | Parameter                   |                                                  | Conditions                                    | Min                       | Max                       | Units |       |

|-------------------|-----------------------------|--------------------------------------------------|-----------------------------------------------|---------------------------|---------------------------|-------|-------|

| V <sub>IL</sub>   | Low Level Input Voltage     |                                                  |                                               |                           |                           | 0.5   | V     |

| V <sub>IH</sub>   | High Level Input Voltage    |                                                  |                                               |                           | V <sub>RTC</sub><br>-0.5V |       | V     |

| I <sub>LEAK</sub> | Input Leakage Current       |                                                  |                                               |                           | -1                        | +1    | μΑ    |

| Logic O           | utputs (nRSTO, EXT_WAKEUP a | nd GPO                                           | 's)                                           |                           |                           |       | '     |

| Symbol            | Parameter                   |                                                  | Conditions                                    |                           | Min                       | Max   | Units |

| V <sub>OL</sub>   | Output Low Level            |                                                  | Load = +0.2 mA = I <sub>OL</sub> Max          |                           | 0.5                       | V     |       |

| V <sub>OH</sub>   | Output High Level           |                                                  | Load = $-0.1 \text{ mA} = I_{OL} \text{ Max}$ | V <sub>RTC</sub><br>-0.5V |                           | V     |       |

| I <sub>LEAK</sub> | Output Leakage Current      |                                                  | $V_{ON} = V_{IN}$                             |                           |                           | +5    | μΑ    |

| Logic O           | utput (nBATT_FLT)           |                                                  |                                               |                           |                           |       | •     |

| Symbol            | Parameter                   |                                                  | Conditions                                    | Min                       | Тур                       | Max   | Units |

|                   | nBATT_FLT Threshold Voltage | Programmable via Serial Interface Default = 2.8V |                                               | 2.4                       | 2.8                       | 3.4   | V     |

| V <sub>OL</sub>   | Output Low Level            | Load = $+0.4 \text{ mA} = I_{OL} \text{ Max}$    |                                               |                           |                           | 0.5   | V     |

| / <sub>OH</sub>   | Output High Level           |                                                  |                                               | V <sub>RTC</sub><br>-0.5V |                           |       | V     |

| I <sub>LEAK</sub> | Input Leakage Current       |                                                  |                                               |                           |                           | +5    | μΑ    |

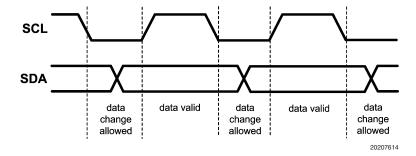

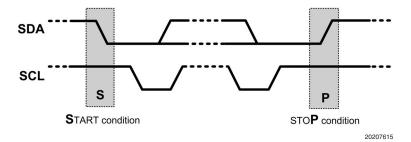

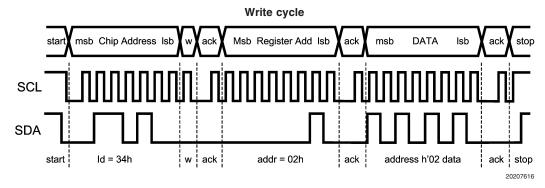

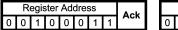

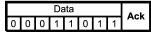

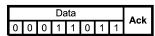

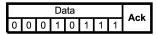

### I<sup>2</sup>C Compatible Serial Interface Electrical Specifications (SDA and SCL)

Unless otherwise noted,  $V_{IN} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $-40^{\circ}C$  to  $+125^{\circ}C$ . (Notes 2, 6) and (Note 9)

| Symbol               | Parameter                              | Conditions                       | Min                  | Тур | Max                  | Units |

|----------------------|----------------------------------------|----------------------------------|----------------------|-----|----------------------|-------|

| V <sub>IL</sub>      | Low Level Input Voltage                | (Note 14) -0.5                   |                      |     | 0.3 V <sub>RTC</sub> | V     |

| V <sub>IH</sub>      | High Level Input Voltage               | (Note 14)                        | 0.7 V <sub>RTC</sub> |     | V <sub>RTC</sub>     |       |

| V <sub>OL</sub>      | Low Level Output Voltage               | (Note 14)                        | 0                    |     | 0.2 V <sub>TRC</sub> |       |

| I <sub>OL</sub>      | Low Level Output Current               | V <sub>OL</sub> = 0.4V (Note 14) | 3.0                  |     |                      | mA    |

| F <sub>CLK</sub>     | Clock Frequency                        | (Note 14)                        |                      |     | 400                  | kHz   |

| t <sub>BF</sub>      | Bus-Free Time Between Start and Stop   | (Note 14)                        | 1.3                  |     |                      | μs    |

| t <sub>HOLD</sub>    | Hold Time Repeated Start Condition     | (Note 14)                        | 0.6                  |     |                      | μs    |

| t <sub>CLKLP</sub>   | CLK Low Period                         | (Note 14)                        | 1.3                  |     |                      | μs    |

| t <sub>CLKHP</sub>   | CLK High Period                        | (Note 14)                        | 0.6                  |     |                      | μs    |

| t <sub>SU</sub>      | Set Up Time Repeated Start Condition   | (Note 14)                        | 0.6                  |     |                      | μs    |

| t <sub>DATAHLD</sub> | Data Hold Time                         | (Note 14)                        | 0                    |     |                      | μs    |

| t <sub>CLKSU</sub>   | Data Set Up Time                       | (Note 14)                        | 100                  |     |                      | ns    |

| T <sub>SU</sub>      | Set Up Time for Start Condition        | (Note 14)                        | 0.6                  |     |                      | μs    |

| T <sub>TRANS</sub>   | Maximum Pulse Width of Spikes that     | (Note 14)                        |                      | 50  |                      | ns    |

|                      | Must be Suppressed by the Input Filter |                                  |                      |     |                      |       |

|                      | of Both DATA & CLK Signals             |                                  |                      |     |                      |       |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP = 125°C), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation: TA-MAX = TJ-MAX-OP - ( $\theta_{JA}$  x PD-MAX).

Note 4: Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51–7. The test board is a 4-layer FR-4 board measuring 102 mm x 76 mm x 1.6 mm with a 2x1 array of thermal vias. The ground plane on the board is 50 mm x 50 mm. Thickness of copper layers are  $36 \, \mu m/1.8 \, \mu m/18 \, \mu m/36 \, \mu m$  (1.5 oz/1 oz/1.5 oz). Ambient temperature in simulation is 22°C, still air. Power dissipation is 1W. Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design. The value of  $\theta_{JA}$  of this product can vary significantly, depending on PCB material, layout, and environmental conditions. In applications where high maximum power dissipation exists (high  $V_{IN}$ , high  $V_{IN}$ , high  $V_{IN}$ ), special care must be paid to thermal dissipation issues. For more information on these topics, please refer to *Application Note 1187: Leadless Leadframe Package (LLP) and the Power Efficiency and Power Dissipation* section of this datasheet.

Note 5: The Human body model is a 100 pF capacitor discharged through a 1.5 k ??? resistor into each pin. (MIL-STD-883 3015.7) The machine model is a 200 pF capacitor discharged directly into each pin. (EAIJ)

**Note 6:** All limits guaranteed at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are production tested, guaranteed through statistical analysis or guaranteed by design. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 7: Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value.

Note 8: Back-up battery charge current is programmable via the I<sup>2</sup>C compatible interface. Refer to the Application Section for more information.

Note 9: The  $I^2C$  signals behave like open-drain outputs and require an external pull-up resistor on the system module in the 2 k $\Omega$  to 20 k $\Omega$  range.

Note 10: LDO\_RTC voltage can track LDO3 voltage. LP3972 has a tracking function (nIO\_TRACK). When enabled, LDO\_RTC voltage will track LDO3 voltage within 200mV down to 2.8V when LDO3 is enabled

Note 11:  $V_{IN}$  minimum for line regulation values is 2.7V for LDOs 1–3 and 1.8V for LDOs 4 and 5. Condition does not apply to input voltages below the minimum input operating voltage.

Note 12: The input voltage range recommended for ideal applications performance for the specified output voltages is given below:

$V_{IN}$  = 2.7V to 5.5V for 0.80V <  $V_{OUT}$  < 1.8V

$V_{IN}$  = (V\_{OUT}+ 1V) to 5.5V for 1.8V  $\leq$   $V_{OUT} \leq$  3.3V

Note 13: Test condition: for  $V_{OUT}$  less than 2.7V,  $V_{IN} = 3.6V$ ; for  $V_{OUT}$  greater than or equal to 2.7V,  $V_{IN} = V_{OUT} + 1V$ .

Note 14: This electrical specification is guaranteed by design.

Note 15: An increase in the load current results in a slight decrease in the output voltage and vice versa.

Note 16: Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply for input voltages below 2.7V for LDOs 1–3 and 1.8V for LDOs 4 and 5.

### **Buck Converter Operation**

#### **DEVICE INFORMATION**

The LP3972 includes three high efficiency step down DC-DC switching buck converters. Using a voltage mode architecture with synchronous rectification, the buck converters have the ability to deliver up to 1600 mA depending on the input voltage, output voltage, ambient temperature and the inductor chosen.

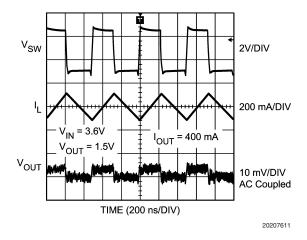

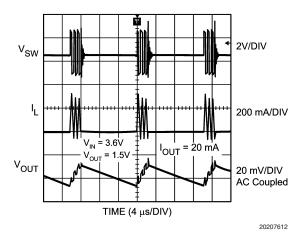

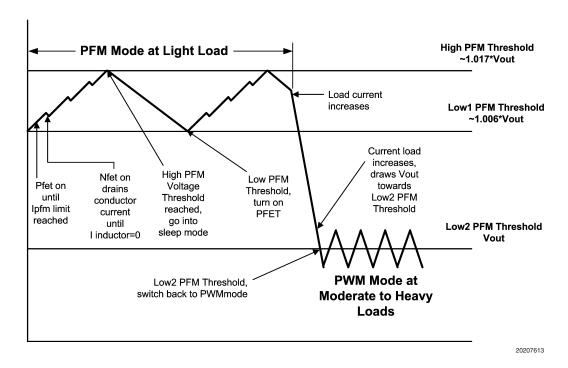

There are three modes of operation depending on the current required - PWM, PFM, and shutdown. The device operates in PWM mode at load currents of approximately 100 mA or higher, having voltage tolerance of  $\pm 3\%$  with 95% efficiency or better. Lighter load currents cause the device to automatically switch into PFM for reduced current consumption. Shutdown mode turns off the device, offering the lowest current consumption ( $I_{O,SHUTDOWN} = 0.01~\mu A$  typ).

Additional features include soft-start, under voltage protection, current overload protection, and thermal shutdown protection.

The part uses an internal reference voltage of 0.5V. It is recommended to keep the part in shutdown until the input voltage is 2.7V or higher.

#### **CIRCUIT OPERATION**

The buck converter operates as follows. During the first portion of each switching cycle, the control block turns on the internal PFET switch. This allows current to flow from the input through the inductor to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of  $(V_{IN}-V_{OUT})/L$ , by storing energy in a magnetic field.

During the second portion of each cycle, the controller turns the PFET switch off, blocking current flow from the input, and then turns the NFET synchronous rectifier on. The inductor draws current from ground through the NFET to the output filter capacitor and load, which ramps the inductor current down with a slope of  $-V_{\rm OUT}/L.$

The output filter stores charge when the inductor current is high, and releases it when inductor current is low, smoothing the voltage across the load.

The output voltage is regulated by modulating the PFET switch on time to control the average current sent to the load. The effect is identical to sending a duty-cycle modulated rectangular wave formed by the switch and synchronous rectifier at the SW pin to a low-pass filter formed by the inductor and output filter capacitor. The output voltage is equal to the average voltage at the SW pin.

#### **PWM OPERATION**

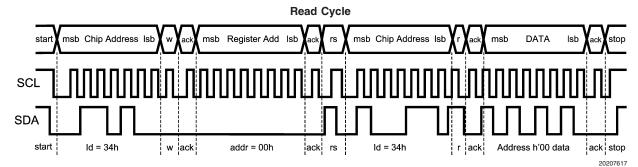

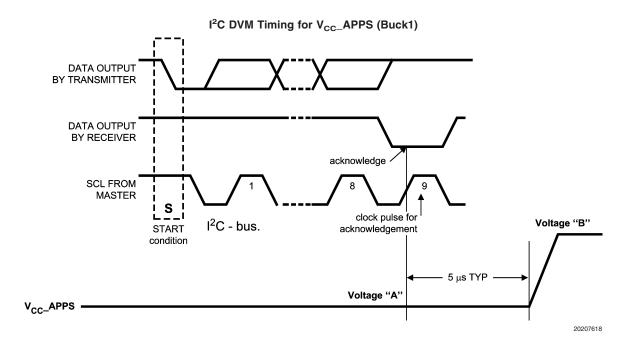

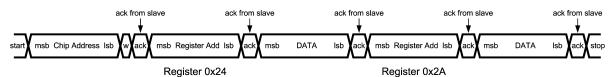

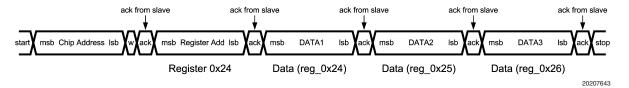

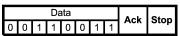

During PWM operation the converter operates as a voltage mode controller with input voltage feed forward. This allows the converter to achieve good load and line regulation. The DC gain of the power stage is proportional to the input voltage. To eliminate this dependence, feed forward inversely proportional to the input voltage is introduced.