### STw5095

# Low Power Asynchronous Stereo Audio Codec with Integrated Power Amplifiers

PRELIMINARY DATA

#### **Features**

- 20 bit audio resolution, 8kHz to 96kHz independent rate ADC and DAC

- Asynchronous sampling ADC and DAC: they do not require oversampled clock and information on the audio data sampling frequency (fs). Jitter tolerant fs

- Wide master clock range: from 4MHz to 32MHz

- I<sup>2</sup>C/SPI compatible control I/F

- Stereo headphones drivers, handsfree loudspeaker driver, line out drivers

- Mixable analog line inputs

- Voice filters: 8/16kHz with voice channel filters

- Automatic gain control for microphone and linein inputs

- Two programmable master/slave serial audio data interfaces (I<sup>2</sup>S, SPI, PCM compatible and other formats)

- Frequency programmable clock outputs

- Multibit ΣΔ modulators with data weighted averaging ADC and DAC

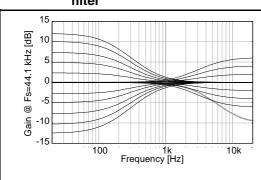

- DSP functions for bass-treble-volume control, mute, mono/stereo selection, voice channel filters, de-emphasis filter and dynamic compression.

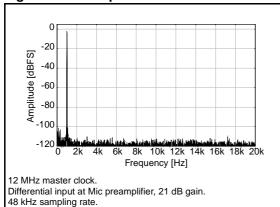

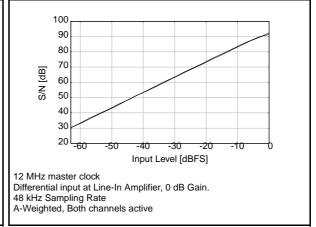

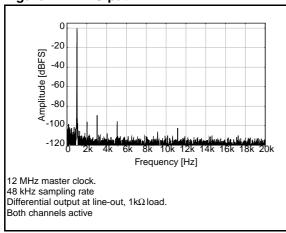

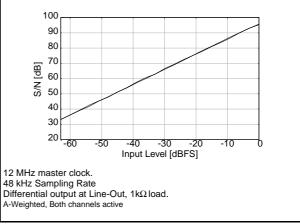

- 93 dB dynamic range ADC, 0.001% THD with full scale output @ 2.7V

- 95 dB dynamic range DAC, 0.02% THD performance @ 2.7V over 16Ω load

#### **Analog inputs**

November 2005

- Selectable stereo differential or single-ended microphone amplifier inputs with 51dB range programmable gain

- One microphone biasing output

- Microphone plug-in and push-button detection input

Selectable stereo differential or single-ended line inputs with 38 dB range programmable gain

#### Analog output drivers

- Stereo headphones outputs driving capability: 40 mW (0.1% THD) over 16Ω with 40 dB range programmable gain

- Common mode voltage headphones driver (phantom ground)

- Balanced loudspeaker output driving capability: up to 500mW (V<sub>CCLS</sub>>3.5V; 1% THD) over 8Ω with 30dB range programmable gain

- Transient supression filter during power up and power down

- Balanced/unbalanced stereo line outputs driving capability 1kΩ

### **Applications**

- Digital cellular telephones with mp3 player, stereo recorder, fm radio stereo listening and recording functions, live music recording

- Portable digital players and recorders

Rev 1.0 1/69

#### **Description**

STw5095 is a low power asynchronous stereo audio CODEC device with headphones amplifiers for high quality audio listening and recording.

The STw5095 control registers are accessed through a selectable I<sup>2</sup>C-bus compatible or SPI compatible interface.

The STw5095 asynchronous stereo audio CODEC is designed to easily fit in most audio systems because it supports an extended master clock range (any value between 4 MHz and 32 MHz) and at the same time it supports any audio data rate (independent in AD and DA paths) from 8 kHz to 48 kHz and from 88 kHz to 96 kHz, moreover it can tolerate jitter on audio data without degrading performance. The audio data serial interfaces (for AD and DA) can be Master or Slave, are I<sup>2</sup>S compatible and they support other formats that can easily interface to standard serial ports. The two audio interfaces can be used as a single bidirectional interface. Two frequency programmable clock sources are available to generate the master clock for the audio sub-system of other devices. The internal D to A and A to D converters work with up to 24 bit resolution.

The supply voltage can be the same for the whole device, in the range 2.4 V to 2.7 V, or it can be differentiated for digital ( $V_{CC}$ : 1.8 V to 2.7 V), analog ( $V_{CCA}$ : 2.4 V to 3.3 V) and loudspeaker driver ( $V_{CCLS}$ :  $V_{CCA}$  to 5.5 V) to obtain best performance and maximum power to the loudspeaker (up to 500 mW).

STw5095 has multiple analog mixable inputs and outputs. It can directly drive Stereo Headphones without external capacitors and it has a Loudspeaker driver that can also be used for monophonic group listening. Stereo differential and single ended microphones, auxiliary line in stereo and mono signals can be mixed and connected to the ADC or directly to the drivers, mixed also with DAC audio signals.

STw5095 stereo audio Codec main applications include multimedia handheld devices such as cellular phones with added low-power high-quality MP3 and/ or FM radio listening/recording features, or any battery powered equipment such as PDAs, Camcorders, etc. that require Stereo Audio Codec with Headphones drivers.

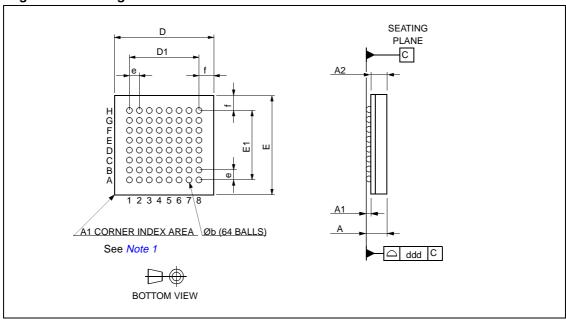

#### **Ordering codes**

| Part Number | Details                |

|-------------|------------------------|

| STw5095     | TFBGA 64 Tray          |

| STw5095T    | TFBGA 64 Tape and Reel |

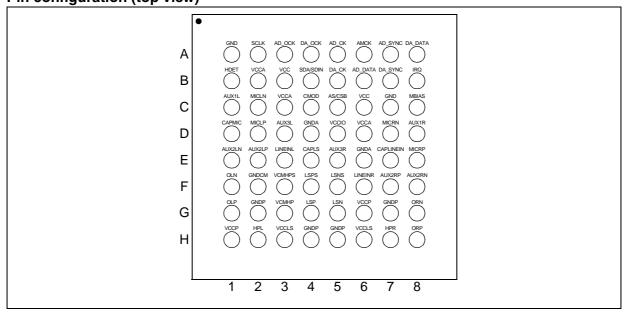

#### Pin configuration (top view)

**577**

### **Contents**

| 1 | Func  | ctional Block Diagram                                     | 6    |

|---|-------|-----------------------------------------------------------|------|

| 2 | Pin C | Description                                               | 7    |

| 3 | Func  | etional Description                                       | . 10 |

|   | 3.1   | Power supply                                              | . 10 |

|   | 3.2   | Device programming                                        | . 10 |

|   | 3.3   | Power up                                                  | . 12 |

|   | 3.4   | Master clock                                              | . 12 |

|   | 3.5   | Data rates                                                | . 13 |

|   | 3.6   | Clock generators and master mode function                 | . 13 |

|   | 3.7   | Audio digital interfaces                                  | . 14 |

|   | 3.8   | Analog inputs                                             | . 15 |

|   | 3.9   | Analog output drivers                                     | . 16 |

|   | 3.10  | Analog mixer                                              | . 17 |

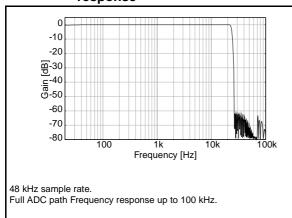

|   | 3.11  | AD path                                                   | . 17 |

|   | 3.12  | DA path                                                   | . 17 |

|   | 3.13  | Analog-only operation                                     | . 17 |

|   | 3.14  | Automatic Gain Control (AGC)                              | . 18 |

|   | 3.15  | Interrupt request: IRQ pin                                | . 18 |

|   | 3.16  | Headset plug-in and push-button detection                 | . 19 |

|   | 3.17  | Microphone biasing circuit                                | . 19 |

| 4 | Cont  | rol Registers                                             | . 20 |

|   | 4.1   | Summary                                                   | . 20 |

|   | 4.2   | Supply and power control                                  | . 21 |

|   | 4.3   | Gains                                                     | . 23 |

|   | 4.4   | DSP control                                               | . 27 |

|   | 4.5   | Analog functions                                          | . 30 |

|   | 4.6   | Digital audio interfaces master mode and clock generators | . 32 |

|   | 4.7   | Digital audio interfaces                                  | . 34 |

|   | 4.8   | Digital filters, software reset and master clock control  | . 36 |

|   |       |                                                           |      |

3/69

|    | 4.9   | Interrupt control and control interface SPI out mode | 37 |

|----|-------|------------------------------------------------------|----|

|    | 4.10  | AGC                                                  | 39 |

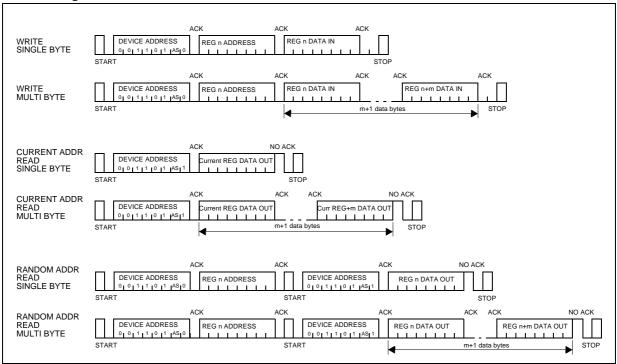

| 5  | Cont  | rol Interface and Master Clock                       | 11 |

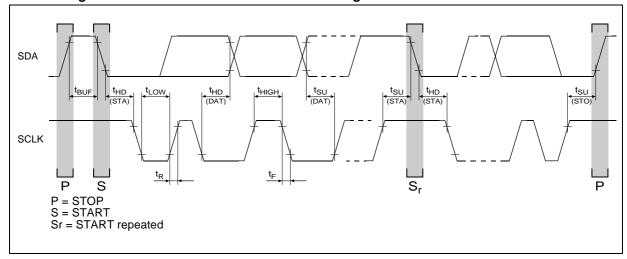

|    | 5.1   | Control interface I2C mode                           | 41 |

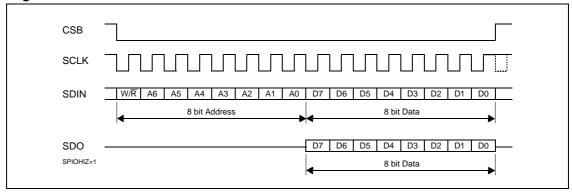

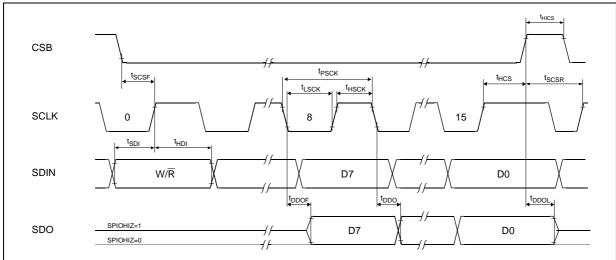

|    | 5.2   | Control interface SPI mode                           | 42 |

|    | 5.3   | Master clock timing                                  | 44 |

| 6  | Audi  | o Interfaces                                         | 15 |

| 7  | Timir | ng Specifications                                    | 19 |

| 8  | Oper  | rative Ranges                                        | 50 |

|    | 8.1   | Absolute maximum ratings                             | 50 |

|    | 8.2   | Operative supply voltage                             | 50 |

|    | 8.3   | Power Dissipation                                    | 51 |

|    | 8.4   | Typical power dissipation                            | 51 |

| 9  | Elect | trical Characteristics                               | 53 |

|    | 9.1   | Digital interfaces                                   | 53 |

|    | 9.2   | AMCK with sinusoidal input                           | 53 |

|    | 9.3   | Analog interfaces                                    | 54 |

|    | 9.4   | Headset plug-in and push-button detector             | 54 |

|    | 9.5   | Microphone bias                                      | 55 |

|    | 9.6   | Power supply rejection ratio                         | 55 |

|    | 9.7   | LS gain limiter                                      | 55 |

| 10 | Anal  | og Input/output Operative Ranges                     | 56 |

|    | 10.1  | Analog levels                                        | 56 |

|    | 10.2  | Microphone input levels                              | 56 |

|    | 10.3  | Line input levels                                    | 57 |

|    | 10.4  | Line output levels                                   | 57 |

|    | 10.5  | Power output levels HP                               | 58 |

|    | 10.6  | Power output levels LS                               | 58 |

#### STw5095

| 11 | Stereo Audio ADC Specifications                                | 59 |

|----|----------------------------------------------------------------|----|

| 12 | Stereo Audio DAC Specifications                                | 60 |

| 13 | AD to DA Mixing (Sidetone) Specifications                      | 61 |

| 14 | Stereo Analog-only Path Specifications                         | 61 |

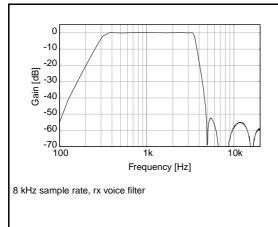

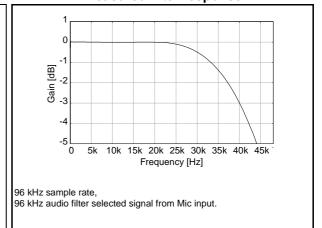

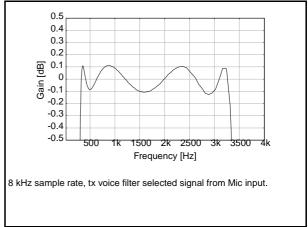

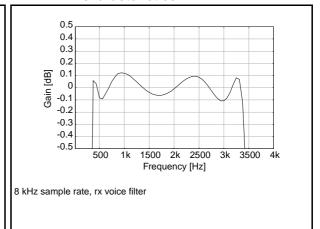

| 15 | ADC (TX) & DAC (RX) Specifications With Voice Filters Selected | 62 |

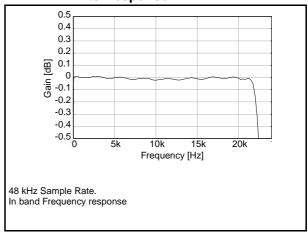

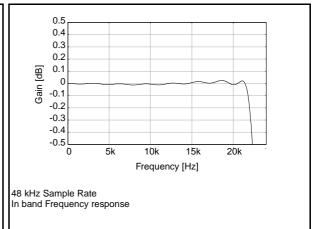

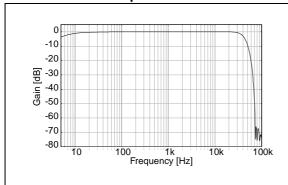

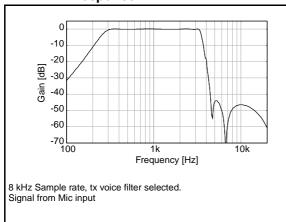

| 16 | Typical Performance Plots                                      | 63 |

| 17 | Application Schematics                                         | 66 |

| 18 | Package Outline                                                | 67 |

| 19 | Revision history                                               | 68 |

**5**//

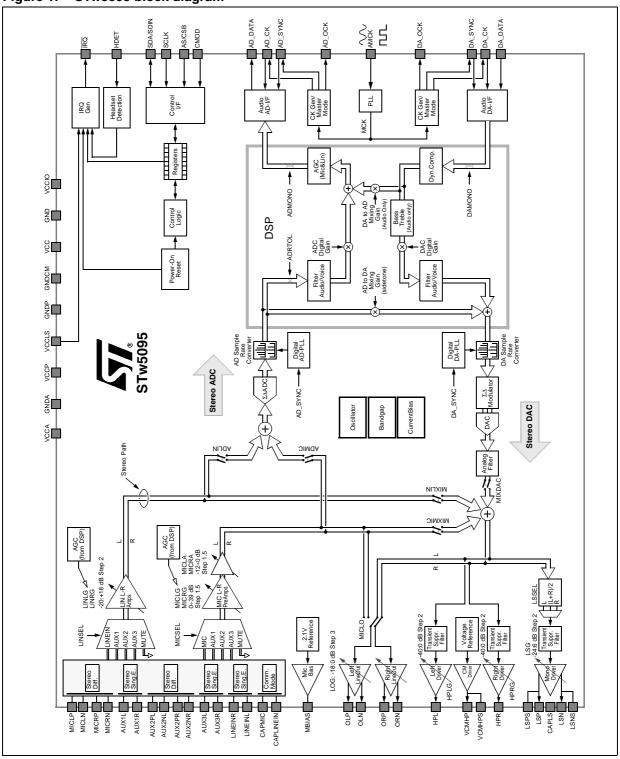

## 1 Functional Block Diagram

Figure 1. STw5095 block diagram

Note: This diagram shows the functionality of the device and of some control registers bits but it does not necessarily reflect the exact hardware implementation.

STw5095 2 Pin Description

## 2 Pin Description

Table 1. Pin description

| Table 1.             | Pin description                      | 1    |                                                                                                                                                                                                                                         |

|----------------------|--------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin N°               | Name                                 | Туре | Description                                                                                                                                                                                                                             |

| D2<br>C2<br>E8<br>D7 | MICLP<br>MICLN<br>MICRP<br>MICRN     | AI   | Left and Right channel differential pins for microphone input.                                                                                                                                                                          |

| C8                   | MBIAS                                | AO   | Microphone Biasing Pin. Fixed voltage reference.                                                                                                                                                                                        |

| D1                   | CAPMIC                               | Al   | A capacitor must be connected between CAPMIC and Ground.                                                                                                                                                                                |

| C1<br>D8             | AUX1L<br>AUX1R                       | Al   | Left and Right channel single ended pins for microphone or line input.                                                                                                                                                                  |

| E2<br>E1<br>F7<br>F8 | AUX2LP<br>AUX2LN<br>AUX2RP<br>AUX2RN | AI   | Left and Right channel differential pins for microphone or line input.                                                                                                                                                                  |

| D3<br>E5             | AUX3L<br>AUX3R                       | Al   | Left and Right channel single ended pins for microphone or line input.                                                                                                                                                                  |

| E3<br>F6             | LINEINL<br>LINEINR                   | Al   | Left and Right channel single ended pins for line input.                                                                                                                                                                                |

| E7                   | CAPLINEIN                            | Al   | A capacitor must be connected between CAPLINEIN and Ground.                                                                                                                                                                             |

| G4<br>G5             | LSP,<br>LSN                          | АО   | Analog differential loudspeaker amplifier output for Left channel or Right channel or the sum of both. This output can drive 50nF (with series resistor) or directly an earpiece transductor of $8\Omega$ ; It can deliver up to 500mW. |

| F4<br>F5             | LSPS,<br>LSNS                        | AO   | LSPS, LSNS (sense) pins must be connected on the application board to LSP, LSN pins respectively (see application note). The connection must be as close as possible to the pins.                                                       |

| E4                   | CAPLS                                | Al   | A capacitor can be connected between this node and Ground. See application notes                                                                                                                                                        |

| H2<br>H7             | HPL<br>HPR                           | АО   | Audio single ended headphones amplifier outputs for Left and Right channels. The outputs can drive 50nF (with series resistor) or directly an earpiece transductor of $16\Omega$                                                        |

| G3                   | VCMHP                                | АО   | Common mode voltage headphones output. The negative pins of headphones left and right speakers can be connected to this pin to avoid decoupling capacitors.                                                                             |

| F3                   | VCMHPS                               | АО   | VCMHPS (sense) pin must be connected on the application board to VCMHP pin (see application note). The connection must be as close as possible to the pins.                                                                             |

| G1<br>F1<br>H8<br>G8 | OLP<br>OLN<br>ORP<br>ORN             | AO   | Audio differential line out amplifier for Left and Right channels. This outputs can drive up to $1k\Omega$ resistive load. Can be used as single ended outputs.                                                                         |

**577**

2 Pin Description STw5095

Table 1. Pin description

| Table 1.             | Pin descriptio | n        |                                                                                                                                                     |

|----------------------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin N°               | Name           | Туре     | Description                                                                                                                                         |

| C4                   | CMOD           | DI       | Control interface type selector: I <sup>2</sup> C-bus mode or SPI mode.                                                                             |

| A2                   | SCLK           | DI       | Control interface serial clock input.                                                                                                               |

| B4                   | SDA/SDIN       | DIOD     | Control interface serial data input-output in I <sup>2</sup> C mode (SDA),<br>Control interface serial data input in SPI mode (SDIN).               |

| C5                   | AS/CSB         | DI       | Control interface address select in I <sup>2</sup> C mode (AS). Interface enable signal in SPI mode (CSB).                                          |

| A7                   | AD_SYNC        | DIO      | Frame Sync for stereo A/D converter.                                                                                                                |

| B7                   | DA_SYNC        | DIO      | Frame Sync for stereo D/A converter.                                                                                                                |

| A5                   | AD_CK          | DIO      | Serial Data Clock for stereo A/D converter.                                                                                                         |

| B5                   | DA_CK          | DIO      | Serial Data Clock for stereo D/A converter.                                                                                                         |

| B6                   | AD_DATA        | DO       | Serial Data Out for stereo A/D converter.                                                                                                           |

| A8                   | DA_DATA        | DI       | Serial Data In for stereo D/A converter.                                                                                                            |

| B1                   | HDET           | Al       | Headset detection input (Microphone Plug-in and Push-Button detection).                                                                             |

| B8                   | IRQ            | DO       | Programmable Interrupt output. Active low signal.                                                                                                   |

| A3                   | AD_OCK         | DO       | Oversampled Clock Out from AD clock generator.                                                                                                      |

| A4                   | DA_OCK         | DO       | Oversampled Clock Out from DA clock generator.                                                                                                      |

| A6                   | AMCK           | DI<br>AI | Master Clock Input. Accepted range 4 MHz to 32 MHz.  AMCK is a Digital square wave  AMCK is an Analog sinewave (see AMCKSIN Section 4.8 on page 36) |

| B2<br>C3<br>D6       | VCCA           | Р        | Power Supply pins for the analog section. Standard Operating range: from 2.7 V to 3.3 V Low Voltage (LV) Range: from 2.4 V to 2.7 V                 |

| D4<br>E6             | GNDA           | Р        | Ground pins for the analog section.                                                                                                                 |

| F2                   | GNDCM          | Р        | Ground pin for analog reference. GNDCM can be connected to GNDA.                                                                                    |

| G6<br>H1             | VCCP           | Р        | Power Supply pins for the left and right output drivers (headphones and line-out).  Operating range: from V <sub>CCA</sub> to 3.3V                  |

| H3<br>H6             | VCCLS          | Р        | Power Supply pins for the mono differential output driver.  Operating range: from V <sub>CCA</sub> to 5.5V                                          |

| G2<br>G7<br>H4<br>H5 | GNDP           | Р        | Ground pins for the left, right and mono-differential output drivers.  GNDP and GNDA must be connected together.                                    |

| B3<br>C6             | VCC            | Р        | Power Supply pins for the digital section.  Operating range: from 1.71 V to 2.7 V                                                                   |

STw5095 2 Pin Description

Table 1. Pin description

| Pin N°   | Name  | Туре | Description                                                                                                             |

|----------|-------|------|-------------------------------------------------------------------------------------------------------------------------|

| A1<br>C7 | GND   | Р    | Ground pins for the digital section.                                                                                    |

| D5       | VCCIO | Р    | Power Supply pin for the Digital I/O buffers.  Operating ranges: from 1.2 V to 1.8 V and from 1.71 V to V <sub>CC</sub> |

Note: VCC, VCCA, VCCP, VCCLS can be connected together for low cost applications: Operating range: 2.4 V-2.7 V.

#### Type definitions

AI - Analog input

AO - Analog Output

AIO - Analog Input Output

DI - Digital Input

DO - Digital output

DIO - Digital Input Output

DIOD - Digital Input Output Open Drain

P - Power Supply or Ground

3 Functional Description STw5095

### 3 Functional Description

#### 3.1 Power supply

STw5095 can have different supply voltages for different blocks, to optimize performance, power consumption and connectivity. See *Operative supply voltage on page 50* for voltage definition.

The correct sequence to apply supply voltage is to set first (and unset last) the digital I/O supply ( $V_{CCIO}$ ). The other supply voltages can be set in any order and can be disconnected individually, if needed. Disconnection does not cause any harm to the device and no extra current is pulled from any supply during this operation. Moreover if a voltage conflict is detected, like  $V_{CCA} < V_{CC}$  (not allowed), simply all blocks connected to  $V_{CCA}$  are set to power down and no extra current is pulled from supply.

When  $V_{CCIO}$  is set and  $V_{CC}$  (digital supply) is not set, all the digital output pins are in high impedance state, while the digital inputs are disconnected to avoid power consumption for any input voltage value between GND and  $V_{CCIO}$ . Before  $V_{CC}$  is disconnected the device has to be reset (SWRES bit in CR30).

When the analog supply  $(V_{CCA})$  is set and  $V_{CC}$  is not set, all the analog inputs are in high impedance state.

The control registers are powered by VCC pin (digital supply) so if this pin is disconnected all the information stored in control registers is lost. When the digital supply voltage is set, a power-on-reset (POR) circuit sets all the registers content to the default value and then generates an IRQ signal writing 1 in bits PORMSK and POREV in CR31 and CR32 respectively.

All supplies must be on during operation.

### 3.2 Device programming

STw5095 can be programmed by writing Control Registers with SPI or I<sup>2</sup>C compatible control interface (both slave). The interface is always active, there is no need to have the master clock running to program the device registers.

The choice between the two interfaces is done via an input pin (CMOD):

1. CMOD connected to GND: I<sup>2</sup>C compatible mode selected The device address is selected with AS pin:

AS connected to GND: chip address 00110101(35hex) for reading, 00110100 (34hex) for writing AS connected to  $V_{CCIO}$ : chip address 00110111(37hex) for reading, 00110110 (36hex) for writing

When this mode is selected control registers are accessed through pins:

SCLK (clock)

SDA (serial data out/in, open drain)

CMOD connected to V<sub>CCIO</sub>: SPI compatible mode selected

When this mode is selected control registers are accessed through:

CSB (chip select, active low)

SCLK (clock)

SDIN (serial data in)

AD\_OCK or DA\_OCK or IRQ (serial data out, if selected)

**Device Programming:** I<sup>2</sup>C. The I<sup>2</sup>C Control Interface timing is shown in *Section 5.1 on page 41*. The interface has an internal counter that keeps the current address of the control register to be read or written. At each write access of the interface the address counter is loaded with the data of the *register address* field. The value in the address counter is increased after each data byte read or write. It is possible to access the interface in 2 modes: single-byte mode in which the address and data of a single register are specified, and multi-byte mode in which the address of the first register to be written or read is specified and all the following bytes exchanged are the data of successive registers starting from the one specified (in multi-byte mode the internal address counter restart from register 0 after the last register 36). Using the multi-byte mode it is possible to write or read all the registers with a single access to the device on the I<sup>2</sup>C bus.

**Device Programming: SPI.** The SPI Control Interface timing is shown in *Section 5.2 on page 42*. Bits SPIOSEL (SPI Output Select) in CR33 control the out pin selection for serial data out (none, AD\_OCK, DA\_OCK or IRQ), while bit SPIOHIZ=1 in CR33 selects the high impedance state of serial data out pin when idle. The first bit sent on SDIN, after CSB falling edge, sets the interface for writing (SDIN=1) or reading (SDIN=0), then a 7-bit Control Register address follows.

If the interface is set for writing then the last 8 bits on SDIN are written in the control register. If the interface is set for reading then after the 7 bit address STw5095 sends out 8 bits data on the pin selected with bits SPIOSEL in CR33, while bits present at SDIN pin are ignored. If SPIOSEL=00 (no out pin selected) the reading access on SPI interface can still be useful to clear the IRQ event bits in CR32.

STw5095 3 Functional Description

#### 3.3 Power up

STw5095 internal blocks can individually be switched on and off according to the user needs. A general Power Up bit is present at bit 7 of CR0. See the following drawing to select the needed block for the desired function. A fast-settling function is activated to guickly charge external capacitors when the device is switched on (CAPLS, CAPLINEIN and CAPMIC).

**POWERUP** ENHSD MBIAS ENMIC STw5095 ENADCL + ENLINL ENADCKGEN ENLINR ADMAST ENADOCK ENLOL AUDIO I/F ENDAOCH DAMAST ENHP ENMIX ENLS ENDACL ENDACKGEN ENDACR ENHPR ENLOR **ENHPVCM**

Power up block diagram Figure 2.

#### 3.4 **Master clock**

The master clock pin (AMCK) accepts any frequency from 4 MHz to 32 MHz. The 4-32 MHz range is divided in sub-ranges that have to be programmed in bits CKRANGE in CR30. The jitter and spectral properties of this clock have a direct impact on the DAC and ADC performance because it is used to directly or by integer division drive the continuous-time to sampled-time interfaces.

Note that AMCK clock des not need to have any relation to any other digital or analog input or output.

STw5095 3 Functional Description

AMCK can be either a squarewave or a sinewave, bit AMCKSIN in CR30 selects the proper input mode. When a sinewave is used as input, AMCK pin must be decoupled with a capacitor. Specification for sinusoidal input can be found in *Section 9.2: AMCK with sinusoidal input on page 53*.

The AMCK clock is not needed when only analog functions are used. For this purpose an internal oscillator with no external components can be used to operate the device (see *Analog-only operation on page 17*).

#### 3.5 Data rates

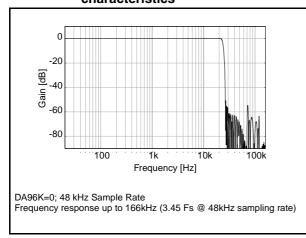

STw5095 supports any data rate in 2 ranges: 8 kHz to 48 kHz and 88 kHz to 96 kHz. The range is selected with bits DA96K and AD96K in CR29 for AD and DA paths respectively.

Note: When AD96K=1 it is required to have DA96K=1.

The rates are fully independent in A/D and D/A paths. Moreover the rates do not have to be specified to the device and they can change on the fly, within one range, while data is flowing.

The 2 audio data interfaces (for A/D and D/A) can independently operate in master or slave mode.

#### 3.6 Clock generators and master mode function

STw5095 provides 2 internal clock generators that can drive, if needed, the audio interfaces (master mode), and/or two independent master clocks.

The AMCK clock input frequency is internally raised via a PLL to obtain a clock (MCK) in the range 32 MHz to 48 MHz. The ratio MCK/AMCK is defined in CR30 (see MCKCOEFF in Section 4.6 on page 32).

MCK is used to obtain, by fractional division, the oversampled clock (OCK), word clock (SYNC) and bit clock (CK), that will therefore have edges aligned with MCK (the OCK period can have iitter of 1 MCK period).

The frequency of OCK, SYNC and CK is set with DAOCKF in CR21/20 for DA interface, and ADOCKF in CR24/23 for AD interface.

The ratio between OCK and SYNC clocks is selected with bit DAOCK512 in CR22 for DA interface and bit ADOCK512 in CR25 for AD interface. The ratio between CK and SYNC clocks depends on the selected interface format (see *Audio digital interfaces* paragraph below). Note that SPI format can only be slave.

The ADOCK and DAOCK output clocks are activated by bits ENADOCK and ENDAOCK respectively, while master mode generation is activated with two bits: first ADMAST (DAMAST) sets ADSYNC and ADCK (DASYNC and DACK) pins as outputs, then ADMASTGEN (DAMASTGEN) generates the SYNC and CK clocks. The logical value at SYNC and CK pins before data generation depends on the interface selected format.

See description of CR20 to CR25 for further details.

3 Functional Description STw5095

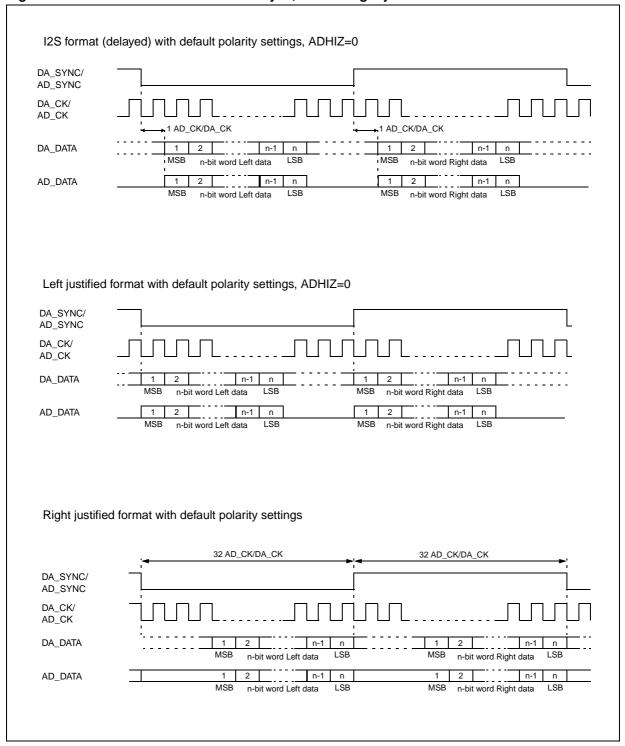

### 3.7 Audio digital interfaces

Two separate audio data interfaces are provided for AD and DA paths to have maximum flexibility in communicating with other devices. The 2 interfaces can have different rates and can work in different formats and modes (i.e AD interface can be 8 kHz PCM slave while DA is 44.1 kHz I<sup>2</sup>S master).

The pins used by the interfaces are:

AD\_SYNC, AD\_CK and AD\_DATA for AD path word clock, bit clock and data, respectively, and DA\_SYNC, DA\_CK and DA\_DATA for DA path word clock, bit clock and data, respectively.

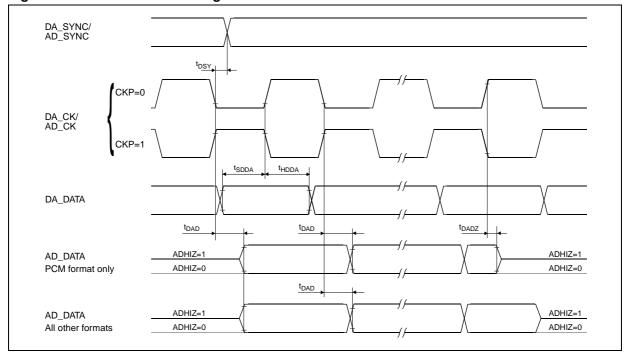

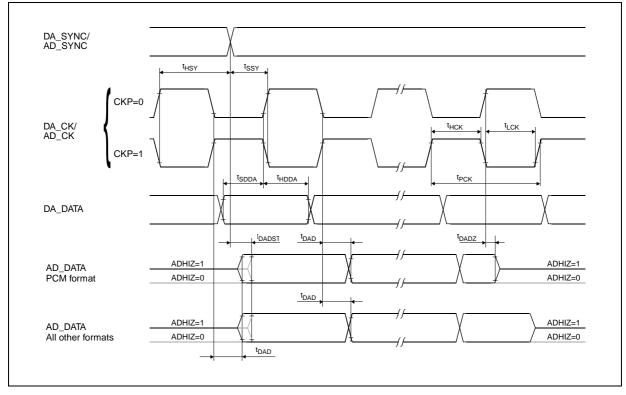

Data is exchanged with MSB first and left channel data first in all formats. Data word-length is selected with bits DAWL in CR26 and ADWL in CR27. AD\_DATA pin, outside the selected time slot, is in the impedance condition selected by bit ADHIZ in CR28 in all data formats except Right-Aligned-Format.

In the following paragraphs SYNC, CK and DATA will be used when the distinction between AD and DA is not relevant. When Master Mode is selected (bits DAMAST and ADMAST in CR22 and CR25 respectively) the SYNC and CK clocks are generated internally. In addition, an oversampled clock can be generated for each interface (AD\_OCK and DA\_OCK). The OCK clock is available in Slave Mode also, if needed.

The AD and DA interfaces can also be used as a single bidirectional interface when they are configured with the same format (Delayed, DSP, etc.) and AD\_SYNC is connected to DA\_SYNC and DA\_CK to AD\_CK. Master Mode is still available selecting ADMAST or DAMAST (not both).

The interfaces features are controlled with control registers CR26, CR27 and CR28.

Supported operating formats:

- Delayed-Format (I<sup>2</sup>S compatible) (DAFORM or ADFORM =000): the Audio Interface is I<sup>2</sup>S compatible (*Figure 8 on page 45*). The number of CK periods within one SYNC period is not relevant, as long as enough CK periods are used to transfer the data and the maximum frequency limit specified for bit clock is not exceeded. CK can be either a continuous clock or a sequence of bursts. In master mode there are 32 CK periods per SYNC period (that means 16 CK periods per channel) when the word length is 16 bit, while there are 64 CK periods per SYNC period (or 32 CK periods per channel) when word length is 18bit or higher. Bits ADSYNCP, DASYNCP and ADCKP, DACKP affect the interface format inverting the polarity of SYNC and CK pins respectively.

- **Left-Aligned-Format** (DAFORM or ADFORM =001): this format is equivalent to Delayed-Format without the 1 bit clock delay at the beginning of each frame (*Figure 8 on page 45*).

- **Right-Aligned-Format** (DAFORM or ADFORM =010): this format is equivalent to Delayed-Format, except that the Audio Data is right aligned and that the number of CK periods is fixed to 64 for each SYNC period (*Figure 8 on page 45*).

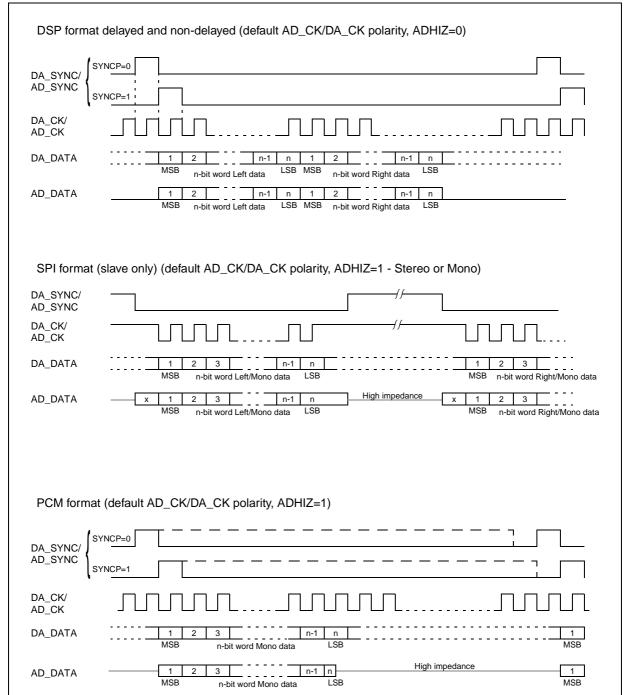

- DSP-Format (DAFORM or ADFORM =011) in this format the Audio Interface starting from a frame sync pulse on SYNC receives (DA) or sends (AD) the Left and Right data one after the other (Figure 9 on page 46). The number of CK periods within one SYNC period is not relevant, as long as enough CK periods are used to transfer the data and the maximum frequency limit specified for bit clock is not exceeded. CK can be either a continuous clock or a sequence of bursts. In Master Mode there are 32 CK periods per SYNC period when the word length is 16 bit, while there are 64 CK periods per SYNC period when word length is 18bit or higher. Bit CKP (ADCKP and DACKP) affects the interface format inverting the polarity of CK pin. Bit SYNCP (ADSYNCP and DASYNCP) switches between

delayed (SYNCP=0) and non delayed (SYNCP=1) formats. DSP-Format is suited to interface with a Multi-Channel Serial Port.

- SPI-Format (DAFORM or ADFORM =100) in this format Left and Right data is received with separate data burst. Every burst is identified with a low level on SYNC signal (Figure 9 on page 46). There is no timing difference between the Left and Right data burst: the two channels are identified by the startup order: the first burst after AD path or DA path power-up identifies the Left channel data, the second one is the Right channel data, then Left and Right data repeat one after the other. CK must have 16 periods per channel in case of 16 bit data word and 32 periods per channel in case of 18 bit to 32 bit data word. The SPI interface can be configured as a single-channel (mono) interface with bit SPIM (ADSPIM and DASPIM). The mono interface always exchanges the left channel sample. SPI-Format can only be Slave: if Master Mode is selected the CK and SYNC pins are set to 0. Bit CKP (ADCKP and DACKP) affects the interface format inverting the polarity of CK pin.

- PCM-Format (DAFORM or ADFORM =111): this format is monophonic, as it can only receive (DA) and transmit (AD) single channel data (*Figure 9 on page 46*). It is mainly used when voice filters are selected. If audio filters are used then the same sample is sent from DA-PCM interface to both channel of DA path, and the left channel sample from AD path is sent to AD-PCM interface. If in the AD path the right channel has to be sent to the PCM interface then the following must be set: ADRTOL=1 (CR27) and ENADCL=0 (CR1). In Master Mode the number of CK periods per SYNC period is between 16 and 512 (see DAPCMF in CR22 and ADPCMF in CR25, *Section 4.6 on page 32* for details). Bit CKP (ADCKP and DACKP) affects the interface format inverting the polarity of CK pin. Bit SYNCP (ADSYNCP and DASYNCP) switches between delayed (SYNCP=0) and non delayed (SYNCP=1) formats.

### 3.8 Analog inputs

STw5095 has a stereo Microphone preamplifier and a stereo Line In amplifier, with inputs selectable among 5: MIC (for Microphone preamplifier only), LINEIN (for Line In amplifier only) and 3 different AUX inputs (for Microphone and Line In amplifiers). The AUX inputs can be used simultaneously for Line In amplifiers and Microphone preamplifiers.

- Microphone preamplifier: it has a very low noise input, specifically designed for low amplitude signals. For this reason it has a high input gain (up to 39 dB) keeping a constant 50 kΩ input impedance for the whole gain range. However it can also be used as a line in preamplifier because it can accept a high dynamic input signal (up to 4 V<sub>pp</sub>). There are two separate gain and attenuation stages in order to improve the S/N ratio when the preamplifier output range is below full scale (volume control). The gain and attenuation controls are separate for left and right channel (CR3 and CR4 respectively). The Preamplifier input is selected with bits MICSEL in CR18, and it is disconnected when MICMUTE=1. If a single ended input is selected then the preamplifier uses the selected pin as the positive input and connects the negative input (for both left and right channels) to CAPMIC pin, which has to be connected through a capacitor to a low noise ground (typically the same reference ground of the input).

- The stereo Microphone preamplifier is powered up with bits ENMICL and ENMICR in CR1.

- Line In amplifier: it is designed for high level input signal. The input gain is in the range

-20 dB up to 18 dB. The Line In amplifier input is selected with bits LINSEL in CR18, and it

is disconnected when LINMUTE=1. If a single ended input is selected then the amplifier

uses the selected pin as the positive input and connects the negative input (for both left

and right channels) to CAPLINEIN pin, which has to be connected through a capacitor to a

3 Functional Description STw5095

low noise ground (typically the same reference ground of the input).

The stereo Line In amplifier is powered up with bits ENLINL and ENLINR in CR1.

### 3.9 Analog output drivers

STw5095 provides 3 different analog signal outputs and 1 common mode reference output:

- Line Out Drivers: it is a stereo differential output, it can be used as single-ended output just by using the positive or negative pin. It can drive 1 kΩ resistive load. The load can be connected between the positive and negative pins or between one pin and ground through a decoupling capacitor. The output gain is regulated with LOG bits in CR7, in the range 0 to -18 dB, simultaneously for left and right channels. When used as a single ended output the effective gain is 6 dB lower. It is muted with bit MUTELO in CR19. The input signal of this stereo output can come from the analog mixer or directly from MIC preamplifiers. The output Common Mode Voltage level is controlled with bits VCML in CR19. The supply voltage of line out drivers is V<sub>CCP</sub>.

- The Line Out Drivers are powered up with bits ENLOL and ENLOR in CR1. The output pins are in high impedance state with a  $180k\Omega$  pull-down resistor when the Line Out Drivers are powered down.

- Headphones Drivers: it is a stereo single ended output. It can drive 16 Ohm resistive load and deliver up to 40 mW. The output gain is regulated with HPLG and HPRG bits in CR8 and CR9 respectively, with a range of -40 to 6 dB. It is muted with bit MUTEHP in CR19. The input signal of this stereo output comes from the analog mixer. The output Common Mode Voltage is controlled with bits VCML in CR19. The supply voltage of headphones drivers is V<sub>CCP</sub>.

- The Headphones Drivers are powered up with bits ENHPL and ENHPR in CR2. The output pins are in high impedance state when the Headphones Drivers are powered down.

- Common Mode Voltage Driver: it is a single ended output with output voltage value selectable with bits VCML in CR19, from 1.2 V to 1.65 V in steps of 150 mV. The output voltage should be set to the value closest to V<sub>CCP</sub>/2 to optimize output drivers performance. The Common Mode Voltage Driver is designed to be connected to the common pin of stereo headphones, so that decoupling capacitors are not needed at HPL and HPR outputs. The supply voltage of the common mode voltage driver is V<sub>CCP</sub>. The Common Mode Voltage Driver is powered up with bit ENHPVCM in CR2. The output pin is in high impedance state when the Common Mode Voltage Driver is powered down.

- Loudspeaker Driver: it is a monophonic differential output. It can drive 8 Ω resistive load and deliver up to 500 mW to the load. The output gain is regulated with LSG bits in CR7, in the range -24 to +6 dB. The input signal of the loudspeaker driver comes from the analog mixers: bits LSSEL in CR29 select left channel, right channel, (L+R)/2 (mono) or mute. The output Common Mode Voltage is obtained with an internal voltage divider from V<sub>CCLS</sub> and it is connected to CAPLS pin. The supply voltage of the loudspeaker driver is V<sub>CCLS</sub>. The Loudspeaker Driver is powered up with bit ENLS in CR2. The output pin is in high impedance state when the Loudspeaker Driver is powered down.

#### Note: Note on direct connection of V<sub>CCLS</sub> To the battery:

The voltage of batteries of handheld devices during charging is usually below 5.5 V, making  $V_{CCLS}$  supply pin suitable for a direct connection to the battery. In this case if STw5095 is delivering the maximum power to the load and the ambient temperature is above 70 °C then the simultaneous charging of the battery can overheat the device. A basic protection scheme is implemented in STw5095 (activated with bit LSLIM in CR19): it limits the maximum gain of the

STw5095 3 Functional Description

loudspeaker to -6 dB when  $V_{CCLS}$  is above 4.2 V, and it removes the limit for  $V_{CCLS}$  below 4.0 V. The loudspeaker gain is left unchanged if it is set below -6 dB with bits LSG. This event ( $V_{CCLS} > 4.2$  V) can generate, if enabled (bit VLSMSK in CR31), an IRQ signal.

#### 3.10 Analog mixer

STw5095 can send to the output drivers the sum of stereo audio signals from 3 different sources, DA path (bit MIXDAC in CR17), Microphone Preamplifiers (bit MIXMIC in CR17) and Line In Amplifiers (bit MIXLIN in CR17). The mixer does not have a gain control on the inputs, therefore the user should reduce the levels of the input signals within the analog signal range. The stereo Analog Mixer is powered up with bits ENMIXL and ENMIXR in CR2.

### 3.11 AD path

The AD path converts audio signals from Microphone Preamplifiers (selected with bit ADMIC in CR17) and Line In Amplifiers (bit ADLIN in CR17) inputs to digital domain. If both inputs are selected then the sum of the two is converted. After AD conversion the audio data is resampled with a sample rate converter and then processed with the internal DSP. Two different filters are selectable in the DSP (bit ADVOICE in CR29): stereo Audio Filter, with DC offset removal and FIR image filtering; and a standard mono Voice-channel filter (uses left channel input and feeds both channel output). The AD path includes a digital gain control (ADCLG, ADCRG in CR12 and CR13 respectively) in the range -57 to +8 dB. The maximum gain from Mic Preamplifier to AD interface is then 47 dB. When Audio filter is selected in both AD and DA paths then DA audio data can be summed to AD data and sent to the AD Audio Interface (see DA2ADG in CR15). Left and Right channels can be independently switched on and off to save power, if needed (bits ENADCL and ENADCR in CR1)

### 3.12 **DA** path

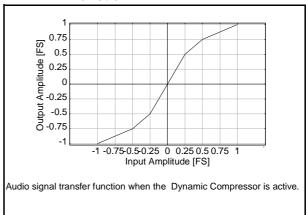

The DA path converts digital data from the digital audio interface to analog domain and feeds it to the analog mixer. Incoming audio data is processed with a DSP where different filters are selectable (bit DAVOICE in CR29): Audio Filter, stereo, with FIR image filtering, bass and treble controls (bits BASS and TREBLE in CR14), de-emphasis filter; and a standard Voice-channel filter, mono (uses left channel input and feeds both channel output). A dynamic compression function is available for both audio and voice filters (bit DYNC in CR14). The DA path includes a digital gain control (DACLG, DACRG in CR10 and CR11 respectively) in the range -65 to 0 dB. AD to DA mixing (sidetone) can be enabled: see CR16 for details. Left and Right channel can be independently switched on and off to save power, if needed (bits ENDACL and ENDACR in CR1)

### 3.13 Analog-only operation

STw5095 can operate without AMCK master clock if analog-only functions are used. It is possible to mix Microphone and Line In preamplifiers signals and listen through headphones, loudspeaker or send them to line-out. The analog-only operation is enabled with bit ENOSC in CR0. When ENOSC=1 the AD and DA paths cannot be used.

3 Functional Description STw5095

In Analog Mode STw5095 can handle two different stereo audio signals, so it can be used as a front end for an external voice codec that does not include microphone preamplifiers and power drivers: mic signal is sent through Microphone preamplifiers directly to line out drivers (Transmit path), while Receive signal is sent through Line In amplifiers to the selected power drivers.

### 3.14 Automatic Gain Control (AGC)

STw5095 provides a digital Automatic Gain Control in AD path. The circuit can control the input gain at MIC preamplifier, Line In amplifier or both (bits ENAGCMIC and ENAGCLIN in CR35). When one input is selected, the center gain value used for the input is fixed with bits MICLG, MICRG, LINLG and LINRG in CR3 to CR6 (like in normal operation), then the AGC circuit adds to all the gains a value in the range -10.5 dB to +10.5 dB (or, extended with bit AGCRANGE in CR35, -21 dB to 21 dB), in order to obtain an average level at the digital interface output in the range -6 dB to -30 dB (selected with bits AGCLEV in CR35). The AGC added gain acts directly in the input gain, to avoid input saturation and improve S/N ratio, so it cannot exceed the input gain range. When MIC and Line-In inputs are selected simultaneously the control is performed on the sum of the two, preserving the balance fixed with input gains. Different values for Attack and Decay constants can be selected, depending on the kind of signal the AGC has to control (i.e. voice, music). The Attack and Decay time constants are related to the AD data rate (see bits AGCATT and AGCDEL in CR34).

### 3.15 Interrupt request: IRQ pin

STw5095 interrupt request feature can signal to a control device the occurrence of particular events. Two control registers are used to choose the behavior of IRQ pin: the first is a Status/ Event Register (CR32), where bits can represent the status of an internal function (i.e. a voltage is above or below a threshold) or an event (i.e. a voltage changed crossing a threshold); the second is a Mask Register (CR31) where if a bit in the mask is set to 1 then the corresponding bit in the Status/Event Register can affect IRQ pin status.

The IRQ pin is always active low. At  $V_{CC}$  power up an interrupt request is generated by the Power-On-Reset circuit that sets to 1 bits PORMSK in CR31 and POREV in CR32. After this event the PORMSK bit should be cleared by the user and bit IRQCMOS in CR33 should be set according to the application (open drain or CMOS).

When an IRQ event occurs and SPI control interface is selected with no serial output pin it is still possible to identify the event (and relative status) that generated the interrupt request. This can be done by setting the IRQ mask/enable bits (in CR31) one at the time (with successive writings) and reading the IRQ pin status. A simple example of this is the headset plug-in detection: at first we set bit HSDETMSK=1 in CR31 (with all the other bits set to 0). If there is an interrupt request then we set HSDETMSK=0 and HSDETEN=1, so we can read the HSDET status at IRQ pin. Then we read CR32 to clear its content (even if no data is sent out).

STw5095 3 Functional Description

### 3.16 Headset plug-in and push-button detection

STw5095 can detect the plug-in of a microphone connector and the press/release event of a call/answer push-button. An application example can be found below, while specifications can be found in *Section 9.4 on page 54*.

VCCA

3kΩ

1.5kΩ

1.5kΩ

From Driver

Generic Connector

Figure 3. Plug-in and push-button detection application note

### 3.17 Microphone biasing circuit

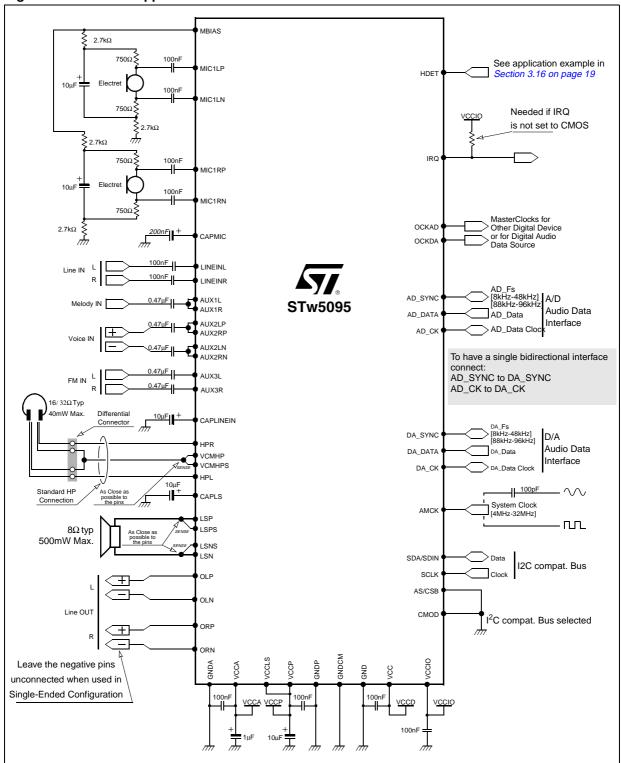

The Microphone Biasing Circuit can drive mono or stereo microphones and can switch them off when not needed in order to save the current used by the microphone biasing network. Two bits control the behavior of the microphone bias circuit: MBIAS in CR17 enables the circuit (fixed voltage at MBIAS pin), while bit MBIASPD in CR17 affects the behavior of MBIAS pin when the function is not enabled. In particular when MBIASPD=1 the MBIAS pin is pulled down, otherwise it is left in tristate mode. The specification for the microphone biasing circuit can be found in *Section 9.6 on page 55*, and an application note is shown in *Section 17 on page 66*.

## 4 Control Registers

## 4.1 Summary

| CR#<br>(hex) | Description                | D7      | D6         | D5          | D4        | D3       | D2          | D1           | D0      | Def.      |

|--------------|----------------------------|---------|------------|-------------|-----------|----------|-------------|--------------|---------|-----------|

| CR0 (00h)    | Supply & Power Control #1  | POWERUP | ENANA      | ENAMCK      | ENOSC     | ENPLL    | ENHSD       | A24V         | D12V    | 0000 0000 |

| CR1 (01h)    | Power Control #2           | ENADCL  | ENADCR     | ENDACL      | ENDACR    | ENMICL   | ENMICR      | ENLINL       | ENLINR  | 0000 0000 |

| CR2 (02h)    | Power Control #3           | ENLOL   | ENLOR      | ENHPL       | ENHPR     | ENHPVCM  | ENLS        | ENMIXL       | ENMIXR  | 0000 0000 |

| CR3 (03h)    | Mic Gain Left              |         | MICLA(2:0) |             |           |          | MICLG(4:0)  | •            |         | 0000 0000 |

| CR4 (04h)    | Mic Gain Right             |         | MICRA(2:0) |             |           |          | MICRG(4:0)  |              |         | 0000 0000 |

| CR5 (05h)    | Line in Gain Left          | Х       | Х          | Х           |           |          | LINLG(4:0)  |              |         | 0000 1001 |

| CR6 (06h)    | Line in Gain Right         | Х       | Х          | х           |           |          | LINRG(4:0)  |              |         | 0000 1001 |

| CR7 (07h)    | LO gain & LS gain          | Х       |            | LOG(2:0)    | •         |          | LSG         | 6(3:0)       |         | 0000 0011 |

| CR8 (08h)    | HPL Gain                   | Х       | Х          | Х           |           |          | HPLG(4:0)   |              |         | 0000 0011 |

| CR9 (09h)    | HPR Gain                   | Х       | Х          | Х           |           |          | HPRG(4:0)   |              |         | 0000 0011 |

| CR10 (0Ah)   | DAC Digital Gain Left      | Х       | Х          |             |           | DACL     | G(5:0)      |              |         | 0000 0000 |

| CR11 (0Bh)   | DAC Digital Gain Right     | Х       | Х          |             |           | DACR     | G(5:0)      |              |         | 0000 0000 |

| CR12 (0Ch)   | ADC Digital Gain Left      | Х       | Х          |             |           | ADCL     | G(5:0)      |              |         | 0000 1000 |

| CR13 (0Dh)   | ADC Digital Gain Right     | Х       | Х          |             |           | ADCR     | G(5:0)      |              |         | 0000 1000 |

| CR14 (0Eh)   | Bass/Treble/De-emphasis    | DYNC    |            | TREBLE(2:0) |           |          | BAS         | S(3:0)       |         | 0000 0000 |

| CR15 (0Fh)   | DA to AD mixing gain       | Х       | Х          | Х           |           |          | DA2ADG(4:0) |              |         | 0000 0000 |

| CR16 (10h)   | AD to DA mix/sidetone gain | Х       | Х          |             |           | AD2DA    | G(5:0)      |              |         | 0000 0000 |

| CR17 (11h)   | Mixer Switches & Mic Bias  | MBIAS   | MBIASPD    | ADMIC       | ADLIN     | MIXMIC   | MIXLIN      | MIXDAC       | MICLO   | 0000 0000 |

| CR18 (12h)   | Input Switches             | Х       | IN2VCM     | LINMUTE     | LINSE     | L(1:0)   | MICMUTE     | MICSE        | EL(1:0) | 0010 0100 |

| CR19 (13h)   | Drivers Control            | VCMI    | L(1:0)     | Х           | MUTELO    | MUTEHP   | LSLIM       | LSSE         | L(1:0)  | 0101 1000 |

| CR20 (14h)   | DAOCK Frequency Ls byte    |         |            |             | DAOC      | KF(7:0)  |             |              |         | 0000 0000 |

| CR21 (15h)   | DAOCK Frequency Ms byte    |         |            |             | DAOC      | KF(15:8) |             |              |         | 0000 0000 |

| CR22 (16h)   | DA Clock Generator Control | Х       | Х          | DAMAST      | DAMASTGEN | ENDAOCK  | DAOCK512    | DAPC         | MF(1:0) | 0000 0000 |

| CR23 (17h)   | ADOCK Frequency Ls byte    |         |            |             | ADOC      | KF(7:0)  |             |              |         | 0000 0000 |

| CR24 (18h)   | ADOCK Frequency Ms byte    |         |            |             | ADOC      | KF(15:8) |             |              |         | 0000 0000 |

| CR25 (19h)   | AD Clock Generator Control | Х       | Х          | ADMAST      | ADMASTGEN | ENADOCK  | ADOCK512    | ADPC         | MF(1:0) | 0000 0000 |

| CR26 (1Ah)   | DAC Data IF Control        | Х       |            | DAFORM(2:0  | )         | DASPIM   |             | DAWL(2:0)    |         | 0000 0000 |

| CR27 (1Bh)   | ADC Data IF Control        | ADRTOL  |            | ADFORM2:0)  | )         | ADSPIM   |             | ADWL(2:0)    |         | 0000 0000 |

| CR28 (1Ch)   | DAC&ADC Data IF Control    | AMCKINV | DACKP      | DASYNCP     | DAMONO    | ADCKP    | ADSYNCP     | ADMONO       | ADHIZ   | 0000 0000 |

| CR29 (1Dh)   | Digital Filters Control    | Х       | DAVOICE    | DA96K       | RXNH      | ADVOICE  | AD96K       | ADNH         | TXNH    | 0000 0000 |

| CR30 (1Eh)   | Soft Reset & AMCK Range    | SWRES   | Х          | Х           | Х         | AMCKSIN  |             | CKRANGE(2:0) |         | 0000 0000 |

| CR31 (1Fh)   | interrupt Mask             | VLSHEN  | PUSHBEN    | HSDETEN     | VLSHMSK   | PUSHBMSK | HSDETMSK    | OVFMSK       | PORMSK  | 0000 0000 |

| CR32 (20h)   | Interrupt Status           | VLSH    | PUSHB      | HSDET       | VLSHEV    | PUSHBEV  | HSDETEV     | OVFEV        | POREV   | 0000 0000 |

| CR33 (21h)   | Misc. Control              | Х       | Х          | SPIOHIZ     | SPIOSI    | EL(1:0)  | IRQCMOS     | OVFDA        | OVFAD   | 0000 0000 |

| CR34 (22h)   | AGC Attack/Decay coeff.    |         | AGC        | ATT(3:0)    |           |          | AGCD        | EC(3:0)      |         | 0000 0000 |

| CR35 (23h)   | AGC Control                | Х       | ENAGCLIN   | ENAGCMIC    | AGCRANGE  |          | AGCL        | EV(3:0)      |         | 0000 0000 |

| CR36 (24h)   | RESERVED                   | Х       | Х          | х           | х         | х        | Х           | Х            | Х       | 0000 0000 |

Note: X reserved, write zero

## 4.2 Supply and power control

| CR#<br>(hex) | Description               | D7      | D6     | D5     | D4     | D3      | D2     | D1     | D0     | Def.      |

|--------------|---------------------------|---------|--------|--------|--------|---------|--------|--------|--------|-----------|

| CR0 (00h)    | Supply & Power Control #1 | POWERUP | ENANA  | ENAMCK | ENOSC  | ENPLL   | ENHSD  | A24V   | D12V   | 0000 0000 |

| CR1 (01h)    | Power Control #2          | ENADCL  | ENADCR | ENDACL | ENDACR | ENMICL  | ENMICR | ENLINL | ENLINR | 0000 0000 |

| CR2 (02h)    | Power Control #3          | ENLOL   | ENLOR  | ENHPL  | ENHPR  | ENHPVCM | ENLS   | ENMIXL | ENMIXR | 0000 0000 |

| Bits | Name       | Val. | CR0 Description                                                              | Def. |

|------|------------|------|------------------------------------------------------------------------------|------|

| 7    | POWERUP    | 1    | All the enabled analog and digital blocks are in power up                    | 0    |

|      |            | 0    | All the device is in power down                                              |      |

| 6    | ENANA      | 1    | The analog blocks can be enabled                                             | 0    |

| 0    |            | 0    | All the analog blocks are in power down                                      | O    |

| 5    | ENAMCK     | 1    | AMCK clock input pin is enabled                                              | 0    |

| 3    | LIVAIVICIT | 0    | AMCK clock input pin is disabled                                             | U    |

|      |            | 1    | The Internal Oscillator is enabled. The analog blocks use Oscillator         |      |

| 4    | 4 ENOSC    | 1000 | clock                                                                        | 0    |

|      |            | 0    | The Internal Oscillator is in power down                                     |      |

| 3    | ENPLL      | 1    | The PLL is enabled                                                           | 0    |

| 3    | EINPLL     | 0    | The PLL is in power down                                                     | U    |

| 2    | ENHSD      | 1    | The Headset Plug-in Detector is enabled                                      | 0    |

| 2    | ENHOD      | 0    | The Headset Plug-in Detector is disabled                                     | U    |

| _    | 1041/      | 1    | Analog Supply Pins voltage range is 2.4V <v<sub>CCA&lt;2.7V</v<sub>          | 0    |

| 1    | A24V       | 0    | Analog Supply Pins voltage range is 2.7V <v<sub>CCA&lt;3.3V</v<sub>          | 0    |

|      | D40)/      | 1    | Digital I/O Pins voltage range is 1.2V <v<sub>CCIO&lt;1.8V</v<sub>           | •    |

| 0    | D12V       | 0    | Digital I/O Pins voltage range is 1.71V <v<sub>CCIO<v<sub>CC</v<sub></v<sub> | 0    |

**577**

| Bits | Name       | Value | CR1 Description                                            | Def. |

|------|------------|-------|------------------------------------------------------------|------|

| 7    | ENADCL     | 1     | The left channel A/D converter is enabled                  | 0    |

|      |            | 0     | The left channel A/D converter is in power down            |      |

| 6    | ENADCR     | 1     | The right channel A/D converter is enabled                 | 0    |

| 0    | LIVIDOR    | 0     | The right channel A/D converter is in power down           | O    |

| 5    | ENDACL     | 1     | The left channel D/A converter is enabled                  | 0    |

| 5    | ENDACL     | 0     | The left channel D/A converter is in power down            | U    |

| 4    | ENDACR     | 1     | The right channel D/A converter is enabled                 | 0    |

| 4    | 4 ENDACK   | 0     | The right channel D/A converter is in power down           | U    |

| 3    | ENMICL     | 1     | The left channel microphone preamplifier is enabled        | 0    |

| 3    | ENVIICE    | 0     | The left channel microphone preamplifier is in power down  | U    |

| 2    | ENMICR     | 1     | The right channel microphone preamplifier is enabled       | 0    |

| 2    | LINIVIICIX | 0     | The right channel microphone preamplifier is in power down | U    |

| 1    | ENLINL     | 1     | The left channel line-in preamplifier is enabled           | 0    |

| •    | LIVEHVE    | 0     | The left channel line-in preamplifier is in power down     | O    |

| 0    | ENLINR     | 1     | The right channel line-in preamplifier is enabled          | 0    |

| U    | U EINLINK  | 0     | The right channel line-in preamplifier is in power down    | U    |

| Bit # | Name    | Value  | CR2 Description                                                                                                         | Def. |

|-------|---------|--------|-------------------------------------------------------------------------------------------------------------------------|------|

| 7     | ENLOL   | 1<br>0 | The left channel line out driver is enabled The left channel line out driver is in power down (default)                 | 0    |

| 6     | ENLOR   | 1<br>0 | The right channel line out driver is enabled The right channel line out driver is in power down (default)               | 0    |

| 5     | ENHPL   | 1<br>0 | The left channel headphones driver is enabled The left channel headphones driver is in power down (default)             | 0    |

| 4     | ENHPR   | 1<br>0 | The right channel headphones driver is enabled The right channel headphones driver is in power down (default)           | 0    |

| 3     | ENHPVCM | 1<br>0 | The headphones reference voltage generator is enabled The headphones reference voltage generator is in power down (def) | 0    |

| 2     | ENLS    | 1<br>0 | The $8\Omega$ loudspeaker amplifier is enabled The $8\Omega$ loudspeaker amplifier is in power down (default)           | 0    |

| 1     | ENMIXL  | 1<br>0 | The left channel analog output mixer is enabled The left channel analog output mixer is in power down (default)         | 0    |

| 0     | ENMIXR  | 1<br>0 | The right channel analog output mixer is enabled The right channel analog output mixer is in power down (default)       | 0    |

### 4.3 Gains

| CR#<br>(hex) | Description            | D7 | D6         | D5         | D4         | D3   | D2         | D1    | D0 | Def.      |

|--------------|------------------------|----|------------|------------|------------|------|------------|-------|----|-----------|

| CR3 (03h)    | Mic Gain Left          |    | MICLA(2:0) |            |            |      | MICLG(4:0) |       |    | 0000 0000 |

| CR4 (04h)    | Mic Gain Right         |    | MICRA(2:0) |            |            |      | MICRG(4:0) |       |    | 0000 0000 |

| CR5 (05h)    | Line in Gain Left      | Х  | х          | Х          |            |      | LINLG(4:0) |       |    | 0000 1001 |

| CR6 (06h)    | Line in Gain Right     | Х  | Х          | Х          |            |      | LINRG(4:0) |       |    | 0000 1001 |

| CR7 (07h)    | LO gain & LS gain      | Х  |            | LOG(2:0)   |            |      | LSG        | (3:0) |    | 0000 0011 |

| CR8 (08h)    | HPL Gain               | Х  | Х          | Х          |            |      | HPLG(4:0)  |       |    | 0000 0011 |

| CR9 (09h)    | HPR Gain               | Х  | Х          | Х          |            |      | HPRG(4:0)  |       |    | 0000 0011 |

| CR10 (0Ah)   | DAC Digital Gain Left  | Х  | Х          |            | •          | DACL | .G(5:0)    |       |    | 0000 0000 |

| CR11 (0Bh)   | DAC Digital Gain Right | Х  | Х          |            | DACRG(5:0) |      |            |       |    |           |

| CR12 (0Ch)   | ADC Digital Gain Left  | Х  | Х          | ADCLG(5:0) |            |      |            |       |    | 0000 1000 |

| CR13 (0Dh)   | ADC Digital Gain Right | Х  | Х          |            |            | ADCR | RG(5:0)    |       |    | 0000 1000 |

| Bits | Name CR3<br>Name CR4     | Value                                | CR3 and CR4 Description                                                                                                                          | Def.  |

|------|--------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7-5  | MICLA(2:0)<br>MICRA(2:0) | 000<br>001<br>010<br><br>110         | Left (CR3) and Right (CR4) Channels Microphone Attenuation 0.0 dB Gain (default) -1.5 dB Gain -3.0 dB Gainstep 1.5 dB -9.0 dB Gain -12.0 dB Gain | 000   |

| 4-0  | MICLG(4:0)<br>MICRG(4:0) | 00000<br>00001<br>00010<br><br>11010 | Left (CR3) and Right (CR4) Channels Microphone Gain 0.0 dB Gain (default) 1.5 dB Gain 3.0 dB Gainstep 1.5 dB 39.0 dB Gain                        | 00000 |

| Bits | Name CR5<br>Name CR6 | Value        | CR5 and CR6 Description                          | Def.  |

|------|----------------------|--------------|--------------------------------------------------|-------|

|      |                      |              | Left (CR5) and Right (CR6) Channels Line In Gain |       |

|      |                      | 00000        | 18.0 dB Gain                                     |       |

|      | 00001 16.0 dB 0      | 16.0 dB Gain |                                                  |       |

| 4-0  | LINLG(4:0)           | 00010        | 14.0 dB Gain                                     | 01001 |

| 4-0  | LINRG(4:0)           |              | step 2.0 dB                                      | 01001 |

|      |                      | 01001        | 0.0 dB Gain (default)                            |       |

|      |                      |              | step 2.0 dB                                      |       |

|      |                      | 10011        | -20.0 dB Gain                                    |       |

**577**

| Bits | Name     | Value                            | CR7 Description                                                                                                                                                                                                                                         |      |  |  |

|------|----------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| 6-4  | LOG(2:0) | 000<br>001<br>010<br>            | Left and Right Channel Line Out Drivers Gain Gain to Differential Output Equivalent Single-Ended Gain -18.0 dB Gain (default) -24.0 dB Gain (default) -15.0 dB Gain -21.0 dB Gain -12.0 dB Gain -18.0 dB Gainstep 3 dBstep 3 dB 00 dB Gain -6.0 dB Gain | 000  |  |  |

| 3-0  | LSG(3:0) | 0000<br>0001<br>0010<br>0011<br> | 8Ω Loudspeaker Gain 6.0 dB Gain 4.0 dB Gain 2.0 dB Gain 0.0 dB Gain 0.0 dB Gain (default)step 2.0 dB -24.0 dB Gain                                                                                                                                      | 0011 |  |  |

| Bits | Name CR8<br>Name CR9   | Value                   | CR8 and CR9 Description                                                | Def.  |

|------|------------------------|-------------------------|------------------------------------------------------------------------|-------|

|      |                        | 00000                   | Left (CR8) and Right (CR9) Channels Headphones Driver Gain 0.0 dB Gain |       |

| 4-0  | HPLG(4:0)<br>HPRG(4:0) | 00001<br>00010<br>00011 | -2.0 dB Gain -4.0 dB Gain -6.0 dB Gain (default)                       | 00011 |

|      |                        | <br>10100               | step 2.0 dB<br>-40.0dB Gain                                            |       |

| Bits | Name CR10<br>Name CR11 | Value                                                                                  | CR10 and CR11 Description                                                                                                                                                                                                                                                                                                                                                                                                        | Def. |

|------|------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Bits |                        | 000000<br>000001<br>000010<br>000011<br>000101<br>000101<br>000111<br>001000<br>001001 | CR10 and CR11 Description  Left (CR10) and Right (CR11) Channels DAC Digital Gain 0.0 dB Gain (default) -1.0 dB Gain -2.0 dB Gain -3.0 dB Gain -3.0 dB Gain -4.0 dB Gain -5.0 dB Gain -6.0 dB Gain -7.0 dB Gain -9.0 dB Gain -10.0 dB Gain -11.0 dB Gain -11.0 dB Gain -12.0 dB Gain -13.0 dB Gain -14.0 dB Gain -15.0 dB Gain -17.0 dB Gain -17.0 dB Gain -18.0 dB Gain | Def. |

|      |                        | 010011<br>010100<br>010101<br>010110<br>010111<br>011000<br>011001<br>011010<br>011011 | -20.0 dB Gain -22.0 dB Gain -24.0 dB Gain -26.0 dB Gain -28.0 dB Gain -30.0 dB Gain -32.0 dB Gain -34.0 dB Gain -36.0 dB Gain -36.0 dB Gain -40 dB Gain -41.0 dB Gain -47.0 dB Gain -50.0 dB Gain -50.0 dB Gain -50.0 dB Gain -50.0 dB Gain -56.0 dB Gain -59.0 dB Gain -59.0 dB Gain -65.0 dB Gain -∞ dB Gain                                                                                                                   |      |

| Bits | Name CR12<br>Name CR13 | Value                                                                                                                | CR12 and CR13 Description                                                                                                                                                                                                                                                                                  | Def.   |

|------|------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|      |                        | 000000<br>000001<br>000010<br>000011<br>000100<br>000101                                                             | Left (CR12) and Right (CR13) Channels ADC Digital Gain 8.0 dB Gain 7.0 dB Gain 6.0 dB Gain 5.0 dB Gain 4.0 dB Gain 3.0 dB Gain                                                                                                                                                                             |        |

|      |                        | 000110<br>000111<br>001000<br>001001<br>001010<br>001011<br>001100<br>001101<br>001110<br>001111<br>010000<br>010001 | 2.0 dB Gain 1.0 dB Gain 0.0 dB Gain (default) -1.0 dB Gain -2.0 dB Gain -3.0 dB Gain -4.0 dB Gain -5.0 dB Gain -6.0 dB Gain -7.0 dB Gain -8.0 dB Gain -9.0 dB Gain                                                                                                                                         |        |

| 5-0  | ADCLG(5:0) ACDRG(5:0)  | 010010<br>010011<br>010100<br>010101<br>010110<br>010111<br>011000<br>011001<br>011011                               | -10.0dB Gain -11.0dB Gain -12.0dB Gain -14.0dB Gain -16.0dB Gain -16.0dB Gain -18.0dB Gain -20.0dB Gain -20.0dB Gain -24.0dB Gain -24.0dB Gain -26.0dB Gain -28.0dB Gain -30.0dB Gain -30.0dB Gain -30.0dB Gain -30.0dB Gain -36.0dB Gain -40.0dB Gain -45.0dB Gain -45.0dB Gain -45.0dB Gain -57.0dB Gain | 001000 |

### 4.4 DSP control

| CR#<br>(hex) | Description                | D7   | D6 | D5            | D4          | D3        | D2 | D1 | D0        | Def.      |

|--------------|----------------------------|------|----|---------------|-------------|-----------|----|----|-----------|-----------|

| CR14 (0Eh)   | Bass/Treble/De-emphasis    | DYNC |    | TREBLE(2:0)   |             | BASS(3:0) |    |    |           | 0000 0000 |

| CR15 (0Fh)   | DA to AD mixing gain       | Х    | Х  | Х             | DA2ADG(4:0) |           |    |    |           | 0000 0000 |

| CR16 (10h)   | AD to DA mix/sidetone gain | Х    | Х  | X AD2DAG(5:0) |             |           |    |    | 0000 0000 |           |

| Bits     | Name        | Value | CR14 Description                                  | Def. |  |  |  |  |

|----------|-------------|-------|---------------------------------------------------|------|--|--|--|--|

| 7        | DYNC        | 1     | Audio Dynamic Compression in D/A path is enabled  | 0    |  |  |  |  |

| <b>'</b> | DINC        | 0     | audio Dynamic Compression in D/A path is disabled |      |  |  |  |  |

|          |             |       | Treble Control in D/A path                        |      |  |  |  |  |

|          |             | 011   | +6.0 dB Treble Gain                               |      |  |  |  |  |

|          |             | 010   | +4.0 dB Treble Gain                               |      |  |  |  |  |

|          |             | 001   | +2.0 dB Treble Gain                               |      |  |  |  |  |

| 6-4      | TREBLE(2:0) | 000   | 0.0 dB Treble Gain                                | 000  |  |  |  |  |

|          |             | 111   | -2.0 dB Treble Gain                               |      |  |  |  |  |

|          |             | 110   | -4.0 dB Treble Gain                               |      |  |  |  |  |

|          |             | 101   | -6.0 dB Treble Gain                               |      |  |  |  |  |

|          |             | 100   | De-emphasis filter enabled                        |      |  |  |  |  |

|          |             |       | Bass Control in D/A path                          |      |  |  |  |  |

|          |             | 0101  | +12.5dB Bass Gain                                 |      |  |  |  |  |

|          |             | 0100  | +10.0dB Bass Gain                                 |      |  |  |  |  |

|          |             | 0011  | +7.5dB Bass Gain                                  |      |  |  |  |  |

|          |             | 0010  | +5.0 dB Bass Gain                                 |      |  |  |  |  |

| 3-0      | BASS(3:0)   | 0001  | +2.5dB Bass Gain                                  | 0000 |  |  |  |  |

| 3-0      | DA33(3.0)   | 0000  | 0.0 dB Bass Gain                                  | 0000 |  |  |  |  |

|          |             | 1111  | -2.5 dB Bass Gain                                 |      |  |  |  |  |

|          |             | 1110  | -5.0 dB Bass Gain                                 |      |  |  |  |  |

|          |             | 1101  | -7.5dB Bass Gain                                  |      |  |  |  |  |

|          |             | 1100  | -10.0dB Bass Gain                                 |      |  |  |  |  |

|          |             | 1011  | -12.5dB Bass Gain                                 |      |  |  |  |  |

**577**

| Bits | Name         | Value | CR15 Description                            | Def.  |

|------|--------------|-------|---------------------------------------------|-------|

|      |              |       | DA to AD mixing                             |       |

|      |              |       | (Audio filter in D/A and A/D path selected) |       |

|      |              | 00000 | DA to AD mixing Disabled (default)          |       |

|      |              | 00001 | +2.0 dB Gain                                |       |

|      |              | 00010 | 0.0 dB Gain                                 |       |

|      |              | 00011 | -2.0 dB Gain                                |       |

|      |              | 00100 | -4.0dB Gain                                 |       |

|      |              | 00101 | -6.0 dB Gain                                |       |

|      |              | 00110 | -8.0 dB Gain                                |       |

|      |              | 00111 | -10.0 dB Gain                               |       |

|      |              | 01000 | -12.0dB Gain                                |       |

|      |              | 01001 | -14.0 dB Gain                               |       |

| 4-0  | DA2ADG(4:0)* | 01010 | -16.0dB Gain                                | 00000 |

|      |              | 01011 | -18.0dB Gain                                |       |

|      |              | 01100 | -20.0 dB Gain                               |       |

|      |              | 01101 | -22.0dB Gain                                |       |

|      |              | 01110 | -24.0dB Gain                                |       |

|      |              | 01111 | -26.0dB Gain                                |       |

|      |              | 10000 | -28.0dB Gain                                |       |

|      |              | 10001 | -30.0 dB Gain                               |       |

|      |              | 10010 | -32.0 dB Gain                               |       |

|      |              | 10011 | -34.0 dB Gain                               |       |

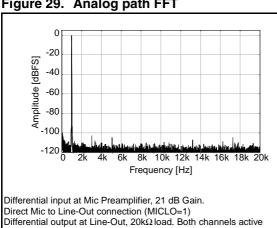

|      |              | 10100 | -36.0dB Gain                                |       |