SCBS711 - OCTOBER 1997

- Members of the Texas Instruments

SCOPE™ Family of Testability Products

- Members of the Texas Instruments Widebus™ Family

- State-of-the-Art 3.3-V ABT Design Supports Mixed-Mode Signal Operation (5-V Input and Output Voltages With 3.3-V V<sub>CC</sub>)

- Support Unregulated Battery Operation Down to 2.7 V

- UBT<sup>™</sup> (Universal Bus Transceiver)

Combines D-Type Latches and D-Type

Flip-Flops for Operation in Transparent,

Latched, or Clocked Mode

- B-Port Outputs of 'LVT182512 Devices Have Equivalent 25-Ω Series Resistors, So No External Resistors Are Required

- Compatible With the IEEE Std 1149.1-1990 (JTAG) Test Access Port and Boundary-Scan Architecture

- SCOPE™ Instruction Set

- IEEE Std 1149.1-1990 Required Instructions and Optional CLAMP and HIGHZ

- Parallel-Signature Analysis at Inputs

- Pseudo-Random Pattern Generation From Outputs

- Sample Inputs/Toggle Outputs

- Binary Count From Outputs

- Device Identification

- Even-Parity Opcodes

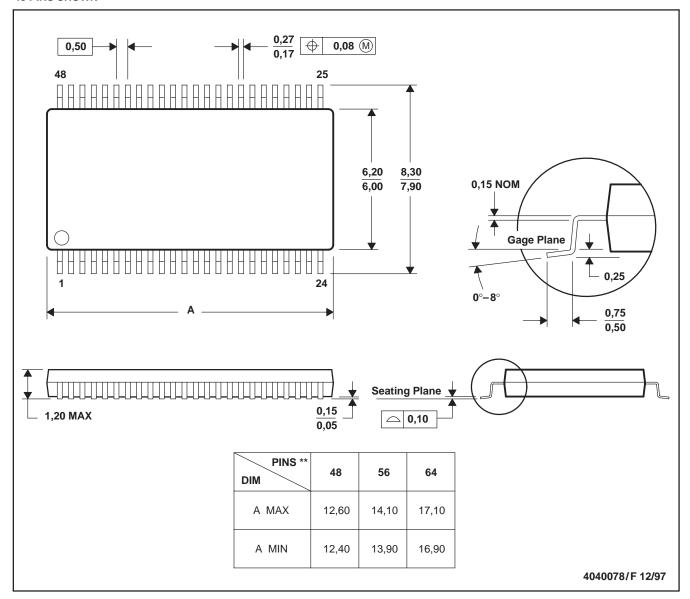

- Package Options Include 64-Pin Plastic Thin Shrink Small Outline (DGG) and 64-Pin Ceramic Dual Flat (HKC) Packages Using 0.5-mm Center-to-Center Spacings

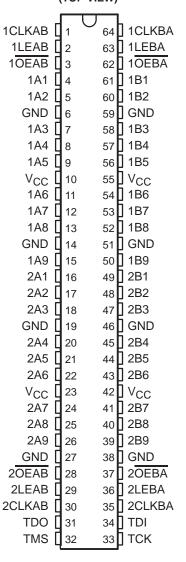

#### SN54LVT18512, SN54LVT182512 . . . HKC PACKAGE SN74LVT18512, SN74LVT182512 . . . DGG PACKAGE (TOP VIEW)

#### description

The 'LVT18512 and 'LVT182512 scan test devices with 18-bit universal bus transceivers are members of the Texas Instruments SCOPE™ testability integrated-circuit family. This family of devices supports IEEE Std 1149.1-1990 boundary scan to facilitate testing of complex circuit-board assemblies. Scan access to the test circuitry is accomplished via the 4-wire test access port (TAP) interface.

Additionally, these devices are designed specifically for low-voltage (3.3-V)  $V_{CC}$  operation, but with the capability to provide a TTL interface to a 5-V system environment.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SCOPE, Widebus, and UBT are trademarks of Texas Instruments Incorporated.

SCBS711 - OCTOBER 1997

#### description (continued)

In the normal mode, these devices are 18-bit universal bus transceivers that combine D-type latches and D-type flip-flops to allow data flow in transparent, latched, or clocked modes. They can be used either as two 9-bit transceivers or one 18-bit transceiver. The test circuitry can be activated by the TAP to take snapshot samples of the data appearing at the device pins or to perform a self test on the boundary-test cells. Activating the TAP in the normal mode does not affect the functional operation of the SCOPE™ universal bus transceivers.

Data flow in each direction is controlled by output-enable ( $\overline{OEAB}$  and  $\overline{OEBA}$ ), latch-enable (LEAB and LEBA), and clock (CLKAB and CLKBA) inputs. For A-to-B data flow, the devices operate in the transparent mode when LEAB is high. When LEAB is low, the A data is latched while CLKAB is held at a static low or high logic level. Otherwise, if LEAB is low, A data is stored on a low-to-high transition of CLKAB. When OEAB is low, the B outputs are active. When  $\overline{OEAB}$  is high, the B outputs are in the high-impedance state. B-to-A data flow is similar to A-to-B data flow but uses the OEBA, LEBA, and CLKBA inputs.

In the test mode, the normal operation of the SCOPE™ universal bus transceivers is inhibited, and the test circuitry is enabled to observe and control the I/O boundary of the device. When enabled, the test circuitry performs boundary-scan test operations according to the protocol described in IEEE Std 1149.1-1990.

Four dedicated test pins are used to observe and control the operation of the test circuitry: test data input (TDI). test data output (TDO), test mode select (TMS), and test clock (TCK). Additionally, the test circuitry performs other testing functions such as parallel-signature analysis (PSA) on data inputs and pseudo-random pattern generation (PRPG) from data outputs. All testing and scan operations are synchronized to the TAP interface.

The B-port outputs of 'LVT182512, which are designed to source or sink up to 12 mA, include equivalent 25- $\Omega$ series resistors to reduce overshoot and undershoot.

The SN54LVT18512 and SN54LVT182512 are characterized for operation over the full military temperature range of -55°C to 125°C. The SN74LVT18512 and SN74LVT182512 are characterized for operation from -40°C to 85°C.

**FUNCTION TABLE**† (normal mode, each register)

|      | INPUTS |            |   |                  |  |  |  |

|------|--------|------------|---|------------------|--|--|--|

| OEAB | LEAB   | CLKAB      | Α | В                |  |  |  |

| L    | L      | L          | Χ | в <sub>0</sub> ‡ |  |  |  |

| L    | L      | $\uparrow$ | L | L                |  |  |  |

| L    | L      | $\uparrow$ | Н | Н                |  |  |  |

| L    | Н      | Χ          | L | L                |  |  |  |

| L    | Н      | Χ          | Н | Н                |  |  |  |

| Н    | Χ      | Χ          | Χ | Z                |  |  |  |

<sup>&</sup>lt;sup>†</sup> A-to-B data flow is shown. B-to-A data flow is similar but uses OEBA, LEBA, and CLKBA.

<sup>‡</sup>Output level before the indicated steady-state input conditions were established

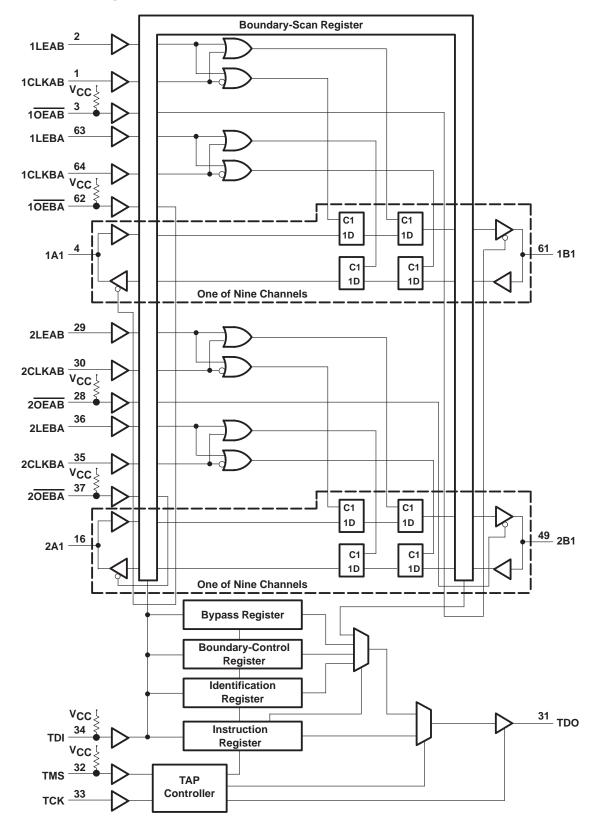

## functional block diagram

SCBS711 - OCTOBER 1997

## **Terminal Functions**

| TERMINAL NAME                                   | DESCRIPTION                                                                                                                                                                                                                                       |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1A1–1A9,<br>2A1–2A9                             | Normal-function A-bus I/O ports. See function table for normal-mode logic.                                                                                                                                                                        |

| 1B1–1B9,<br>2B1–2B9                             | Normal-function B-bus I/O ports. See function table for normal-mode logic.                                                                                                                                                                        |

| 1CLKAB, 1CLKBA,<br>2CLKAB, 2CLKBA               | Normal-function clock inputs. See function table for normal-mode logic.                                                                                                                                                                           |

| GND                                             | Ground                                                                                                                                                                                                                                            |

| 1LEAB, 1LEBA,<br>2LEAB, 2LEBA                   | Normal-function latch enables. See function table for normal-mode logic.                                                                                                                                                                          |

| 1 <u>OEAB</u> , 1 <u>OEBA</u> ,<br>2OEAB, 2OEBA | Normal-function output enables. See function table for normal-mode logic. An internal pullup at each terminal forces the terminal to a high level if left unconnected.                                                                            |

| TCK                                             | Test clock. One of four terminals required by IEEE Std 1149.1-1990. Test operations of the device are synchronous to TCK. Data is captured on the rising edge of TCK and outputs change on the falling edge of TCK.                               |

| TDI                                             | Test data input. One of four terminals required by IEEE Std 1149.1-1990. TDI is the serial input for shifting data through the instruction register or selected data register. An internal pullup forces TDI to a high level if left unconnected. |

| TDO                                             | Test data output. One of four terminals required by IEEE Std 1149.1-1990. TDO is the serial output for shifting data through the instruction register or selected data register.                                                                  |

| TMS                                             | Test mode select. One of four terminals required by IEEE Std 1149.1-1990. TMS directs the device through its TAP controller states. An internal pullup forces TMS to a high level if left unconnected.                                            |

| Vcc                                             | Supply voltage                                                                                                                                                                                                                                    |

#### test architecture

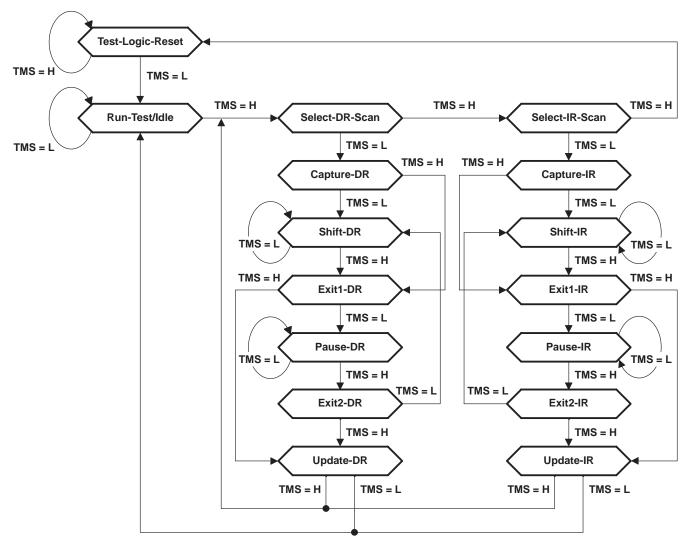

Serial-test information is conveyed by means of a 4-wire test bus or TAP, that conforms to IEEE Std 1149.1-1990. Test instructions, test data, and test control signals all are passed along this serial-test bus. The TAP controller monitors two signals from the test bus, TCK and TMS. The TAP controller extracts the synchronization (TCK) and state control (TMS) signals from the test bus and generates the appropriate on-chip control signals for the test structures in the device. Figure 1 shows the TAP-controller state diagram.

The TAP controller is fully synchronous to the TCK signal. Input data is captured on the rising edge of TCK and output data changes on the falling edge of TCK. This scheme ensures data to be captured is valid for fully one-half of the TCK cycle.

The functional block diagram shows the IEEE Std 1149.1-1990 4-wire test bus and boundary-scan architecture and the relationship among the test bus, the TAP controller, and the test registers. As shown, the device contains an 8-bit instruction register and four test-data registers: a 48-bit boundary-scan register, a 3-bit boundary-control register, a 1-bit bypass register, and a 32-bit device identification register.

Figure 1. TAP-Controller State Diagram

SCBS711 - OCTOBER 1997

#### state diagram description

The TAP controller is a synchronous finite-state machine that provides test control signals throughout the device. The state diagram shown in Figure 1 is in accordance with IEEE Std 1149.1-1990. The TAP controller proceeds through its states based on the level of TMS at the rising edge of TCK.

As shown, the TAP controller consists of 16 states. There are six stable states (indicated by a looping arrow in the state diagram) and ten unstable states. A stable state is a state the TAP controller can retain for consecutive TCK cycles. Any state that does not meet this criterion is an unstable state.

There are two main paths through the state diagram: one to access and control the selected data register and one to access and control the instruction register. Only one register can be accessed at a time.

#### Test-Logic-Reset

The device powers up in the Test-Logic-Reset state. In the stable Test-Logic-Reset state, the test logic is reset and is disabled so that the normal logic function of the device is performed. The instruction register is reset to an opcode that selects the optional IDCODE instruction, if supported, or the BYPASS instruction. Certain data registers can also be reset to their power-up values.

The state machine is constructed such that the TAP controller returns to the Test-Logic-Reset state in no more than five TCK cycles if TMS is left high. The TMS pin has an internal pullup resistor that forces it high if left unconnected or if a board defect causes it to be open circuited.

For the 'LVT18512 and 'LVT182512, the instruction register is reset to the binary value 10000001, which selects the IDCODE instruction. Bits 47–44 in the boundary-scan register are reset to logic 1, ensuring that these cells, which control A-port and B-port outputs, are set to benign values (i.e., if test mode were invoked the outputs would be at the high-impedance state). Reset-value of other bits in the boundary-scan register should be considered indeterminate. The boundary-control register is reset to the binary value 010, which selects the PSA test operation.

#### Run-Test/Idle

The TAP controller must pass through the Run-Test/Idle state (from Test-Logic-Reset) before executing any test operations. The Run-Test/Idle state also can be entered following data-register or instruction-register scans. Run-Test/Idle is a stable state in which the test logic can be actively running a test or can be idle. The test operations selected by the boundary-control register are performed while the TAP controller is in the Run-Test/Idle state.

#### Select-DR-Scan, Select-IR-Scan

No specific function is performed in the Select-DR-Scan and Select-IR-Scan states, and the TAP controller exits either of these states on the next TCK cycle. These states allow the selection of either data-register scan or instruction-register scan.

#### Capture-DR

When a data-register scan is selected, the TAP controller must pass through the Capture-DR state. In the Capture-DR state, the selected data register captures a data value as specified by the current instruction. Such capture operations occur on the rising edge of TCK, upon which the TAP controller exits the Capture-DR state.

SCBS711 - OCTOBER 1997

#### Shift-DR

Upon entry to the Shift-DR state, the data register is placed in the scan path between TDI and TDO, and on the first falling edge of TCK, TDO goes from the high-impedance state to an active state. TDO enables to the logic level present in the least-significant bit of the selected data register.

While in the stable Shift-DR state, data is serially shifted through the selected data register on each TCK cycle. The first shift occurs on the first rising edge of TCK after entry to the Shift-DR state (i.e., no shifting occurs during the TCK cycle in which the TAP controller changes from Capture-DR to Shift-DR or from Exit2-DR to Shift-DR). The last shift occurs on the rising edge of TCK, upon which the TAP controller exits the Shift-DR state.

#### Exit1-DR, Exit2-DR

The Exit1-DR and Exit2-DR states are temporary states that end a data-register scan. It is possible to return to the Shift-DR state from either Exit1-DR or Exit2-DR without recapturing the data register. On the first falling edge of TCK after entry to Exit1-DR, TDO goes from the active state to the high-impedance state.

#### Pause-DR

No specific function is performed in the stable Pause-DR state, in which the TAP controller can remain indefinitely. The Pause-DR state suspends and resumes data-register scan operations without loss of data.

#### **Update-DR**

If the current instruction calls for the selected data register to be updated with current data, such update occurs on the falling edge of TCK, following entry to the Update-DR state.

#### Capture-IR

When an instruction-register scan is selected, the TAP controller must pass through the Capture-IR state. In the Capture-IR state, the instruction register captures its current status value. This capture operation occurs on the rising edge of TCK, upon which the TAP controller exits the Capture-IR state. For the 'LVT18512 and 'LVT182512, the status value loaded in the Capture-IR state is the fixed binary value 10000001.

#### Shift-IR

Upon entry to the Shift-IR state, the instruction register is placed in the scan path between TDI and TDO. On the first falling edge of TCK, TDO goes from the high-impedance state to the active state. TDO enables to the logic level present in the least-significant bit of the instruction register.

While in the stable Shift-IR state, instruction data is serially shifted through the instruction register on each TCK cycle. The first shift occurs on the first rising edge of TCK after entry to the Shift-IR state (i.e., no shifting occurs during the TCK cycle in which the TAP controller changes from Capture-IR to Shift-IR or from Exit2-IR to Shift-IR). The last shift occurs on the rising edge of TCK, upon which the TAP controller exits the Shift-IR state.

#### Exit1-IR, Exit2-IR

The Exit1-IR and Exit2-IR states are temporary states that end an instruction-register scan. It is possible to return to the Shift-IR state from either Exit1-IR or Exit2-IR without recapturing the instruction register. On the first falling edge of TCK after entry to Exit1-IR, TDO goes from the active state to the high-impedance state.

#### Pause-IR

No specific function is performed in the stable Pause-IR state, in which the TAP controller can remain indefinitely. The Pause-IR state suspends and resumes instruction-register scan operations without loss of data.

#### **Update-IR**

The current instruction is updated and takes effect on the falling edge of TCK, following entry to the Update-IR state.

#### register overview

With the exception of the bypass and device-identification registers, any test register can be thought of as a serial shift register with a shadow latch on each bit. The bypass and device-identification registers differ in that they contain only a shift register. During the appropriate capture state (Capture-IR for instruction register, Capture-DR for data registers), the shift register can be parallel loaded from a source specified by the current instruction. During the appropriate shift state (Shift-IR or Shift-DR), the contents of the shift register are shifted out from TDO while new contents are shifted in at TDI. During the appropriate update state (Update-IR or Update-DR), the shadow latches are updated from the shift register.

### instruction register description

The instruction register (IR) is eight bits long and tells the device what instruction is to be executed. Information contained in the instruction includes the mode of operation (either normal mode, in which the device performs its normal logic function, or test mode, in which the normal logic function is inhibited or altered), the test operation to be performed, which of the four data registers is to be selected for inclusion in the scan path during data-register scans, and the source of data to be captured into the selected data register during Capture-DR.

Table 3 lists the instructions supported by the 'LVT18512 and 'LVT182512. The even-parity feature specified for SCOPE™ devices is supported in this device. Bit 7 of the instruction opcode is the parity bit. Any instructions that are defined for SCOPE™ devices but are not supported by this device default to BYPASS.

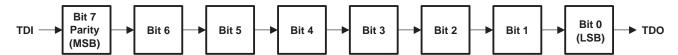

During Capture-IR, the IR captures the binary value 10000001. As an instruction is shifted in, this value is shifted out via TDO and can be inspected as verification that the IR is in the scan path. During Update-IR, the value that has been shifted into the IR is loaded into shadow latches. At this time, the current instruction is updated and any specified mode change takes effect. At power up or in the Test-Logic-Reset state, the IR is reset to the binary value 10000001, which selects the IDCODE instruction. The IR order of scan is shown in Figure 2.

Figure 2. Instruction Register Order of Scan

### data register description

#### boundary-scan register

The boundary-scan register (BSR) is 48 bits long. It contains one boundary-scan cell (BSC) for each normal-function input pin and one BSC for each normal-function I/O pin (one single cell for both input data and output data). The BSR is used to store test data that is to be applied externally to the device output pins, and/or to capture data that appears internally at the outputs of the normal on-chip logic and/or externally at the device input pins.

The source of data to be captured into the BSR during Capture-DR is determined by the current instruction. The contents of the BSR can change during Run-Test/Idle as determined by the current instruction. At power up or in Test-Logic-Reset, BSCs 47–44 are reset to logic 1, ensuring that these cells, which control A-port and B-port outputs are set to benign values (i.e., if test mode were invoked, the outputs would be at the high-impedance state). Reset values of other BSCs should be considered indeterminate.

The BSR order of scan is from TDI through bits 47–0 to TDO. Table 1 shows the BSR bits and their associated device pin signals.

**BSR BIT DEVICE BSR BIT DEVICE BSR BIT DEVICE** NUMBER NUMBER **SIGNAL SIGNAL** NUMBER **SIGNAL** 2OEAB 35 2A9-I/O 17 2B9-I/O 1OEAB 46 34 2A8-I/O 16 2B8-I/O 45 2OEBA 33 2A7-I/O 15 2B7-I/O 44 10EBA 32 14 2B6-I/O 2A6-I/O 43 2CLKAB 13 31 2A5-I/O 2B5-I/O 42 1CLKAB 30 2A4-I/O 12 2B4-I/O 41 2CLKBA 29 2A3-I/O 11 2B3-I/O 1CLKBA 10 40 28 2A2-I/O 2B2-I/O 39 2LEAB 27 2A1-I/O 9 2B1-I/O 38 1LEAB 26 1A9-I/O 8 1B9-I/O 37 2LEBA 25 1A8-I/O 7 1B8-I/O 1A7-I/O 36 1LEBA 24 6 1B7-I/O 23 1A6-I/O 5 1B6-I/O 1A5-I/O 4 1B5-I/O 22 3 21 1A4-I/O 1B4-I/O 2 20 1A3-I/O 1B3-I/O

1A2-I/O

1A1-I/O

1

0

1B2-I/O

1B1-I/O

19

18

Table 1. Boundary-Scan Register Configuration

SCBS711 - OCTOBER 1997

#### boundary-control register

The boundary-control register (BCR) is three bits long. The BCR is used in the context of the boundary-run test (RUNT) instruction to implement additional test operations not included in the basic SCOPE™ instruction set. Such operations include PRPG, PSA, and binary count up (COUNT). Table 4 shows the test operations that are decoded by the BCR.

During Capture-DR, the contents of the BCR are not changed. At power up or in Test-Logic-Reset, the BCR is reset to the binary value 010, which selects the PSA test operation. The BCR order of scan is shown in Figure 3.

Figure 3. Boundary-Control Register Order of Scan

#### bypass register

The bypass register is a 1-bit scan path that can be selected to shorten the length of the system scan path, reducing the number of bits per test pattern that must be applied to complete a test operation. During Capture-DR, the bypass register captures a logic 0. The bypass register order of scan is shown in Figure 4.

Figure 4. Bypass Register Order of Scan

SCBS711 - OCTOBER 1997

#### device-identification register

The device-identification register (IDR) is 32 bits long. It can be selected and read to identify the manufacturer, part number, and version of this device.

For the 'LVT18512, the binary value 0000000000001000111000000101111 (0004702F, hex) is captured (during Capture-DR state) in the IDR to identify this device as Texas Instruments SN54/74LVT18512.

For the 'LVT182512, the binary value 000000000000100100000000101111 (0004802F, hex) is captured (during Capture-DR state) in the device-identification register to identify this device as Texas Instruments SN54/74LVT182512.

The IDR order of scan is from TDI through bits 31–0 to TDO. Table 2 shows the IDR bits and their significance.

Table 2. Device-Identification Register Configuration

| IDR BIT<br>NUMBER | IDENTIFICATION<br>SIGNIFICANCE | IDR BIT<br>NUMBER | IDENTIFICATION<br>SIGNIFICANCE | IDR BIT<br>NUMBER | IDENTIFICATION<br>SIGNIFICANCE |

|-------------------|--------------------------------|-------------------|--------------------------------|-------------------|--------------------------------|

| 31                | VERSION3                       | 27                | PARTNUMBER15                   | 11                | MANUFACTURER10 <sup>†</sup>    |

| 30                | VERSION2                       | 26                | PARTNUMBER14                   | 10                | MANUFACTURER09 <sup>†</sup>    |

| 29                | VERSION1                       | 25                | PARTNUMBER13                   | 9                 | MANUFACTURER08†                |

| 28                | VERSION0                       | 24                | PARTNUMBER12                   | 8                 | MANUFACTURER07 <sup>†</sup>    |

| _                 | _                              | 23                | PARTNUMBER11                   | 7                 | MANUFACTURER06†                |

| _                 | _                              | 22                | PARTNUMBER10                   | 6                 | MANUFACTURER05†                |

| _                 | _                              | 21                | PARTNUMBER09                   | 5                 | MANUFACTURER04 <sup>†</sup>    |

| _                 | _                              | 20                | PARTNUMBER08                   | 4                 | MANUFACTURER03 <sup>†</sup>    |

| _                 | _                              | 19                | PARTNUMBER07                   | 3                 | MANUFACTURER02 <sup>†</sup>    |

| _                 | _                              | 18                | PARTNUMBER06                   | 2                 | MANUFACTURER01 <sup>†</sup>    |

| _                 | _                              | 17                | PARTNUMBER05                   | 1                 | MANUFACTURER00†                |

| _                 | _                              | 16                | PARTNUMBER04                   | 0                 | LOGIC1 <sup>†</sup>            |

| _                 | _                              | 15                | PARTNUMBER03                   |                   |                                |

|                   | _                              | 14                | PARTNUMBER02                   |                   |                                |

| _                 | _                              | 13                | PARTNUMBER01                   |                   |                                |

|                   | _                              | 12                | PARTNUMBER00                   |                   |                                |

<sup>†</sup> Note that for TI products, bits 11–0 of the device-identification register always contain the binary value 000000101111 (02F, hex).

SCBS711 - OCTOBER 1997

#### instruction-register opcode description

The instruction-register opcodes are shown in Table 3. The following descriptions detail the operation of each instruction.

**Table 3. Instruction-Register Opcodes**

| $\begin{array}{c} \text{BINARY CODE}^{\dagger} \\ \text{BIT 7} \rightarrow \text{BIT 0} \\ \text{MSB} \rightarrow \text{LSB} \end{array}$ | SCOPE OPCODE        | DESCRIPTION                        | SELECTED DATA<br>REGISTER | MODE          |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|---------------------------|---------------|

| 00000000                                                                                                                                  | EXTEST              | Boundary scan                      | Boundary scan             | Test          |

| 10000001                                                                                                                                  | IDCODE              | Identification read                | Device identification     | Normal        |

| 10000010                                                                                                                                  | SAMPLE/PRELOAD      | Sample boundary                    | Boundary scan             | Normal        |

| 00000011                                                                                                                                  | BYPASS‡             | Bypass scan                        | Bypass                    | Normal        |

| 10000100                                                                                                                                  | BYPASS‡             | Bypass scan                        | Bypass                    | Normal        |

| 00000101                                                                                                                                  | BYPASS <sup>‡</sup> | Bypass scan                        | Bypass                    | Normal        |

| 00000110                                                                                                                                  | HIGHZ               | Control boundary to high impedance | Bypass                    | Modified test |

| 10000111                                                                                                                                  | CLAMP               | Control boundary to 1/0            | Bypass                    | Test          |

| 10001000                                                                                                                                  | BYPASS‡             | Bypass scan                        | Bypass                    | Normal        |

| 00001001                                                                                                                                  | RUNT                | Boundary-run test                  | Bypass                    | Test          |

| 00001010                                                                                                                                  | READBN              | Boundary read                      | Boundary scan             | Normal        |

| 10001011                                                                                                                                  | READBT              | Boundary read                      | Boundary scan             | Test          |

| 00001100                                                                                                                                  | CELLTST             | Boundary self test                 | Boundary scan             | Normal        |

| 10001101                                                                                                                                  | TOPHIP              | Boundary toggle outputs            | Bypass                    | Test          |

| 10001110                                                                                                                                  | SCANCN              | Boundary-control register scan     | Boundary control          | Normal        |

| 00001111                                                                                                                                  | SCANCT              | Boundary-control register scan     | Boundary control          | Test          |

| All others                                                                                                                                | BYPASS              | Bypass scan                        | Bypass                    | Normal        |

<sup>†</sup> Bit 7 is used to maintain even parity in the 8-bit instruction.

#### boundary scan

This instruction conforms to the IEEE Std 1149.1-1990 EXTEST instruction. The BSR is selected in the scan path. Data appearing at the device input and I/O pins is captured in the associated BSCs. Data that has been scanned into the I/O BSCs for pins in the output mode is applied to the device I/O pins. Data present at the device pins, except for output enables, is passed through the BSCs to the normal on-chip logic. For I/O pins, the operation of a pin as input or output is determined by the contents of the output-enable BSCs (bits 47–44 of the BSR). When a given output enable is active (logic 0), the associated I/O pins operate in the output mode. Otherwise, the I/O pins operate in the input mode. The device operates in the test mode.

#### identification read

This instruction conforms to the IEEE Std 1149.1-1990 IDCODE instruction. The IDR is selected in the scan path. The device operates in the normal mode.

#### sample boundary

This instruction conforms to the IEEE Std 1149.1-1990 SAMPLE/PRELOAD instruction. The BSR is selected in the scan path. Data appearing at the device input pins and I/O pins in the input mode is captured in the associated BSCs, while data appearing at the outputs of the normal on-chip logic is captured in the BSCs associated with I/O pins in the output mode. The device operates in the normal mode.

<sup>&</sup>lt;sup>‡</sup> The BYPASS instruction is executed in lieu of a SCOPE™ instruction that is not supported in the 'LVT18512 or 'LVT182512.

SCBS711 - OCTOBER 1997

#### bypass scan

This instruction conforms to the IEEE Std 1149.1-1990 BYPASS instruction. The bypass register is selected in the scan path. A logic 0 value is captured in the bypass register during Capture-DR. The device operates in the normal mode.

#### control boundary to high impedance

This instruction conforms to the IEEE Std 1149.1a-1993 HIGHZ instruction. The bypass register is selected in the scan path. A logic 0 value is captured in the bypass register during Capture-DR. The device operates in a modified test mode in which all device I/O pins are placed in the high-impedance state, the device input pins remain operational, and the normal on-chip logic function is performed.

#### control boundary to 1/0

This instruction conforms to the IEEE Std 1149.1a-1993 CLAMP instruction. The bypass register is selected in the scan path. A logic 0 value is captured in the bypass register during Capture-DR. Data in the I/O BSCs for pins in the output mode is applied to the device I/O pins. The device operates in the test mode.

#### boundary-run test

The bypass register is selected in the scan path. A logic 0 value is captured in the bypass register during Capture-DR. The device operates in the test mode. The test operation specified in the BCR is executed during Run-Test/Idle. The five test operations decoded by the BCR are: sample inputs/toggle outputs (TOPSIP), PRPG, PSA, simultaneous PSA and PRPG (PSA/PRPG), and simultaneous PSA and binary count up (PSA/COUNT).

#### boundary read

The BSR is selected in the scan path. The value in the BSR remains unchanged during Capture-DR. This instruction is useful for inspecting data after a PSA operation.

#### boundary self test

The BSR is selected in the scan path. All BSCs capture the inverse of their current values during Capture-DR. In this way, the contents of the shadow latches can be read out to verify the integrity of both shift-register and shadow-latch elements of the BSR. The device operates in the normal mode.

#### boundary toggle outputs

The bypass register is selected in the scan path. A logic 0 value is captured in the bypass register during Capture-DR. Data in the shift-register elements of the selected output-mode BSCs is toggled on each rising edge of TCK in Run-Test/Idle and is then updated in the shadow latches and thereby applied to the associated device I/O pins on each falling edge of TCK in Run-Test/Idle. Data in the input-mode BSCs remains constant. Data appearing at the device input or I/O pins is not captured in the input-mode BSCs. The device operates in the test mode.

#### boundary-control-register scan

The BCR is selected in the scan path. The value in the BCR remains unchanged during Capture-DR. This operation must be performed before a boundary-run test operation to specify which test operation is to be executed.

SCBS711 - OCTOBER 1997

## boundary-control-register opcode description

The BCR opcodes are decoded from BCR bits 2–0 as shown in Table 4. The selected test operation is performed while the RUNT instruction is executed in the Run-Test/Idle state. The following descriptions detail the operation of each BCR instruction and illustrate the associated PSA and PRPG algorithms.

**Table 4. Boundary-Control Register Opcodes**

| $\begin{array}{c} \textbf{BINARY CODE} \\ \textbf{BIT 2} \rightarrow \textbf{BIT 0} \\ \textbf{MSB} \rightarrow \textbf{LSB} \end{array}$ | DESCRIPTION                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| X00                                                                                                                                       | Sample inputs/toggle outputs (TOPSIP)                        |

| X01                                                                                                                                       | Pseudo-random pattern generation/36-bit mode (PRPG)          |

| X10                                                                                                                                       | Parallel-signature analysis/36-bit mode (PSA)                |

| 011                                                                                                                                       | Simultaneous PSA and PRPG/18-bit mode (PSA/PRPG)             |

| 111                                                                                                                                       | Simultaneous PSA and binary count up/18-bit mode (PSA/COUNT) |

While the control input BSCs (bits 47–36) are not included in the toggle, PSA, PRPG, or COUNT algorithms, the output-enable BSCs (bits 47–44 of the BSR) control the drive state (active or high impedance) of the selected device output pins. These BCR instructions are only valid when both bytes of the device are operating in one direction of data flow (i.e.,  $1\overline{OEAB} \neq 1\overline{OEBA}$  and  $2\overline{OEAB} \neq 2\overline{OEBA}$ ) and in the same direction of data flow (i.e.,  $1\overline{OEAB} = 2\overline{OEBA}$ ). Otherwise, the bypass instruction is operated.

### sample inputs/toggle outputs (TOPSIP)

Data appearing at the selected device input-mode I/O pins is captured in the shift-register elements of the associated BSCs on each rising edge of TCK. Data in the shift-register elements of the selected output-mode BSCs is toggled on each rising edge of TCK, updated in the shadow latches, and applied to the associated device I/O pins on each falling edge of TCK.

## pseudo-random pattern generation (PRPG)

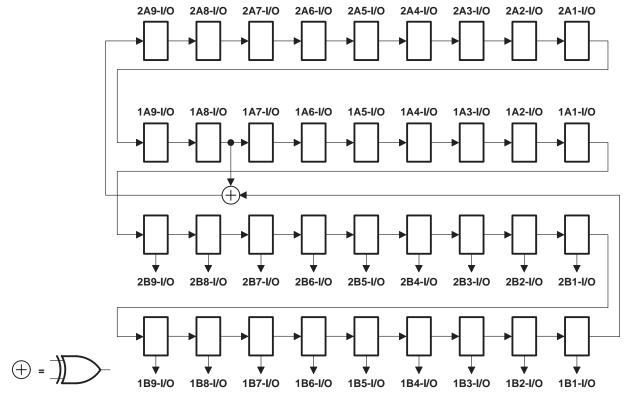

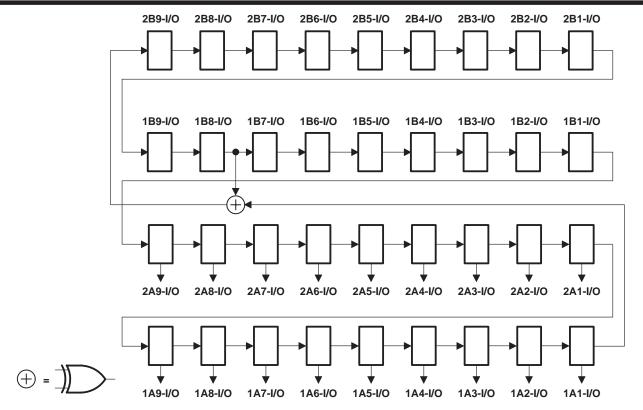

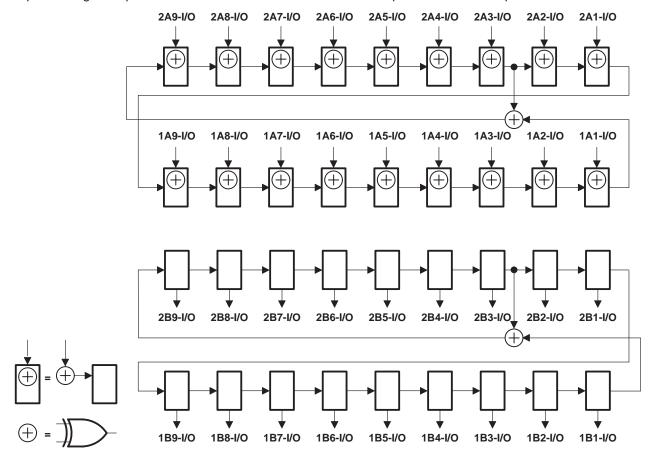

A pseudo-random pattern is generated in the shift-register elements of the selected BSCs on each rising edge of TCK, updated in the shadow latches, and applied to the associated device output-mode I/O pins on each falling edge of TCK. Figures 5 and 6 show the 36-bit linear-feedback shift-register algorithms through which the patterns are generated. An initial seed value should be scanned into the BSR before performing this operation. A seed value of all zeroes does not produce additional patterns.

Figure 5. 36-Bit PRPG Configuration (1OEAB = 2OEAB = 0, 1OEBA = 2OEBA = 1)

Figure 6. 36-Bit PRPG Configuration  $(1\overline{OEAB} = 2\overline{OEAB} = 1, 1\overline{OEBA} = 2\overline{OEBA} = 0)$

## parallel-signature analysis (PSA)

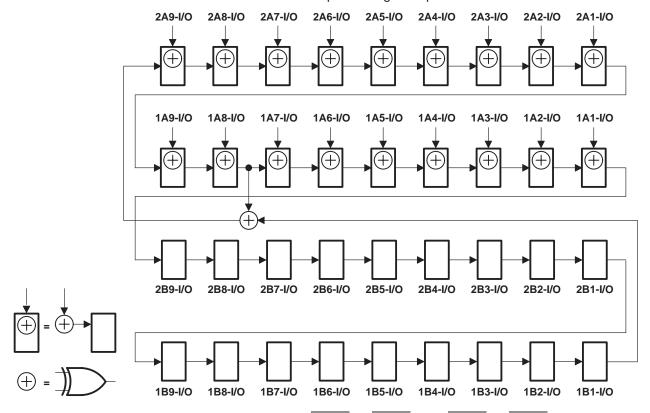

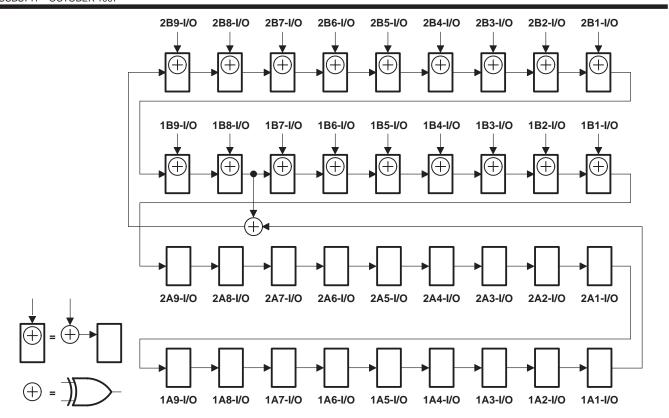

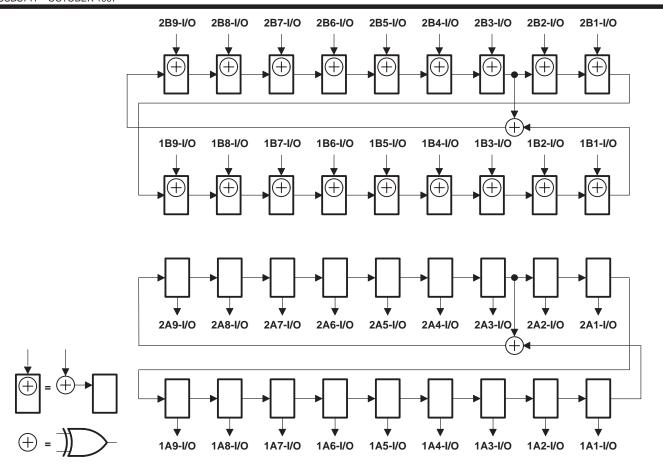

Data appearing at the selected device input-mode I/O pins is compressed into a 36-bit parallel signature in the shift-register elements of the selected BSCs on each rising edge of TCK. Data in the shadow latches of the selected output-mode BSCs remains constant and is applied to the associated device I/O pins. Figures 7 and 8 show the 36-bit linear-feedback shift-register algorithms through which the signature is generated. An initial seed value should be scanned into the BSR before performing this operation.

Figure 7. 36-Bit PSA Configuration  $(1\overline{OEAB} = 2\overline{OEAB} = 0, 1\overline{OEBA} = 2\overline{OEBA} = 1)$

Figure 8. 36-Bit PSA Configuration  $(1\overline{OEAB} = 2\overline{OEAB} = 1, 1\overline{OEBA} = 2\overline{OEBA} = 0)$

#### simultaneous PSA and PRPG (PSA/PRPG)

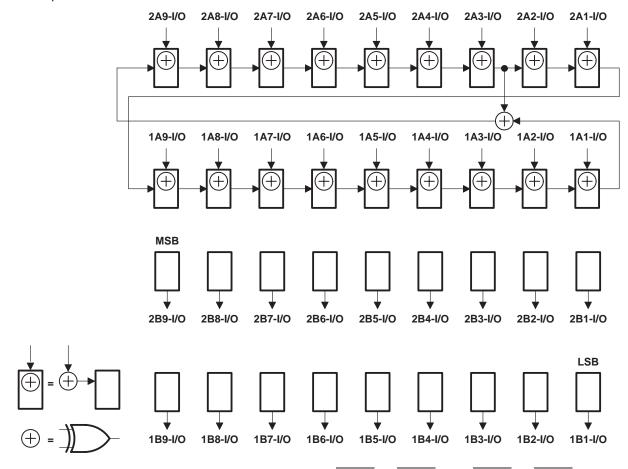

Data appearing at the selected device input-mode I/O pins is compressed into an 18-bit parallel signature in the shift-register elements of the selected input-mode BSCs on each rising edge of TCK. At the same time, an 18-bit pseudo-random pattern is generated in the shift-register elements of the selected output-mode BSCs on each rising edge of TCK, updated in the shadow latches, and applied to the associated device I/O pins on each falling edge of TCK. Figures 9 and 10 show the 18-bit linear-feedback shift-register algorithms through which the signature and patterns are generated. An initial seed value should be scanned into the BSR before performing this operation. A seed value of all zeroes does not produce additional patterns.

Figure 9. 18-Bit PSA/PRPG Configuration (1OEAB = 2OEAB = 0, 1OEBA = 2OEBA = 1)

Figure 10. 18-Bit PSA/PRPG Configuration (1OEAB = 2OEAB = 1, 1OEBA = 2OEBA = 0)

### simultaneous PSA and binary count up (PSA/COUNT)

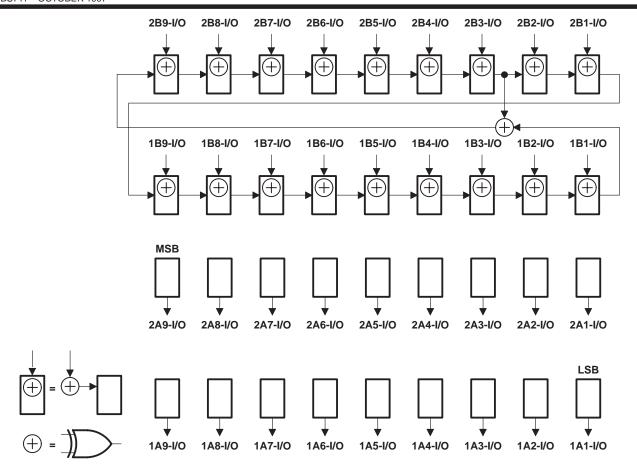

Data appearing at the selected device input-mode I/O pins is compressed into an 18-bit parallel signature in the shift-register elements of the selected input-mode BSCs on each rising edge of TCK. At the same time, an 18-bit binary count-up pattern is generated in the shift-register elements of the selected output-mode BSCs on each rising edge of TCK, updated in the shadow latches, and applied to the associated device I/O pins on each falling edge of TCK. Figures 11 and 12 show the 18-bit linear-feedback shift-register algorithms through which the signature is generated. An initial seed value should be scanned into the BSR before performing this operation.

Figure 11. 18-Bit PSA/COUNT Configuration (1OEAB = 2OEAB = 0, 1OEBA = 2OEBA = 1)

Figure 12. 18-Bit PSA/COUNT Configuration (1OEAB = 2OEAB = 1, 1OEBA = 2OEBA = 0)

SCBS711 - OCTOBER 1997

### timing description

All test operations of the 'LVT18512 and 'LVT182512 are synchronous to the TCK signal. Data on the TDI, TMS, and normal-function inputs is captured on the rising edge of TCK. Data appears on the TDO and normal-function output pins on the falling edge of TCK. The TAP controller is advanced through its states (as shown in Figure 1) by changing the value of TMS on the falling edge of TCK and then applying a rising edge to TCK.

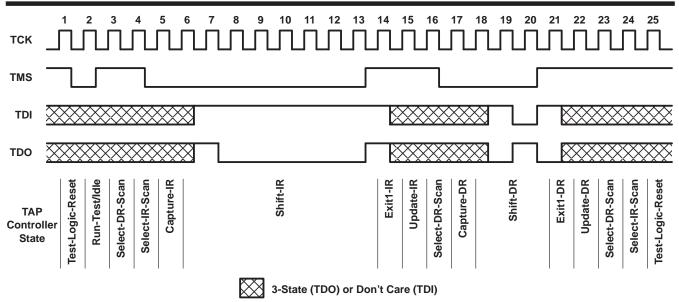

A simple timing example is shown in Figure 13. In this example, the TAP controller begins in the Test-Logic-Reset state and is advanced through its states, as necessary, to perform one instruction-register scan and one data-register scan. While in the Shift-IR and Shift-DR states, TDI is used to input serial data, and TDO is used to output serial data. The TAP controller is then returned to the Test-Logic-Reset state. Table 5 details the operation of the test circuitry during each TCK cycle.

**Table 5. Explanation of Timing Example**

| TCK<br>CYCLE(S) | TAP STATE<br>AFTER TCK | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | Test-Logic-Reset       | TMS is changed to a logic 0 value on the falling edge of TCK to begin advancing the TAP controller toward the desired state.                                                                                                                                                                                                                                                                                                                              |

| 2               | Run-Test/Idle          |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3               | Select-DR-Scan         |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4               | Select-IR-Scan         |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5               | Capture-IR             | The IR captures the 8-bit binary value 10000001 on the rising edge of TCK as the TAP controller exits the Capture-IR state.                                                                                                                                                                                                                                                                                                                               |

| 6               | Shift-IR               | TDO becomes active and TDI is made valid on the falling edge of TCK. The first bit is shifted into the TAP on the rising edge of TCK as the TAP controller advances to the next state.                                                                                                                                                                                                                                                                    |

| 7–13            | Shift-IR               | One bit is shifted into the IR on each TCK rising edge. With TDI held at a logic 1 value, the 8-bit binary value 11111111 is serially scanned into the IR. At the same time, the 8-bit binary value 10000001 is serially scanned out of the IR via TDO. In TCK cycle 13, TMS is changed to a logic 1 value to end the IR scan on the next TCK cycle. The last bit of the instruction is shifted as the TAP controller advances from Shift-IR to Exit1-IR. |

| 14              | Exit1-IR               | TDO becomes inactive (goes to the high-impedance state) on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                       |

| 15              | Update-IR              | The IR is updated with the new instruction (BYPASS) on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                           |

| 16              | Select-DR-Scan         |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17              | Capture-DR             | The bypass register captures a logic 0 value on the rising edge of TCK as the TAP controller exits the Capture-DR state.                                                                                                                                                                                                                                                                                                                                  |

| 18              | Shift-DR               | TDO becomes active and TDI is made valid on the falling edge of TCK. The first bit is shifted into the TAP on the rising edge of TCK as the TAP controller advances to the next state.                                                                                                                                                                                                                                                                    |

| 19–20           | Shift-DR               | The binary value 101 is shifted in via TDI, while the binary value 010 is shifted out via TDO.                                                                                                                                                                                                                                                                                                                                                            |

| 21              | Exit1-DR               | TDO becomes inactive (goes to the high-impedance state) on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                       |

| 22              | Update-DR              | The selected data register is updated with the new data on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                       |

| 23              | Select-DR-Scan         |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 24              | Select-IR-Scan         |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 25              | Test-Logic-Reset       | Test operation completed                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Figure 13. Timing Example

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> –0.                                                       | 5 V to 4.6 V |

|-------------------------------------------------------------------------------------------------|--------------|

| Input voltage range, V <sub>I</sub> (see Note 1)                                                |              |

| Voltage range applied to any output in the high or power-off state, V <sub>O</sub> (see Note 1) | 0.5 V to 7 V |

| Current into any output in the low state, IO: SN54LVT18512                                      | 96 mA        |

| SN54LVT182512 (A port or TDO)                                                                   |              |

| SN54LVT182512 (B port)                                                                          |              |

| SN74LVT18512                                                                                    |              |

| SN74LVT182512 (A port or TDO)                                                                   | 128 mA       |

| SN74LVT182512 (B port)                                                                          | 30 mA        |

| Current into any output in the high state, IO (see Note 2): SN54LVT18512                        | 48 mA        |

| SN54LVT182512 (A port or TDO)                                                                   | 48 mA        |

| SN54LVT182512 (B port)                                                                          | 30 mA        |

| SN74LVT18512                                                                                    | 64 mA        |

| SN74LVT182512 (A port or TDO)                                                                   | 64 mA        |

| SN74LVT182512 (B port)                                                                          | 30 mA        |

| Input clamp current, $I_{ K }(V_{ } < 0)$                                                       | –50 mA       |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0)                                      |              |

| Package thermal impedance, θ <sub>JA</sub> (see Note 3): DGG package                            | 73°C/W       |

| Storage temperature range, T <sub>stq</sub> –65°                                                |              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. This current only flows when the output is in the high state and  $V_O > V_{CC}$ .

- 3. The package thermal impedance is calculated in accordance with JESD 51.

NOTES: 1. The input and output negative-voltage ratings can be exceeded if the input and output clamp-current ratings are observed.

SCBS711 - OCTOBER 1997

## recommended operating conditions (see Note 4)

|                   |                                    |                 | SN54LVT     | 18512 | SN74LVT | UNIT |      |

|-------------------|------------------------------------|-----------------|-------------|-------|---------|------|------|

|                   |                                    |                 | MIN         | MAX   | MIN     | MAX  | UNIT |

| VCC               | Supply voltage                     |                 | 2.7         | 3.6   | 2.7     | 3.6  | V    |

| VIH               | High-level input voltage           |                 | 2           | , P   | 2       |      | V    |

| V <sub>IL</sub>   | Low-level input voltage            |                 | 0.8         |       | 0.8     | V    |      |

| VI                | Input voltage                      |                 | 8           | 5.5   |         | 5.5  | V    |

| IOH               | High-level output current          |                 | 5           | -24   |         | -32  | mA   |

| loL               | Low-level output current           |                 | 20          | 24    |         | 32   | mA   |

| I <sub>OL</sub> † | Low-level output current           |                 | 0           | 48    |         | 64   | mA   |

| Δt/Δν             | Input transition rise or fall rate | Outputs enabled | Q           | 10    |         | 10   | ns/V |

| TA                | Operating free-air temperature     |                 | <b>-</b> 55 | 125   | -40     | 85   | °C   |

<sup>†</sup> Current duty cycle ≤ 50%, f ≥ 1 kHz

NOTE 4: Unused inputs must be held high or low to prevent them from floating.

SCBS711 - OCTOBER 1997

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| DA                 | DAMETER       | TEST COM                                                            | DITIONS                               | SN5                 | 4LVT18           | 512  | SN7                | '4LVT18          | 512        | UNIT |  |

|--------------------|---------------|---------------------------------------------------------------------|---------------------------------------|---------------------|------------------|------|--------------------|------------------|------------|------|--|

| PAI                | RAMETER       | TEST CONI                                                           | DITIONS                               | MIN                 | TYP <sup>†</sup> | MAX  | MIN                | TYP <sup>†</sup> | MAX        | UNII |  |

| VIK                |               | $V_{CC} = 2.7 V,$                                                   | $I_I = -18 \text{ mA}$                |                     |                  | -1.2 |                    |                  | -1.2       | V    |  |

|                    |               | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V},$                         | $I_{OH} = -100  \mu A$                | V <sub>CC</sub> -0. | 2                |      | V <sub>CC</sub> -0 | .2               |            |      |  |

|                    |               | $V_{CC} = 2.7 \text{ V},$                                           | I <sub>OH</sub> = -3 mA               | 2.4                 |                  |      | 2.4                |                  |            |      |  |

| Vон                |               |                                                                     | I <sub>OH</sub> = -8 mA               | 2.4                 |                  |      | 2.4                |                  |            | V    |  |

|                    |               | VCC = 3 V                                                           | I <sub>OH</sub> = -24 mA              | 2                   |                  |      |                    |                  |            |      |  |

|                    |               |                                                                     | $I_{OH} = -32 \text{ mA}$             |                     |                  |      | 2                  |                  |            |      |  |

|                    |               | V00 = 2.7.V                                                         | I <sub>OL</sub> = 100 μA              |                     |                  | 0.2  |                    |                  | 0.2        |      |  |

|                    |               | V <sub>CC</sub> = 2.7 V                                             | I <sub>OL</sub> = 24 mA               |                     |                  | 0.5  |                    |                  | 0.5        |      |  |

| VOL                |               |                                                                     | I <sub>OL</sub> = 16 mA               |                     |                  | 0.4  |                    |                  | 0.4        | V    |  |

| \ VOL              | OL .          | VCC = 3 V                                                           | $I_{OL} = 32 \text{ mA}$              |                     |                  | 0.5  |                    |                  | 0.5        | V    |  |

|                    |               | 1 100 - 3 1                                                         | I <sub>OL</sub> = 48 mA               |                     |                  | 0.55 |                    |                  |            |      |  |

|                    |               |                                                                     | $I_{OL} = 64 \text{ mA}$              |                     |                  |      |                    |                  | 0.55       |      |  |

|                    | CLK, LE, TCK  | $V_{CC} = 3.6 \text{ V},$                                           | $V_I = V_{CC}$ or GND                 | ±1                  |                  |      |                    |                  | ±1         |      |  |

|                    | CLK, LE, TCK  | $V_{CC} = 0 \text{ or } 3.6 \text{ V},$                             | V <sub>I</sub> = 5.5 V                |                     |                  | 10   |                    |                  | 10         |      |  |

|                    |               |                                                                     | V <sub>I</sub> = 5.5 V                |                     |                  | 5 5  |                    |                  |            |      |  |

| ١,,                | OE, TDI, TMS  | V <sub>CC</sub> = 3.6 V                                             | $V_I = V_{CC}$                        |                     | Ţ,               | 1    |                    |                  | 1          | μА   |  |

| 1                  |               |                                                                     | V <sub>I</sub> = 0                    | -25                 | 77               | -100 | -25                |                  | -100       | μι   |  |

|                    | A or B ports‡ | V <sub>CC</sub> = 3.6 V                                             | V <sub>I</sub> = 5.5 V                |                     | 15               | 20   |                    |                  | 20         |      |  |

|                    |               |                                                                     | VI = VCC                              | à                   | 5                | 1    |                    |                  | 1          |      |  |

|                    |               |                                                                     | V <sub>I</sub> = 0                    | 0                   | /                | -5   |                    |                  | <b>–</b> 5 |      |  |

| l <sub>off</sub>   |               | $V_{CC} = 0$ ,                                                      | $V_I$ or $V_O = 0$ to 4.5 $V$         | Q                   |                  |      |                    |                  | ±100       | μΑ   |  |

| lozh               |               | V <sub>CC</sub> = 3.6 V,                                            | VO = 3 V                              |                     |                  | 1    |                    |                  | 1          | μΑ   |  |

| lozL               |               | $V_{CC} = 3.6 \text{ V},$                                           | $V_0 = 0.5 \text{ V}$                 |                     |                  | -1   |                    |                  | -1         | μΑ   |  |

| lozpu              |               | $V_{CC} = 0 \text{ to } 1.5 \text{ V},$                             | $V_0 = 0.5 \text{ V or } 3 \text{ V}$ |                     |                  | ±50  |                    |                  | ±50        | μΑ   |  |

| lozpd              |               | $V_{CC} = 1.5 \text{ V to } 0,$                                     | $V_0 = 0.5 \text{ V or } 3 \text{ V}$ |                     |                  | ±50  |                    |                  | ±50        | μΑ   |  |

|                    |               | V <sub>CC</sub> = 3.6 V,                                            | Outputs high                          |                     | 0.6              | 2    |                    | 0.6              | 2          |      |  |

| Icc                |               | $I_{O} = 0$ ,                                                       | Outputs low                           |                     | 18               | 24   |                    | 18               | 24         | mA   |  |

|                    |               | $V_I = V_{CC}$ or GND                                               | Outputs disabled                      |                     | 0.6              | 2    |                    | 0.6              | 2          |      |  |

| ∆l <sub>CC</sub> § |               | $V_{CC}$ = 3 V to 3.6 V, One inp<br>Other inputs at $V_{CC}$ or GNI |                                       |                     |                  | 0.5  |                    |                  | 0.5        | mA   |  |

| Ci                 |               | V <sub>I</sub> = 3 V or 0                                           |                                       |                     | 4                |      |                    | 4                |            | pF   |  |

| C <sub>io</sub>    |               | V <sub>O</sub> = 3 V or 0                                           |                                       |                     | 10               |      |                    | 10               |            | pF   |  |

| Co                 |               | V <sub>O</sub> = 3 V or 0                                           |                                       |                     | 8                |      |                    | 8                |            | pF   |  |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>‡</sup> Unused pins at V<sub>CC</sub> or GND

<sup>§</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

SCBS711 - OCTOBER 1997

# timing requirements over recommended operating free-air temperature range (unless otherwise noted) (normal mode) (see Figure 14)

|                 |                               |                                    |                                                            |     | SN54LV                             | T18512 |                         | SN74LVT18512 |      |     |     |     |

|-----------------|-------------------------------|------------------------------------|------------------------------------------------------------|-----|------------------------------------|--------|-------------------------|--------------|------|-----|-----|-----|

|                 |                               |                                    | V <sub>CC</sub> = 3.3 V<br>± 0.3 V V <sub>CC</sub> = 2.7 V |     | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |        | V <sub>CC</sub> = 2.7 V |              | UNIT |     |     |     |

|                 |                               |                                    |                                                            | MIN | MAX                                | MIN    | MAX                     | MIN          | MAX  | MIN | MAX |     |

| fclock          | Clock frequency               | CLKAB or CLKBA                     |                                                            | 0   | 100                                | 0      | 80                      | 0            | 100  | 0   | 80  | MHz |

|                 | t <sub>w</sub> Pulse duration | CLKAB or CLKBA hig                 | h or low                                                   | 4.4 |                                    | 5.6    |                         | 4.4          |      | 5.6 |     | ns  |

| t <sub>W</sub>  | Puise duration                | LEAB or LEBA high                  |                                                            | 3   |                                    | 43     |                         | 3            |      | 3   |     | 115 |

|                 |                               | A before CLKAB↑ or B before CLKBA↑ |                                                            | 2.8 |                                    | 3      |                         | 2.8          |      | 3   |     |     |

| t <sub>su</sub> | Setup time                    | A before LEAB↓ or                  | CLK high                                                   | 1.5 | .Ú                                 | 0.7    |                         | 1.5          |      | 0.7 |     | ns  |

|                 |                               | B before LEBA↓                     | CLK low                                                    | 1.6 | 20                                 | 1.6    |                         | 1.6          |      | 1.6 |     |     |

| th              | Hold time                     | A after CLKAB↑ or B after CLKBA↑   |                                                            | 1.4 | PAG                                | 1.1    | ·                       | 1.4          | ·    | 1.1 | ·   | ns  |

|                 |                               | A after LEAB↓ or B at              | fter LEBA↓                                                 | 3.1 |                                    | 3.5    |                         | 3.1          |      | 3.5 |     |     |

# timing requirements over recommended operating free-air temperature range (unless otherwise noted) (test mode) (see Figure 14)

|                |                 |                                                |                                                            | SN54LV | T18512                             |     |                         | SN74LV | T18512 |     |     |

|----------------|-----------------|------------------------------------------------|------------------------------------------------------------|--------|------------------------------------|-----|-------------------------|--------|--------|-----|-----|

|                |                 |                                                | V <sub>CC</sub> = 3.3 V<br>± 0.3 V V <sub>CC</sub> = 2.7 V |        | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |     | V <sub>CC</sub> = 2.7 V |        | UNIT   |     |     |

|                |                 |                                                | MIN                                                        | MAX    | MIN                                | MAX | MIN                     | MAX    | MIN    | MAX |     |

| fclock         | Clock frequency | TCK                                            | 0                                                          | 50     | 0                                  | 40  | 0                       | 50     | 0      | 40  | MHz |

| t <sub>W</sub> | Pulse duration  | TCK high or low                                | 9.5                                                        |        | 10.5                               |     | 9.5                     |        | 10.5   |     | ns  |

|                |                 | A, B, CLK, LE, or <del>OE</del><br>before TCK↑ | 6.5                                                        |        | 147                                |     | 6.5                     |        | 7      |     |     |

| tsu            | Setup time      | TDI before TCK↑                                | 2.5                                                        |        | 3.5                                |     | 2.5                     |        | 3.5    |     | ns  |

|                |                 | TMS before TCK↑                                | 2.5                                                        | .Ú     | 3.5                                |     | 2.5                     |        | 3.5    |     |     |

|                |                 | A, B, CLK, LE, or OE after TCK↑                | 1.7                                                        | 2      | 1                                  |     | 1.7                     |        | 1      |     |     |

| th             | Hold time       | TDI after TCK↑                                 | 1.5                                                        | 20     | 1                                  |     | 1.5                     |        | 1      |     | ns  |

|                |                 | TMS after TCK↑                                 | 1.5                                                        | 4      | 1                                  |     | 1.5                     |        | 1      |     |     |

| t <sub>d</sub> | Delay time      | Power up to TCK↑                               | 50                                                         |        | 50                                 |     | 50                      |        | 50     |     | ns  |

| t <sub>r</sub> | Rise time       | V <sub>CC</sub> power up                       | 1                                                          |        | 1                                  |     | 1                       |        | 1      |     | μs  |

SCBS711 - OCTOBER 1997

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted) (normal mode) (see Figure 14)

|                  |                 |        | SN54LVT18512 |                                    |     |                         |     |                         |     |       |      |

|------------------|-----------------|--------|--------------|------------------------------------|-----|-------------------------|-----|-------------------------|-----|-------|------|

| PARAMETER        | FROM<br>(INPUT) |        |              | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |     | V <sub>CC</sub> = 2.7 V |     | 3.3 V V <sub>CC</sub> = |     | 2.7 V | UNIT |

|                  |                 |        | MIN          | MAX                                | MIN | MAX                     | MIN | MAX                     | MIN | MAX   |      |

| f <sub>max</sub> | CLKAB or CLKBA  |        | 100          |                                    | 80  |                         | 100 |                         | 80  |       | MHz  |

| <sup>t</sup> PLH | A or B          | B or A | 1.5          | 5.1                                |     | 5.8                     | 1.5 | 4.9                     |     | 5.6   | ns   |

| <sup>t</sup> PHL | AUIB            | BOIA   | 1.5          | 5.1                                | N.  | 5.8                     | 1.5 | 4.9                     |     | 5.6   | 115  |

| t <sub>PLH</sub> | CLKAB or CLKBA  | B or A | 1.5          | 6.3                                | 14  | 7.2                     | 1.5 | 5.8                     |     | 6.8   | ns   |

| t <sub>PHL</sub> | CLNAD OF CLNBA  | BULA   | 1.5          | 6.3                                | 46  | 7.2                     | 1.5 | 5.8                     |     | 6.8   | 115  |

| <sup>t</sup> PLH | LEAB or LEBA    | B or A | 1.5          | 7.8                                | ,   | 9.2                     | 1.5 | 7.4                     |     | 8.4   | no   |

| t <sub>PHL</sub> | LEAD OF LEDA    | BULA   | 1.5          | 6                                  |     | 6.6                     | 1.5 | 5.7                     |     | 6.4   | ns   |

| <sup>t</sup> PZH | OEAB or OEBA    | P.or A | 1.5          | 7.6                                |     | 8.5                     | 1.5 | 7.1                     |     | 8.3   | no   |

| <sup>t</sup> PZL | OEAB OF OEBA    | B or A | 1.5          | 7.6                                |     | 8.5                     | 1.5 | 7.1                     |     | 8.3   | ns   |

| <sup>t</sup> PHZ | OF AD OFDA      | B or A | 2.5          | 8.3                                |     | 8.8                     | 2.5 | 7.8                     |     | 8.4   | ns   |

| t <sub>PLZ</sub> | OEAB or OEBA    | BULA   | 2.5          | 8.3                                |     | 8.8                     | 2.5 | 7.8                     |     | 8.4   | 115  |

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted) (test mode) (see Figure 14)

|                  |                 | ТО<br>(ОИТРИТ) |     | SN54LV                             | T18512 |                         |     |              |       |       |      |  |

|------------------|-----------------|----------------|-----|------------------------------------|--------|-------------------------|-----|--------------|-------|-------|------|--|

| PARAMETER        | FROM<br>(INPUT) |                |     | V <sub>CC</sub> = 3.3 V<br>± 0.3 V |        | V <sub>CC</sub> = 2.7 V |     | 3.3 V<br>3 V | VCC = | 2.7 V | UNIT |  |