- Designed to Reduce Reflection Noise

- Repetitive Peak Forward Current to 200 mA

- 12-Bit Array Structure Suited for Bus-Oriented Systems

#### description/ordering information

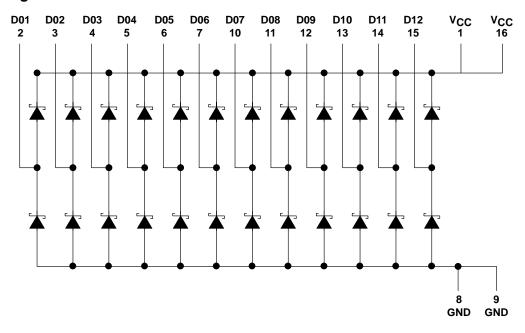

This Schottky barrier diode bus-termination array is designed to reduce reflection noise on memory bus lines. This device consists of a 12-bit high-speed Schottky diode array suitable for clamping to  $V_{CC}$  and/or GND.

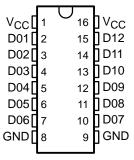

# D, N, NS, OR PW PACKAGE (TOP VIEW)

#### ORDERING INFORMATION

| TA          | PACKAGE <sup>†</sup> |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>Marking |  |

|-------------|----------------------|---------------|--------------------------|---------------------|--|

|             | PDIP – N             | Tube          | SN74S1051N               | SN74S1051N          |  |

|             | SOIC - D             | Tube          | SN74S1051D               | S1051               |  |

| 0°C to 70°C | 3010 - 0             | Tape and reel | SN74S1051DR              | 31031               |  |

|             | SOP - NS             | Tape and reel | SN74S1051NSR             | 74S1051             |  |

|             | TSSOP – PW           | Tape and reel | SN74S1051PWR             | S1051               |  |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

## schematic diagrams

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# SN74S1051 12-BIT SCHOTTKY BARRIER DIODE BUS-TERMINATION ARRAY

SDLS018B - SEPTEMBER 1990 - REVISED MARCH 2003

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Steady-state reverse voltage, V <sub>R</sub>                            |                                             | 7 V            |

|-------------------------------------------------------------------------|---------------------------------------------|----------------|

| Continuous forward current, IF: Any D terminal                          |                                             |                |

| Total through a                                                         | II GND or V <sub>CC</sub> terminals         | 170 mA         |

| Repetitive peak forward current <sup>‡</sup> , I <sub>FRM</sub> : Any D |                                             |                |

| Total th                                                                | nrough all GND or V <sub>CC</sub> terminals | 1 A            |

| Package thermal impedance, $\theta_{JA}$ (see Note 1):                  |                                             |                |

|                                                                         | N package                                   | 67°C/W         |

|                                                                         | NS package                                  | 64°C/W         |

|                                                                         | PW package                                  | 108°C/W        |

| Operating free-air temperature range                                    |                                             | 0°C to 70°C    |

| Storage temperature range, T <sub>stg</sub>                             |                                             | –65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: The package thermal impedance is calculated in accordance with JESD 51-7.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

#### single-diode operation (see Note 2)

| PARAMETER                |                        | TEST CONDITIONS    |                         | MIN TYP§ | MAX  | UNIT |

|--------------------------|------------------------|--------------------|-------------------------|----------|------|------|

|                          | Chatia famuand valtana | To V <sub>CC</sub> | I <sub>F</sub> = 18 mA  | 0.85     | 1.05 | 3 V  |

| \/_                      |                        |                    | I <sub>F</sub> = 50 mA  | 1.05     | 1.3  |      |

| V <sub>F</sub> Static fo | Static forward voltage | From GND           | I <sub>F</sub> = 18 mA  | 0.75     | 0.95 |      |

|                          |                        |                    | I <sub>F</sub> = 50 mA  | 0.95     | 1.2  |      |

| V <sub>FM</sub>          | Peak forward voltage   |                    | I <sub>F</sub> = 200 mA | 1.45     |      | V    |

|                          | Static reverse current | To V <sub>CC</sub> | V <sub>R</sub> = 7 V    |          | 5    |      |

| IR                       | Static reverse current | From GND           | vR = 1 v                |          | 5    | μΑ   |

| C.                       | Total capacitance      | $V_R = 0 V$        | f = 1 MHz               | 8        | 16   | pF   |

| Ct                       |                        | $V_{R} = 2 V$ ,    | f = 1 MHz               | 4        | 8    | Pi   |

<sup>§</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

NOTE 2: Test conditions and limits apply separately to each of the diodes. The diodes not under test are open-circuited during the measurement of these characteristics.

## multiple-diode operation

|      | PARAMETER TEST CONDITIONS  |                                     | MIN        | TYP§ | MAX  | UNIT |     |

|------|----------------------------|-------------------------------------|------------|------|------|------|-----|

|      | Internal crosstalk current | Total I <sub>F</sub> current = 1 A, | See Note 3 |      | 0.8  | 2    | m ^ |

| l 'x |                            | Total IF current = 198 mA,          | See Note 3 |      | 0.02 | 0.2  | mA  |

<sup>§</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

NOTE 3: I<sub>X</sub> is measured under the following conditions with one diode static, all others switching:

Switching diodes:  $t_W = 100 \mu s$ , duty cycle = 20%

Static diode:  $V_R = 5 V$

The static diode input current is the internal crosstalk current,  $I_{\rm X}$ .

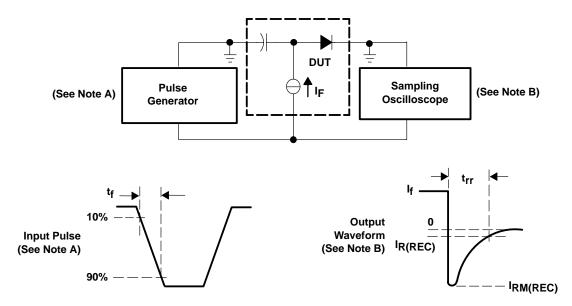

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted) (see Figures 1 and 2)

|                 | PARAMETER TEST CONDITIONS |                        |                                |                              |                    | MIN | TYP | MAX | UNIT |

|-----------------|---------------------------|------------------------|--------------------------------|------------------------------|--------------------|-----|-----|-----|------|

| t <sub>rr</sub> | Reverse recovery time     | $I_F = 10 \text{ mA},$ | $I_{RM(REC)} = 10 \text{ mA},$ | $I_{R(REC)} = 1 \text{ mA},$ | $R_L = 100 \Omega$ |     | 8   | 16  | ns   |

<sup>‡</sup> These values apply for  $t_W \le 100 \mu s$ , duty cycle  $\le 20\%$ .

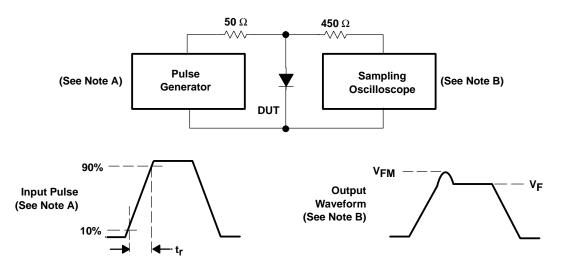

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. The input pulse is supplied by a pulse generator having the following characteristics:  $t_f = 20$  ns,  $Z_O = 50 \Omega$ , freq = 500 Hz, duty cycle = 1%.

- B. The output waveform is monitored by an oscilloscope having the following characteristics:  $t_{\Gamma} \le 350$  ps,  $R_i = 50 \Omega$ ,  $C_i \le 5$  pF.

Figure 1. Forward Recovery Voltage

- NOTES: A. The input pulse is supplied by a pulse generator having the following characteristics:  $t_f = 0.5$  ns,  $Z_O = 50 \Omega$ ,  $t_W \ge 50$  ns, duty cycle = 1%.

- B. The output waveform is monitored by an oscilloscope having the following characteristics:  $t_r \le 350$  ps,  $R_i = 50 \Omega$ ,  $C_i \le 5$  pF.

Figure 2. Reverse Recovery Time

#### APPLICATION INFORMATION

Large negative transients at the inputs of memory devices (DRAMs, SRAMs, EPROMs, etc.) or on the CLOCK lines of many clocked devices can result in improper operation of the devices. The SN74S1051 diode termination array helps suppress negative transients caused by transmission-line reflections, crosstalk, and switching noise.

Diode terminations have several advantages when compared to resistor termination schemes. Split-resistor or Thevenin-equivalent termination can cause a substantial increase in power consumption. The use of a single resistor to ground to terminate a line usually results in degradation of the output high level, resulting in reduced noise immunity. Series damping resistors placed on the outputs of the driver reduce negative transients, but they also can increase propagation delays down the line because a series resistor reduces the output drive capability of the driving device. Diode terminations have none of these drawbacks.

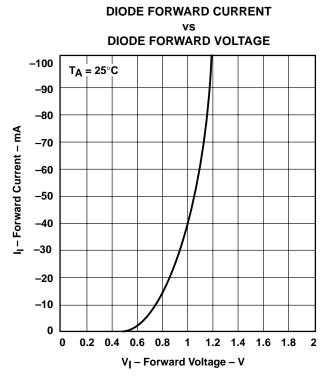

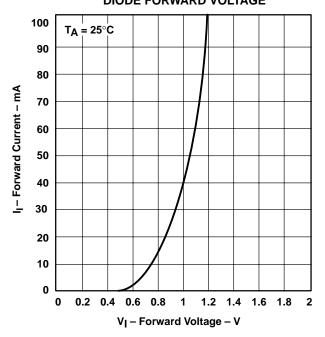

The operation of the diode arrays in reducing negative transients is explained in the following figures. The diode conducts current when the voltage reaches a negative value large enough for the diode to turn on. Suppression of negative transients is tracked by the current-voltage characteristic curve for that diode. Typical current-versus-voltage curves for the SN74S1051 are shown in Figures 3 and 4.

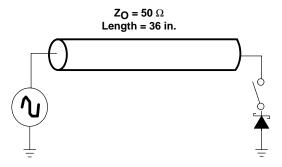

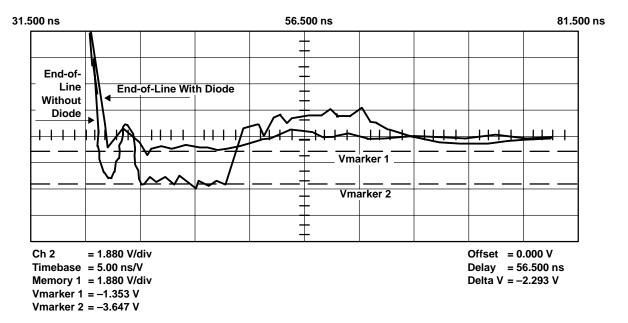

To illustrate how the diode arrays act to reduce negative transients at the end of a transmission line, the test setup in Figure 5 was evaluated. The resulting waveforms with and without the diode are shown in Figure 6.

The maximum effectiveness of the diode arrays in suppressing negative transients occurs when the diode arrays are placed at the end of a line and/or the end of a long stub branching off a main transmission line. The diodes can also reduce the negative transients that occur due to discontinuities in the middle of a line. An example of this is a slot in a backplane that is provided for an add-on card.

Figure 3. Typical Input Current vs Input Voltage (Lower Diode)

# DIODE FORWARD CURRENT vs DIODE FORWARD VOLTAGE

Figure 4. Typical Input Current vs Input Voltage (Upper Diode)

#### **APPLICATION INFORMATION**

Figure 5. Diode Test Setup

Figure 6. Reduction of Negative Transients at the End of a Transmission Line

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated