**N PACKAGE**

SLLS026C - JANUARY 1987 - REVISED JULY 1990

- IEEE 802.3 1BASE5 Driver and Receiver

- On-Chip Receiver Squelch With Adjustable Threshold

- Adjustable Squelch Delay

- Direct TTL-Level Squelch Output

- Squelch Circuit Allows for External Noise Filtering

- Two Driver-Enable Options

- On-Chip Start-of-Idle Detection and Disable

- Driver Provides 2-V Minimum into a 50-Ω

Differential Load Allowing for Use With Doubly-Terminated Lines and Multipoint Architectures

- On-Chip Driver Slew-Rate Control for Very Closely Matched Output Rise and Fall Times

#### (TOP VIEW) **DRDLAJ** 16 $V_{CC}$ 15 DATEN DRO + 1 2 DRO – **1** 3 14**∏** DRI 13 DLEN SQDLAJ [ RXI + **1** 5 12 RXO 11 SQO RXI – **∏** 6 10 SQDLI SQTHAJ [] GND [ 9 SQRXO

#### **Function Tables**

#### **DRIVER**

|     | INPUTS |      | OUTI  | PUTS  |

|-----|--------|------|-------|-------|

| DRI | DATEN  | DLEN | DRO + | DRO - |

| L   | L      | Х    | L     | Н     |

| Н   | L      | Χ    | Н     | L     |

| X   | Н      | Н    | Z     | Z     |

| Н   | Н      | L    | H†    | L†    |

| L   | Н      | L    | ∟‡    | н‡    |

#### **RECEIVER§**

| CONDITION           | INPU  | JTS   | OUTPUTS |     |  |

|---------------------|-------|-------|---------|-----|--|

| CONDITION           | RXI + | RXI – | RXO SO  | SQO |  |

| No active signal ¶  | Х     | Χ     | Н       | Н   |  |

| A ativa ai ana al ¶ | L     | Н     | L       | L   |  |

| Active signal ¶     | Н     | L     | Н       | L   |  |

<sup>†</sup> This condition is valid during the time period set by DRDLAJ following a rising transition on DRI. Following this, when a subsequent positive transition does not occur on DRI, the outputs go to the high-impedance state.

<sup>&</sup>lt;sup>‡</sup> This condition is valid when it occurs within the enable time set by DRDLAJ after a rising transition on DRI. Otherwise, the outputs are in the high-impedance state.

<sup>§</sup> Pins 9 and 10 are tied together.

$<sup>\</sup>P$  An active signal is one that has an amplitude greater than the threshold level set by SQTHAJ.

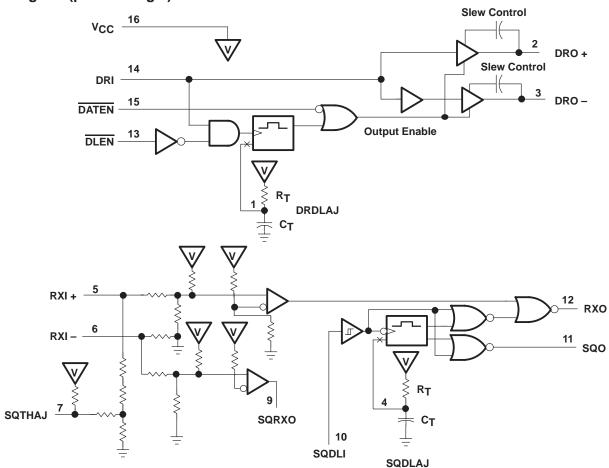

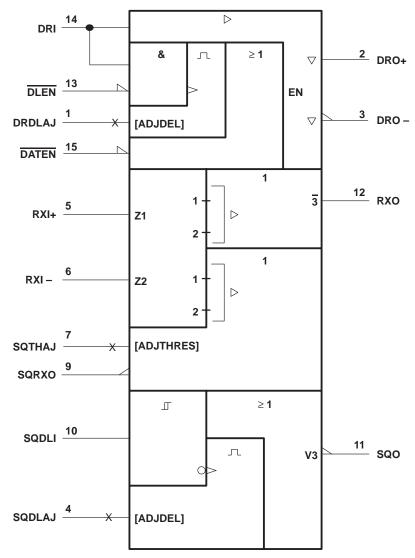

# logic diagram (positive logic)

## logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

## description

The SN75061 is a single-channel driver/receiver pair designed for use in IEEE 802.3, 1BASE5 applications as well as other general data communications circuits. The SN75061 offers both a driver and a receiver that are easily configured for use with a variety of controllers and data encoder/decoders.

The receiver features a full analog squelch circuit with an adjustable threshold and a programmable squelch delay. Internal nodes of the squelch circuitry are brought out to external connections to allow for the insertion of noise-filtering circuitry of the designer's choice.

As with the receiver, the driver offers a variety of implementation options. Driver enabling may be directly controlled by an external logic input or by use of an on-chip one-shot that is retriggered as long as data is being sent to the driver. The driver then automatically goes to the high-impedance state when end-of-packet common phrase occurs. The driver features internal slew-rate control for optimal matching of rise and fall times allowing for reduction of driver-induced jitter.

# SN75061 DRIVER/RECEIVER PAIR WITH SOUELCH

SLLS026C - JANUARY 1987 - REVISED JULY 1990

#### receiver

The SN75061 receiver implements full analog squelch functions by integrating both a separate, parallel squelch receiver with an externally programmable threshold, and a programmable one-shot. The output of the squelch receiver and the input to the high-level, dc-triggered one-shot are brought out to external connections. These pins can be shorted for direct implementation or used for the insertion of noise-filtering circuitry of the implementer's design. The receiver one-shot can be effectively bypassed by applying a high logic level to SQDLI. The squelch threshold may be set externally by applying an external voltage set to a level that is –2 times the desired threshold voltage. When SQTHAJ is left open, the squelch receiver defaults to its internal preset value of –600 mV. The receiver also outputs a high logic squelch signal when there is not any active data present at the receiver inputs. When data is not present on the transmission line, the receiver output assumes a high level. The unsquelch duration is set externally with an R-C combination at SQDLAJ.

#### driver

The driver offers a variety of implementation options. Driver enabling may be controlled directly by an active-low, external logic input on  $\overline{\text{DATEN}}$  or by use of another on-chip one-shot that retriggers with positive-going transitions on the driver input line. When positive transition does not occur within the pulse duration set by an external R-C combination, the one-shot times out and the driver is automatically put into a high-impedance state. When operating in the delay-enable mode, the 2-bit-time, high-level, start-of-idle pulse prescribed by IEEE 802.3 1BASE5 causes the one-shot to time out and automatically place the driver outputs in the high-impedance state. This delay time is also adjustable for use in other applications. The driver implements an output slew-rate control that is internally set for nominally 40 mV/ns. (This is roughly a 100-ns peak-to-peak differential transition time.) The driver outputs are capable of driving a 50- $\Omega$  differential load with a minimum output level of 2 V. Short-circuit output current is greater than 100 mA.

SLLS026C - JANUARY 1987 - REVISED JULY 1990

## **Terminal Functions**

| PIN    |     | DESCRIPTION                                                                                                                                                                                                                                                             |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | DESCRIPTION                                                                                                                                                                                                                                                             |

| DATEN  | 15  | Driver data enable. When this sign is low, driver outputs are in an active state. When the signal is high, the driver outputs are in a high-impedance state when $\overline{\text{DLEN}}$ is also high.                                                                 |

| DLEN   | 13  | Driver delay enable. When this signal is low and DATEN is high, the driver outputs are active for a period of time set by DRDLAJ after a positive-going transition on DRI. When there is not any active data on DRI, the outputs are in a high-impedance state.         |

| DRDLAJ | 1   | Driver delay adjust is a connection for the external R-C combination that determines the duration of the driver output active state after a positive transition on DRI when DLEN is low and DATEN is high.                                                              |

| DRI    | 14  | Driver data input                                                                                                                                                                                                                                                       |

| DRO+   | 2   | Noninverting driver output                                                                                                                                                                                                                                              |

| DRO-   | 3   | Inverting driver output                                                                                                                                                                                                                                                 |

| GND    | 8   | Ground. Common for all voltages                                                                                                                                                                                                                                         |

| RXI+   | 5   | Noninverting receiver input                                                                                                                                                                                                                                             |

| RXI-   | 6   | Inverting receiver input                                                                                                                                                                                                                                                |

| RXO    | 12  | Main receiver input                                                                                                                                                                                                                                                     |

| SQDLAJ | 4   | Squelch delay adjust is a connection for an external R-C combination that determines the duration of the receiver unsquelch after a negative-going transition on SQDLI.                                                                                                 |

| SQDLI  | 10  | Squelch delay input is the input to the one-shot that controls the duration of the receiver unsquelch period. The main receiver output remains unsquelched as long as SQDLI is held high. Timing of the unsquelch period begins on the high-to-low transition of SQDLI. |

| SQO    | 11  | Squelch output is high while the receiver is squelched.                                                                                                                                                                                                                 |

| SQRXO  | 9   | Squelch receiver output is high only when the differential receiver input exceeds the threshold set by SQTHAJ.                                                                                                                                                          |

| SQTHAJ | 7   | Squelch receiver threshold adjust. The voltage at this input determines the threshold of the squelch receiver in a ratio of $-2$ , SQTHAJ to threshold. When the receiver is left open, the squelch receiver threshold defaults to $-600$ mV.                           |

| Vcc    | 16  | Supply-voltage input                                                                                                                                                                                                                                                    |

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>CC</sub>                                                   | 7 V            |

|-----------------------------------------------------------------------------------|----------------|

| Input voltage, V <sub>I</sub> (any logic input)                                   |                |

| Receiver differential input voltage                                               |                |

| Receiver input voltage                                                            | ±15 V          |

| Driver output voltage                                                             | 0.5 V to 15 V  |

| Continuous total dissipation at (or below) 25°C free-air temperature (see Note 1) | 1150 mW        |

| Operating free-air temperature range, T <sub>A</sub>                              | 0°C to 70°C    |

| Storage temperature range, T <sub>stq</sub>                                       | −65°C to 150°C |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                      |                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: For operation above 25°C free-air temperature, derate to 736 mW at 70°C at the rate of 9.2 mW/°C.

SLLS026C - JANUARY 1987 - REVISED JULY 1990

# recommended operating conditions

|                                                                  | MIN  | NOM         | MAX  | UNIT |

|------------------------------------------------------------------|------|-------------|------|------|

| Supply voltage, V <sub>CC</sub>                                  | 4.75 | 5           | 5.25 | V    |

| Driver high-level input voltage, V <sub>IH</sub>                 | 2    |             |      | V    |

| Driver low-level input voltage, V <sub>IL</sub>                  |      |             | 0.8  | V    |

| Receiver common-mode input voltage, V <sub>IC</sub> (see Note 2) | -2.5 |             | 5    | V    |

| Driver high-level output current, I <sub>OH</sub>                |      |             | -150 | mA   |

| Driver low-level output current, IOL                             |      |             | 150  | mA   |

| External timing resistance, Rext                                 | 5    |             | 260  | kΩ   |

| External timing capacitance, C <sub>ext</sub>                    | No   | restriction | on   |      |

| Operating free-air temperature, T <sub>A</sub>                   | 0    |             | 70   | °C   |

NOTE 2: The algebraic convention, in which the less-positive (more negative) limit is designated as minimum, is used in this data sheet for common-mode input voltage V<sub>IC</sub> and threshold levels V<sub>IT+</sub> and V<sub>IT+</sub>.

# electrical characteristics over recommended operating free-air temperature and supply voltage ranges (unless otherwise noted)

## driver

|                  | PARAMETER                                                               |                                    | TEST CONDITIONS                 |      | TYP <sup>†</sup> | MAX  | UNIT |

|------------------|-------------------------------------------------------------------------|------------------------------------|---------------------------------|------|------------------|------|------|

| VIK              | Input clamp voltage                                                     | I <sub>I</sub> = -18 mA            |                                 |      |                  | -1.5 | V    |

| \/               | Differential cutout valte as                                            | R <sub>L</sub> = 50 Ω              |                                 | 2    | 2.4              | 3.3  | V    |

| VOD              | Differential output voltage                                             | R <sub>L</sub> = 115 Ω             |                                 |      |                  | 3.65 | v    |

| ΔV <sub>OD</sub> | Change in differential output voltage for a change in logic input state |                                    |                                 |      |                  | 50   | mV   |

| lн               | High-level input current                                                | V <sub>I</sub> = 2 4 V             |                                 |      |                  | 20   | μΑ   |

| I <sub>Ι</sub> Γ | Low-level input current                                                 | V <sub>I</sub> = 0.5 V             |                                 | ±100 |                  | -35  | μΑ   |

| los              | Short-circuit output current                                            | $V_0 = 0 \text{ or } 6 \text{ V},$ | V <sub>I</sub> = 0.8 V or 2.5 V |      |                  | ±300 | mA   |

| lo-              | High-impedance output current                                           | Vac = 5.25.V                       | V <sub>OC</sub> = 10 V          |      |                  | 100  |      |

| loz              | riigii-iiripedarice odipdi curretti                                     | $V_{CC} = 5.25 \text{ V}$          | VOC = 0                         |      |                  | -100 | μΑ   |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

SLLS026C - JANUARY 1987 - REVISED JULY 1990

# electrical characteristics over recommended operating free-air temperature and supply voltage ranges (unless otherwise noted) (continued)

## receiver

|                       | PARAMETER                                                         |       | TEST C                                                                     | ONDITIONS                                                      | MIN  | TYP <sup>†</sup> | MAX  | UNIT   |  |

|-----------------------|-------------------------------------------------------------------|-------|----------------------------------------------------------------------------|----------------------------------------------------------------|------|------------------|------|--------|--|

| VIK                   | Input clamp voltage, squelch delay                                |       | $I_{I} = -18 \text{ mA}$                                                   |                                                                |      |                  | -1.5 | V      |  |

| V <sub>IT+</sub>      | Positive-going input threshold volta                              | ge    | $V_0 = 2.7 V$ ,                                                            | $I_{O} = -0.4 \text{ mA}$                                      |      |                  | 50   | mV     |  |

| V <sub>IT</sub> _     | Negative-going input threshold volta                              | age   | V <sub>O</sub> = 0.5 V,                                                    | I <sub>O</sub> = 16 mA                                         | -50‡ |                  |      | mV     |  |

| V <sub>hys</sub>      | Hysteresis voltage (V <sub>IT+</sub> – V <sub>IT</sub> _)         |       |                                                                            |                                                                |      | 50               |      | mV     |  |

| V <sub>IC</sub>       | Common-mode input voltage                                         |       |                                                                            |                                                                |      |                  | 5    | V      |  |

|                       |                                                                   | RXO   | $V_{CC} = 4.75 \text{ V},$                                                 | $I_{OH} = -400  \mu A$                                         | 2.7  |                  |      |        |  |

| \/                    | Lligh lovel output voltage                                        | SQO   | SQDLAJ at 0.8 V                                                            |                                                                | 2.7  | 3.5              |      |        |  |

| VOH                   | High-level output voltage                                         | SQRXO | V <sub>CC</sub> = 4.75 V,<br>V <sub>ID(RXI)</sub> = -0.7 V,                | I <sub>OH</sub> = -20 μA,<br>SQDLAJ open                       | 2.7  | 4.65             |      | V      |  |

|                       |                                                                   | RXO   |                                                                            | I <sub>OL</sub> = 8 mA                                         |      |                  | 0.45 | $\Box$ |  |

|                       |                                                                   |       | I <sub>OL</sub> = 8 mA<br>V <sub>CC</sub> = 4.75 V, I <sub>OL</sub> = 8 mA | I <sub>OL</sub> = 16 mA                                        |      |                  | 0.5  | V      |  |

| VOL                   | Low-level output voltage                                          | SQO   |                                                                            | I <sub>OL</sub> = 8 mA                                         |      | 0.35             | 0.5  |        |  |

|                       |                                                                   | SQRXO |                                                                            |                                                                |      | 0.45             | v    |        |  |

|                       |                                                                   | SQRXO | $V_{ID(RXI)} = 50 \text{ mV}$                                              | I <sub>OL</sub> = 16 mA                                        |      |                  | 0.5  |        |  |

| lн                    | High-level input current                                          | SQDLI | V <sub>I</sub> = 2.4 V                                                     |                                                                |      |                  | 20   | μΑ     |  |

| I <sub>IL</sub>       | Low-level input current                                           | SQDLI | V <sub>I</sub> = 0.5 V                                                     |                                                                |      |                  | -35  | μΑ     |  |

|                       |                                                                   | RXO   | Vcc = 5.25 V,                                                              | V <sub>O</sub> = 0                                             | -15  |                  | -85  |        |  |

| los                   | Short-circuit output current                                      | SQO   | VCC = 5.25 V,                                                              | ν() = 0                                                        | -15  |                  | -100 | mA     |  |

|                       |                                                                   | SQRXO | V <sub>C</sub> C = 5 V,                                                    | $V_{CC} = 5 \text{ V}, \qquad V_{O} = 0$                       |      | -1               | -1.2 |        |  |

| rį                    | Input resistance                                                  |       |                                                                            |                                                                |      | 10               |      | kΩ     |  |

|                       |                                                                   |       | V 5 V                                                                      | V <sub>IC</sub> = 1.5 V to 3.5 V                               | -525 | -600             | -675 | mV     |  |

| V <sub>IT</sub> -(sq) | Squelch preset input threshold volta                              | age   | V <sub>CC</sub> = 5 V,<br>SQTHAJ open                                      | $V_{IC} = -2.5 \text{ V to } 1.5 \text{ V}$<br>or 3.5 V to 5 V | -500 |                  | -700 | mV     |  |

|                       | Ratio of SQTHAJ input voltage to actual squelch threshold voltage |       | SQTHAJ at 200 mV                                                           | to 4 V                                                         | -1.9 |                  | -2.1 |        |  |

#### driver and receiver

|     | Icc | Supply current | V <sub>CC</sub> = 5.25 V, | Driver outputs disabled, | 70 | mA  |

|-----|-----|----------------|---------------------------|--------------------------|----|-----|

| - 1 | • • |                | No load                   |                          |    | l . |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>‡</sup> The algebraic convention, in which the less positive (more negative) limit is designated as minimum, is used in this data sheet for common-mode input voltage V<sub>IC</sub> and threshold levels V<sub>IT+</sub> and V<sub>IT-</sub>.

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

## driver

|                  | PARAMETER                                                     | TEST CONDI                                                                 | TIONS                                   | MIN | TYP | MAX | UNIT  |

|------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------|-----|-----|-----|-------|

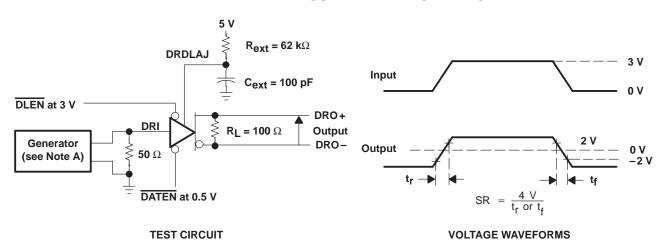

| SR               | Differential-output slew rate                                 | $V_O = -2 \text{ V to 2 V},$<br>$R_L = 100 \Omega \text{ (differential)},$ | See Figure 1                            | 28  | 40  | 52  | mV/ns |

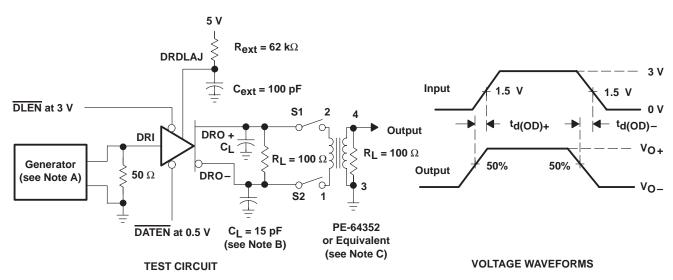

| td(OD)           | Differential-output delay time $(t_d(OD)+ and t_d(OD)-)$      | $C_L$ = 15 pF,<br>$R_L$ =100 $\Omega$ (differential),                      | See Figure 2                            |     |     | 160 | ns    |

|                  | Differential-output delay time difference (td(OD)+ - td(OD)-) | $R_L$ =100 $Ω$ (differential),                                             | See Figure 2                            |     |     | 5   | ns    |

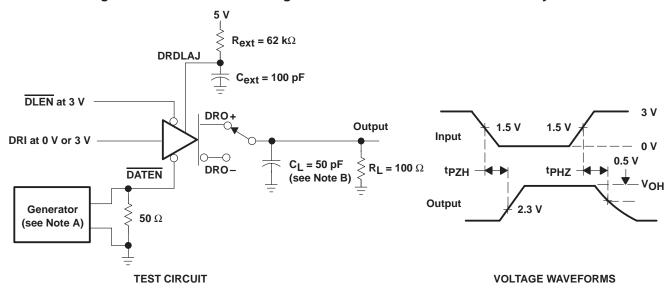

| <sup>t</sup> PHZ | Disable time from DATEN                                       |                                                                            |                                         |     |     | 220 | ns    |

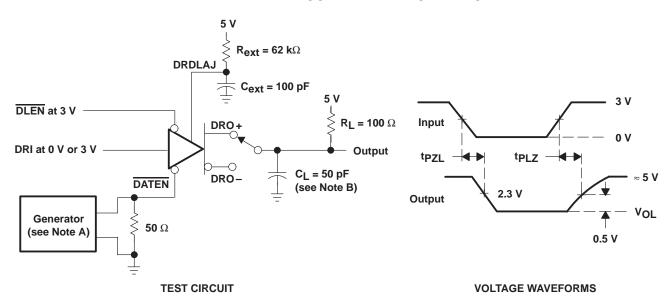

| <sup>t</sup> PLZ | Disable time from DATEN                                       |                                                                            |                                         |     |     | 300 | ns    |

| <sup>t</sup> PZH | Enable time from DATEN                                        | See Figure 3, 4, and 5                                                     |                                         |     |     | 220 | ns    |

| tPZL             | Enable time from DATEN                                        |                                                                            |                                         |     |     | 290 | ns    |

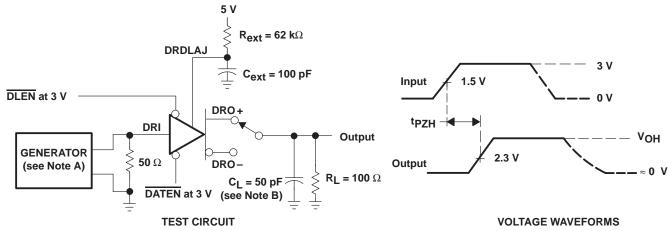

| <sup>t</sup> PZH | Enable time from DLEN                                         |                                                                            |                                         |     |     | 250 | ns    |

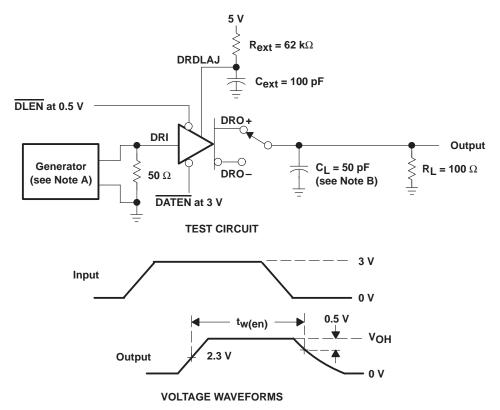

| tw(en)           | Enable pulse duration time (with DLEN low)                    | C <sub>ext</sub> = 100 pF,<br>See Figure 6                                 | $R_{\text{ext}} = 62 \text{ k}\Omega$ , | 2   | 2.5 | 3   | μs    |

## receiver

| PARAMETER            |                                                   | TEST CONDITIONS                           |                                  | MIN | TYP | MAX  | UNIT |

|----------------------|---------------------------------------------------|-------------------------------------------|----------------------------------|-----|-----|------|------|

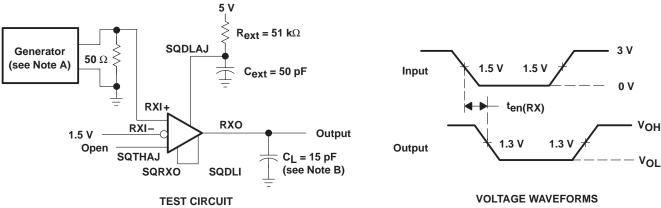

| ten(RX)              | Receiver enable time                              | Squelch off,                              | See Figure 7                     |     | 117 |      | ns   |

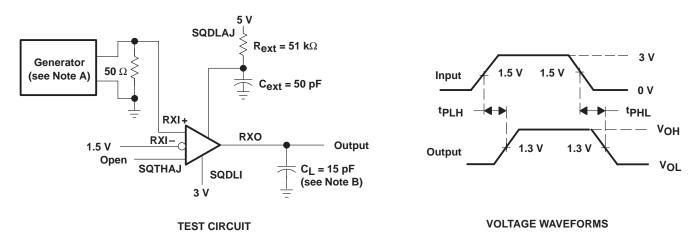

| tPLH                 | Propagation delay time, low- to high level output | Squelch off,                              | See Figure 8                     |     | 20  | 35   | ns   |

| tPHL                 | Propagation delay time, high- to low level output | Squelch off,                              | See Figure 8                     |     | 22  | 35   | ns   |

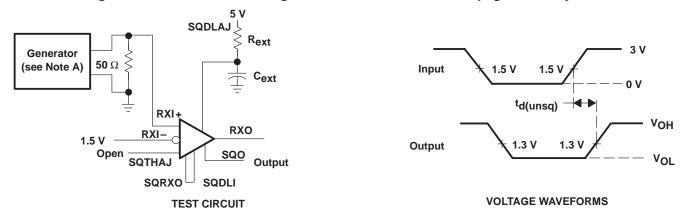

|                      | Heavy slab dalay time                             | C <sub>ext</sub> = 50 pF,<br>See Figure 9 | $R_{ext} = 51 \text{ k}\Omega,$  | 1   | 1.2 | 1.45 | μs   |

| <sup>t</sup> d(unsq) | Unsquelch delay time                              | C <sub>ext</sub> = 15 pF,<br>See Figure 9 | $R_{ext} = 6.8 \text{ k}\Omega,$ |     |     | 180  | ns   |

## PARAMETER MEASUREMENT INFORMATION

NOTE A: The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%,  $t_f \leq$  6 ns,  $t_f \leq$  8 ns,  $t_f \leq$  9 ns,  $t_$

Figure 1. Test Circuit and Voltage Waveforms for Driver Slew Rate

- NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%,  $t_{\Gamma} \leq$  6 ns,  $t_{\Gamma} \leq$  7 ns,  $t_{\Gamma} \leq$  8 ns,  $t_{\Gamma} \leq$  8 ns,  $t_{\Gamma} \leq$  9 ns,

- B. CL includes probe and jig capacitance.

- C. When measuring differential-output delay time difference, switches S1 and S2 are closed (Isolation transformer from Pulse Engineering P/N PE-64352).

Figure 2. Test Circuit and Voltage Waveforms for Driver Differential Delay Time

- NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  500 kHz, duty cycle  $\leq$  50%,  $t_f \leq$  6 ns,  $t_f \leq$  7 ns,  $t_f \leq$  8 ns,

- B. C<sub>L</sub> includes probe and jig capacitance.

Figure 3. Test Circuit and Voltage Waveforms for Driver Enable and Disable Time

NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  200 kHz, duty cycle  $\leq$  50%,  $t_{\Gamma} \leq$  6 ns,  $t_{\Gamma} \leq$  7 ns,  $t_{\Gamma} \leq$  8 n

B. C<sub>L</sub> includes probe and jig capacitance.

Figure 4. Test Circuit and Voltage Waveforms for Driver Enable and Disable Time

NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%,  $t_f \leq$  6 ns,  $t_f \leq$  8 ns,  $t_f \leq$  8 ns,  $t_f \leq$  9 ns,

B. C<sub>I</sub> includes probe and jig capacitance.

Figure 5. Test Circuit and Voltage Waveforms for Enable Time From Delay Enable

NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  200 kHz, duty cycle  $\leq$  50%,  $t_{f} \leq$  6 ns,  $Z_{O} = 50 \ \Omega$ .

B. C<sub>L</sub> includes probe and jig capacitance.

Figure 6. Test Circuit and Voltage Waveforms for Enable Pulse Duration With Delay Enable Low

NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  500 kHz, duty cycle  $\leq$  50%,  $t_{f} \leq$  6 ns,  $Z_{O} =$  50  $\Omega$ .

B. C<sub>I</sub> includes probe and jig capacitance.

Figure 7. Test Circuit and Voltage Waveforms for Receiver Enable (Unsquelch) Time

NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%,  $t_{\Gamma} \leq$  6 ns,  $t_{\Gamma} \leq$  7 ns,  $t_{\Gamma} \leq$  8 ns,  $t_{\Gamma} \leq$  8 ns,  $t_{\Gamma} \leq$  9 ns,

B. C<sub>L</sub> includes probe and jig capacitance.

Figure 8. Test Circuit and Voltage Waveforms for Receiver Propagation Delay Time

Figure 9. Test Circuit and Voltage Waveforms for Unsquelch Duration Time

NOTE A: The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  100 kHz, duty cycle  $\leq$  50%,  $t_f \leq$  6 ns,  $t_f \leq$  8 ns,  $t_f \leq$  9 ns,

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current and complete.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated