### SRAM Memory Card 128 kB through512 kB

### **General Description**

The WEDC **SEA** SRAM Series memory cards offer a high performance nonvolatile storage solution for code and data storage, disk caching, and write intensive mobile and embedded applications.

Packaged in PCMCIA type I housing the WEDC SRAM SEA series is based on 1 or 4Mbit SRAM memories, providing densities from 128 Kbytes to 512 Kbytes.

The SEA series of SRAM memory cards requires a 5V power supply and operates at speeds to 150ns. The cards are based on advanced CMOS technology providing very low power and reliable data retention characteristics. WEDC's SRAM cards contain a rechargeable lithium battery and recharge circuitry, eliminating the need for replaceable batteries found in many SRAM cards.

WEDC's standard cards are shipped with WEDC's SRAM Logo. Cards are also available with blank housings (no Logo). The blank housings are available in both a recessed (for label) and flat housing. Please contact WEDC sales representative for further information on Custom artwork.

#### **Features**

- High Performance SRAM Memory Card

- Single 5 Volt Supply

- Fast Access Times: 150ns

- x8 Interface (subset of PCMCIA standard)

- Low Power CMOS technology provides very low power and reliable data retention characteristics

operating current 80mA maximum

standby current < 100µA typical</li>

- Rechargeable Lithium battery with recharge circuitry - eliminates the need for replaceable batteries - standby current during recharge typically < 2mA

- battery backup time

- 18 months typical typical based on 512kB (lower densities will have greater storage times)

- Unlimited write cycles, no endurance issues

- 2KB EEPROM attribute memory containing CIS (optional)

- Optional Hardware Write Protect Switch

- PC Card Standard Type I Form Factor

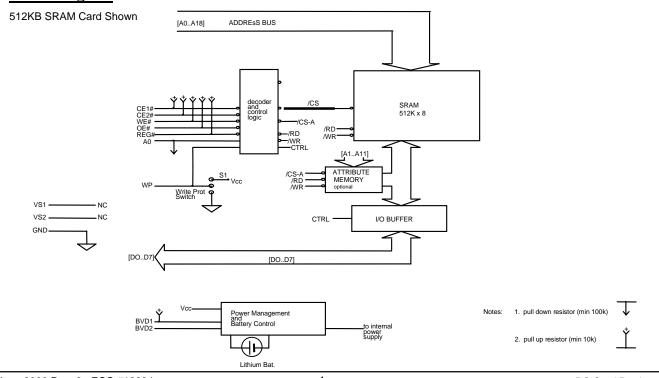

### **Block Diagram**

# **PCMCIA Flash Memory Card**

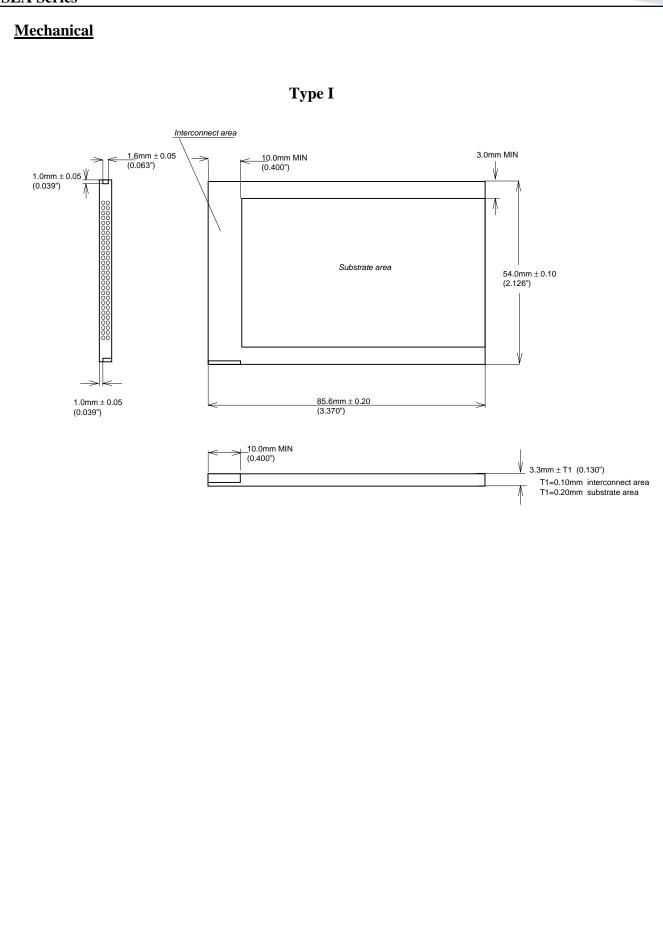

### **SEA Series**

### **Pinout**

| Pin | Signal name | I/O | Function       | Active   | Pin | Signal name | I/O | Function            |

|-----|-------------|-----|----------------|----------|-----|-------------|-----|---------------------|

| 1   | GND         |     | Ground         |          | 35  | GND         |     | Ground              |

| 2   | DQ3         | I/O | Data bit 3     |          | 36  | CD1#        | 0   | Card Detect 1       |

| 3   | DQ4         | I/O | Data bit 4     |          | 37  | NC          | I/O | Data bit 11         |

| 4   | DQ5         | I/O | Data bit 5     |          | 38  | NC          | I/O | Data bit 12         |

| 5   | DQ6         | I/O | Data bit 6     |          | 39  | NC          | I/O | Data bit 13         |

| 6   | DQ7         | I/O | Data bit 7     |          | 40  | NC          | I/O | Data bit 14         |

| 7   | CE1#        | Ι   | Card enable 1  | LOW      | 41  | NC          | Ι   | Data bit 15         |

| 8   | A10         | Ι   | Address bit 10 |          | 42  | NC          | Ι   | Card Enable 2       |

| 9   | OE#         | Ι   | Output enable  | LOW      | 43  | VS1         | 0   | Voltage Sense 1     |

| 10  | A11         | Ι   | Address bit 11 |          | 44  | N.C.        |     |                     |

| 11  | A9          | Ι   | Address bit 9  |          | 45  | N.C.        |     |                     |

| 12  | A8          | Ι   | Address bit 8  |          | 46  | A17         | Ι   | Address bit 17      |

| 13  | A13         | Ι   | Address bit 13 |          | 47  | A18         | Ι   | Address bit 18      |

| 14  | A14         | Ι   | Address bit 14 |          | 48  | N.C.        | Ι   | Address bit 19      |

| 15  | WE#         | Ι   | Write Enable   | LOW      | 49  | N.C.        | Ι   | Address bit 20      |

| 16  | N.C.        |     |                |          | 50  | N.C.        | Ι   | Address bit 21      |

| 17  | Vcc         |     | Supply Voltage |          | 51  | Vcc         |     | Supply Voltage      |

| 18  | N.C.        |     |                |          | 52  | N.C.        |     |                     |

| 19  | A16         | Ι   | Address bit 16 | 128KB(2) | 53  | N.C.        |     | Address bit 22      |

| 20  | A15         | Ι   | Address bit 15 |          | 54  | N.C.        |     | Address bit 23      |

| 21  | A12         | Ι   | Address bit 12 |          | 55  | N.C.        |     | Address bit 24      |

| 22  | A7          | Ι   | Address bit 7  |          | 56  | N.C.        |     | Address bit 25      |

| 23  | A6          | Ι   | Address bit 6  |          | 57  | VS2         | 0   | Voltage Sense 2     |

| 24  | A5          | Ι   | Address bit 5  |          | 58  | N.C.        |     |                     |

| 25  | A4          | Ι   | Address bit 4  |          | 59  | N.C.        | 0   | Extended Bus Cycle  |

| 26  | A3          | Ι   | Address bit 3  |          | 60  | N.C.        |     |                     |

| 27  | A2          | Ι   | Address bit 2  |          | 61  | REG#        | Ι   | Attrib Mem Select   |

| 28  | A1          | Ι   | Address bit 1  |          | 62  | BVD2        | 0   | Bat. Volt. Detect 2 |

| 29  | A0          | Ι   | Address bit 0  |          | 63  | BVD1        | 0   | Bat. Volt. Detect 1 |

| 30  | DQ0         | I/O | Data bit 0     |          | 64  | NC          | I/O | Data bit 8          |

| 31  | DQ1         | I/O | Data bit 1     |          | 65  | NC          | I/O | Data bit 9          |

| 32  | DQ2         | I/O | Data bit 2     |          | 66  | NC          | 0   | Data bit 10         |

| 33  | WP          | 0   | Write Potect   | HIGH     | 67  | CD2#        | 0   | Card Detect 2       |

| 34  | GND         |     | Ground         |          | 68  | GND         |     | Ground              |

#### Notes:

1. CD1# and CD2# are grounded internal to PC Card.

2. Shows density for which specified address bit is MSB.

Higher order address bits are no connects (ie 512KB A18 is MSB, A19 - A21 are NC). 3. BVD1 is an open drain output with a 10K ohm internal pull-up resistor. Active

LOW

LOW N.C.

512KB(2)

N.C.

Low

Low

(3)

LOW

# **PCMCIA Flash Memory Card**

## **SEA Series**

## **Card Signal Description**

| Symbol         | Туре      | Name and Function                                                      |

|----------------|-----------|------------------------------------------------------------------------|

| A0 - A25       | INPUT     | ADDRESS INPUTS: A0 through A25 enable direct addressing of up          |

|                |           | to 64MB of memory on the card. Signal A0 is not used in word access    |

|                |           | mode. A25 is the most significant bit. (address pins used are based on |

|                |           | card density, see pinout for highest used address pin)                 |

| DQ0 - DQ7      | INPUT/OUT | <b>DATA INPUT/OUTPUT:</b> DQ0 THROUGH DQ15 constitute the              |

| DQ8 – DQ15     | PUT       | bi-directional databus. DQ0 - DQ7 constitute the lower (even) byte and |

|                |           | DQ8 - DQ15 the upper (odd) byte. Upper byte is Not Connected on        |

|                |           | this card.                                                             |

| C E1 #, C E2 # | INPUT     | CARD ENABLE 1 AND 2: CE1 # enables even byte accesses,                 |

|                |           | CE2 # control signal in PCMCIA standard, to access high byte, - not    |

|                |           | used on this card                                                      |

| OE#            | INPUT     | <b>OUTPUT ENABLE:</b> Active low signal enabling read data from the    |

|                |           | memory card.                                                           |

| WE#            | INPUT     | <b>WRITE ENABLE:</b> Active low signal gating write data to the memory |

|                |           | card.                                                                  |

| RDY/BSY #      | OUTPUT    | <b>READY/BUSY OUTPUT:</b> Not used for SRAM cards                      |

| CD1 #, CD2 #   | OUTPUT    | CARD DETECT 1 and 2: Provide card insertion detection. These           |

|                |           | signals are connected to ground internally on the memory card. The     |

|                |           | host socket interface circuitry shall supply 10K-ohm or larger pull-up |

|                |           | resistors on these signal pins.                                        |

| WP             | OUTPUT    | WRITE PROTECT: Follows hardware Write Protect Switch. When             |

|                |           | Switch is placed in on position, signal is pulled high (10K ohm). When |

|                |           | switch is off signal is pulled low.                                    |

| VPP1, VPP2     | N.C.      | <b>PROGRAM/ERASE POWER SUPPLY:</b> Not used for SRAM                   |

|                |           | cards.                                                                 |

| VCC            |           | <b>CARD POWER SUPPLY:</b> 5.0V for all internal circuitry.             |

| GND            |           | <b>GROUND:</b> for all internal circuitry.                             |

| REG #          | INPUT     | ATTRIBUTE MEMORY SELECT : only used with cards built with              |

|                |           | optional attribute memory.                                             |

| RST            | INPUT     | <b>RESET:</b> Not used for SRAM cards                                  |

| WAIT #         | OUTPUT    | WAIT: This signal is pulled high internally for compatibility. No wait |

|                |           | states are generated.                                                  |

| BVD1, BVD2     | OUTPUT    | <b>BATTERY VOLTAGE DETECT:</b> Provides status of Battery              |

|                |           | voltage.                                                               |

|                |           | BVD2 = BVD1 = Voh (battery voltage is guaranteed to retain data)       |

|                |           | BVD2 = Vol, BVD1 = Voh (data is valid, battery recharge required)      |

|                |           | BVD2 = BVD1 = Vol (data may no longer be valid, battery requires       |

|                |           | extended recharge)                                                     |

| VS1, VS2       | OUTPUT    | <b>VOLTAGE SENSE:</b> Notifies the host socket of the card's VCC       |

|                |           | requirements. VS1 and VS2 are open to indicate a 5V, 16 bit card has   |

|                |           | been inserted.                                                         |

| RFU            |           | RESERVED FOR FUTURE USE                                                |

| N.C.           |           | NO INTERNAL CONNECTION TO CARD: pin may be driven                      |

|                |           | or left floating                                                       |

#### FUNCTIONAL TRUTH TABLE

| READ function        |      |      |     |     |      | Commor | n Memory | Α    | ttribute M | emory    |

|----------------------|------|------|-----|-----|------|--------|----------|------|------------|----------|

| Function Mode        | /CE2 | /CE1 | /OE | /WE | /REG | D15-D8 | D7-D0    | /REG | D15-D8     | D7-D0    |

| Standby Mode         | Х    | Н    | Х   | Х   | Х    | High-Z | High-Z   | Х    | High-Z     | High-Z   |

| Byte Access (8 bits) | Х    | L    | L   | Н   | Н    | High-Z | Data Out | L    | High-Z     | Data Out |

| WRITE function       |      |      |     |     |      |        |          |      |            |          |

| Standby Mode         | Х    | Н    | Х   | Х   | Х    | Х      | Х        | Х    | Х          | Х        |

| Byte Access (8 bits) | Х    | L    | Н   | L   | Н    | Х      | Data In  | L    | Х          | Data In  |

## Absolute Maximum Ratings (2)

|                       | ) ('<br>u                                                                    |

|-----------------------|------------------------------------------------------------------------------|

| 0°C to +60 °C         | +                                                                            |

| -40°C to +85 °C       | 1                                                                            |

|                       | (2                                                                           |

| 0°C to +60 °C         | p p                                                                          |

| -40°C to +85 °C       | s                                                                            |

| -0.5V to VCC+0.5V (1) | th                                                                           |

| -0.5V to +7.0V        | th                                                                           |

|                       | -40°C to +85 °C<br>0°C to +60 °C<br>-40°C to +85 °C<br>-0.5V to VCC+0.5V (1) |

#### Notes:

During transitions, inputs may undershoot to -2.0V or overshoot to VCC +2.0V for periods less than 20ns.

(2) Stress greater than those listed under "Absolute Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **DC Characteristics** <sup>(1)</sup>

CMOS Test Conditions: VIL = VSS ± 0.2V, VIH = VCC ± 0.2V

| Sym  | Parameter              | Density | Notes | Min   | Typ <sup>(3)</sup> | Max  | Units | Test Conditions       |

|------|------------------------|---------|-------|-------|--------------------|------|-------|-----------------------|

| ICC  | VCC Active Current     | 128KB   | 1     |       | 40                 | 80   | mA    | VCC = 5.25V           |

|      |                        | 512KB   |       |       | 40                 | 80   |       | tcycle = 150ns        |

| ICCS | VCC Standby Current    | All     | 2,4   | < 0.1 | < 1                | 10   | mA    | VCC = 5.25V           |

|      |                        |         |       |       |                    |      |       | Control Signals = VCC |

| ILI  | Input Leakage Current  | All     | 5,6   |       |                    | ±20  | μA    | VCC = VCCMAX          |

|      |                        |         |       |       |                    |      |       | Vin =VCC or VSS       |

| ILO  | Output Leakage Current | All     | 6     |       |                    | ±20  | μA    | VCC = VCCMAX          |

|      |                        |         |       |       |                    |      |       | Vout =VCC or VSS      |

| VIL  | Input Low Voltage      | All     | 6     | 0     |                    | 0.8  | V     |                       |

| VIH  | Input High Voltage     | All     | 6     | 3.85  |                    | VCC  | V     |                       |

|      |                        |         |       |       |                    | +0.5 |       |                       |

| VOL  | Output Low Voltage     | All     | 6     |       |                    | 0.4  | V     | IOL = 3.2mA           |

| VOH  | Output High Voltage    | All     | 6     | VCC-  |                    | VCC  | V     | IOH = -2.0mA          |

|      |                        |         |       | 0.4   |                    |      |       |                       |

#### Notes:

1. All currents are for x8 mode and are RMS values unless otherwise specified.

2. Control Signals: CE1#, CE2#, OE#, WE#, REG#.

3. Typical: VCC = 5V, T = +25C.

4. ICCS includes battery recharge current. Value depends on battery discharge level. ICCS min is specified for fully charged battery. ICCS typical value is specified for battery discharge to 2.7V. ICCS max is specified for a fully discharged battery (0V). Battery will recharge to 1.5V in 20 sec.

5. Values are the same for byte and word wide modes for all card densities.

Exceptions: Leakage currents on CE1#, CE2#, OE#, REG# and WE# will be < 500 μA when VIN = GND due to internal pull-up resistors.

## **Battery Characteristics**

| Parameter              | Density | Notes | Type I | Units     | Conditions                          |

|------------------------|---------|-------|--------|-----------|-------------------------------------|

| Battery Life           | All     | (1)   | 10     | years     | Normal operation, T=25C             |

|                        | 128KB   | (2)   | 24     |           | T=25C                               |

| Dottom                 | 512KB   |       | 18     | months    | Battery backup time is a calculated |

| Battery<br>Backup Time |         |       |        |           | value and is not guaranteed. This   |

| Баскир тіше            |         |       |        | (typical) | should not be used to schedule      |

|                        |         |       |        |           | battery recharging.                 |

#### Notes:

1. Battery Life refers to functional lifetime of battery.

2. Battery backup time is density and temperature dependent.

## **AC Characteristics**

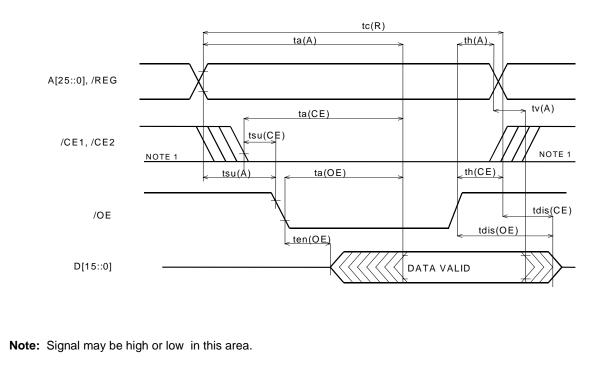

**Read Timing Parameters**

|                       |                                 | 150ns |     |      |

|-----------------------|---------------------------------|-------|-----|------|

| SYM<br>(PCMCIA)       | Parameter                       | Min   | Max | Unit |

| t <sub>RC</sub>       | Read Cycle Time                 | 150   |     | ns   |

| t <sub>a</sub> (A)    | Address Access Time             |       | 150 | ns   |

| t <sub>a</sub> (CE)   | Card Enable Access Time         |       | 150 | ns   |

| t <sub>a</sub> (OE)   | Output Enable Access Time       |       | 75  | ns   |

| t <sub>su</sub> (A)   | Address Setup Time              | 20    |     | ns   |

| t <sub>su</sub> (CE)  | Card Enable Setup Time          | 0     |     | ns   |

| t <sub>h</sub> (A)    | Address Hold Time               | 20    |     | ns   |

| t <sub>h</sub> (CE)   | Card Enable Hold Time           | 20    |     | ns   |

| t <sub>v</sub> (A)    | Output Hold from Address Change | 0     |     | ns   |

| t <sub>dis</sub> (CE) | Output Disable Time from CE#    |       | 75  | ns   |

| t <sub>dis</sub> (OE) | Output Disable Time from OE#    |       | 75  | ns   |

| t <sub>dis</sub> (CE) | Output Enable Time from CE#     | 5     |     | ns   |

| t <sub>dis</sub> (CE) | Output Enable Time from OE#     | 5     |     | ns   |

**Note:** AC timing diagrams and characteristics are guaranteed to meet or exceed PCMCIA 2.1 specifications.

#### Read Timing Diagram

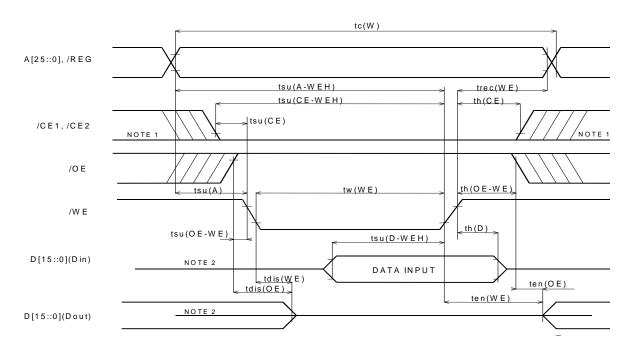

#### Write Timing Parameters

|                          |                                 | 150ns |     |      |

|--------------------------|---------------------------------|-------|-----|------|

| SYM<br>(PCMCIA)          | Parameter                       | Min   | Max | Unit |

| t <sub>c</sub> W         | Write Cycle Time                | 150   |     | ns   |

| t <sub>w</sub> (WE)      | Write Pulse Width               | 80    |     | ns   |

| t <sub>su</sub> (A)      | Address Setup Time              | 20    |     | ns   |

| t <sub>su</sub> (A-WEH)  | Address Setup Time for WE#      | 100   |     | ns   |

| t <sub>su</sub> (CE-WEH) | Card Enable Setup Time for WE#  | 100   |     | ns   |

| t <sub>su</sub> (D-WEH)  | Data Setup Time for WE#         | 50    |     | ns   |

| t <sub>h</sub> (D)       | Data Hold Time                  | 20    |     | ns   |

| t <sub>rec</sub> (WE)    | Write Recover Time              | 20    |     | ns   |

| t <sub>dis</sub> (WE)    | Output Disable Time from WE#    |       | 75  | ns   |

| t <sub>dis</sub> (OE)    | Output Disable Time from OE#    |       | 75  | ns   |

| t <sub>en</sub> (WE)     | Output Enable Time from WE#     | 5     |     | ns   |

| t <sub>dis</sub> (OE)    | Output Enable Time from OE#     | 5     |     | ns   |

| t <sub>su</sub> (OE-WE)  | Output Enable Setup from WE#    | 10    |     | ns   |

| t <sub>h</sub> (OE-WE)   | Output Enable Hold from WE#     | 10    |     | ns   |

| t <sub>su</sub> (CE)     | Card Enable Setup Time from OE# | 0     |     | ns   |

| t <sub>h</sub> (CE)      | Card Enable Hold Time           | 20    |     | ns   |

Note: AC timing diagrams and characteristics are guaranteed to meet or exceed PCMCIA 2.1 specifications.

#### Write Timing Diagram

#### Notes:

1. Signal may be high or low in this area.

2. When the data I/O pins are in the output state, no signals shall be applied to the data pins (D15 - D0) by the host system.

## **PCMCIA Flash Memory Card**

**SEA Series**

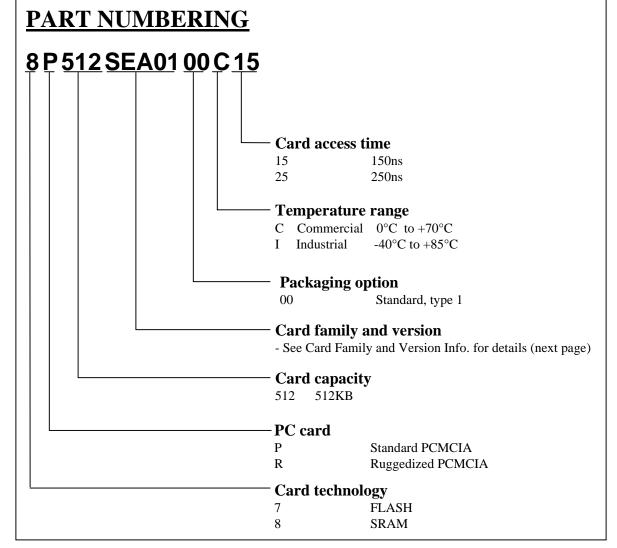

## **Ordering Information**

# 8P XXX SEA YY SS T ZZ

#### where

| XXX: | 128 | 128KB                                            |

|------|-----|--------------------------------------------------|

|      | 512 | 512KB                                            |

| YY:  | 01  | no attribute memory, no Write Protect Switch     |

|      | 02  | with attribute memory, no Write Protect Switch   |

|      | 03  | with Write Protect Switch, no attribute memory   |

|      | 04  | with attribute memory, with Write Protect Switch |

| SS:  | 00  | WEDC SRAM Logo Type I                            |

|      | 01  | Blank Housing, Type I                            |

|      | 02  | Blank Housing, Type I Recessed                   |

| T:   | С   | Commercial                                       |

|      | Ι   | Industrial                                       |

| ZZ:  | 15  | 150ns                                            |

| REVISION HISTORY |         |                                  |  |  |  |  |

|------------------|---------|----------------------------------|--|--|--|--|

| Date of revision | Version | Description                      |  |  |  |  |

| 1-Jun-98         | -001    | Initial release                  |  |  |  |  |

| 27-May-99        | -002    | Company/Logo change              |  |  |  |  |

| 1-Jun-00         | -003    | Added page 8, Page Header Change |  |  |  |  |

| White Electronic Designs Corporation           |                          |

|------------------------------------------------|--------------------------|

| One Research Drive, Westborough, MA 01581, USA |                          |

| tel: (508) 366 5151                            |                          |

| fax: (508) 836 4850                            |                          |

| www.whiteedc.com                               | WHITE ELECTRONIC DESIGNS |