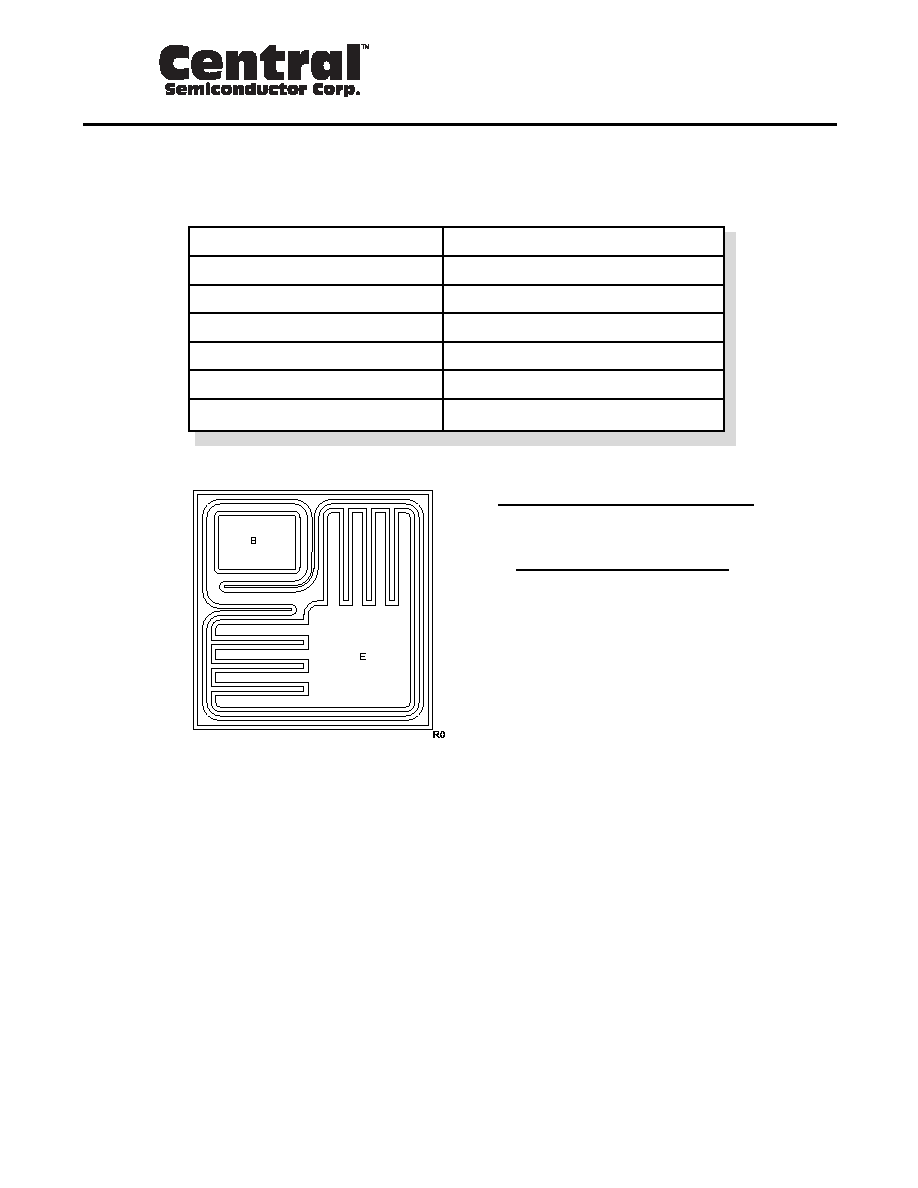

PROCESS

CP230

Power Transistors

NPN - Silicon Darlington Transistor Chip

PRINCIPAL DEVICE TYPES

CZT122

CJD122

Process

EPITAXIAL BASE

Die Size

80 X 80 MILS

Die Thickness

8 MILS

Base Bonding Pad Area

18 X 27 MILS

Emitter Bonding Pad Area

34 X 34 MILS

Top Side Metalization

Al - 30,000≈

Back Side Metalization

Ti/Pd/Ag (20,000≈)

PROCESS DETAILS

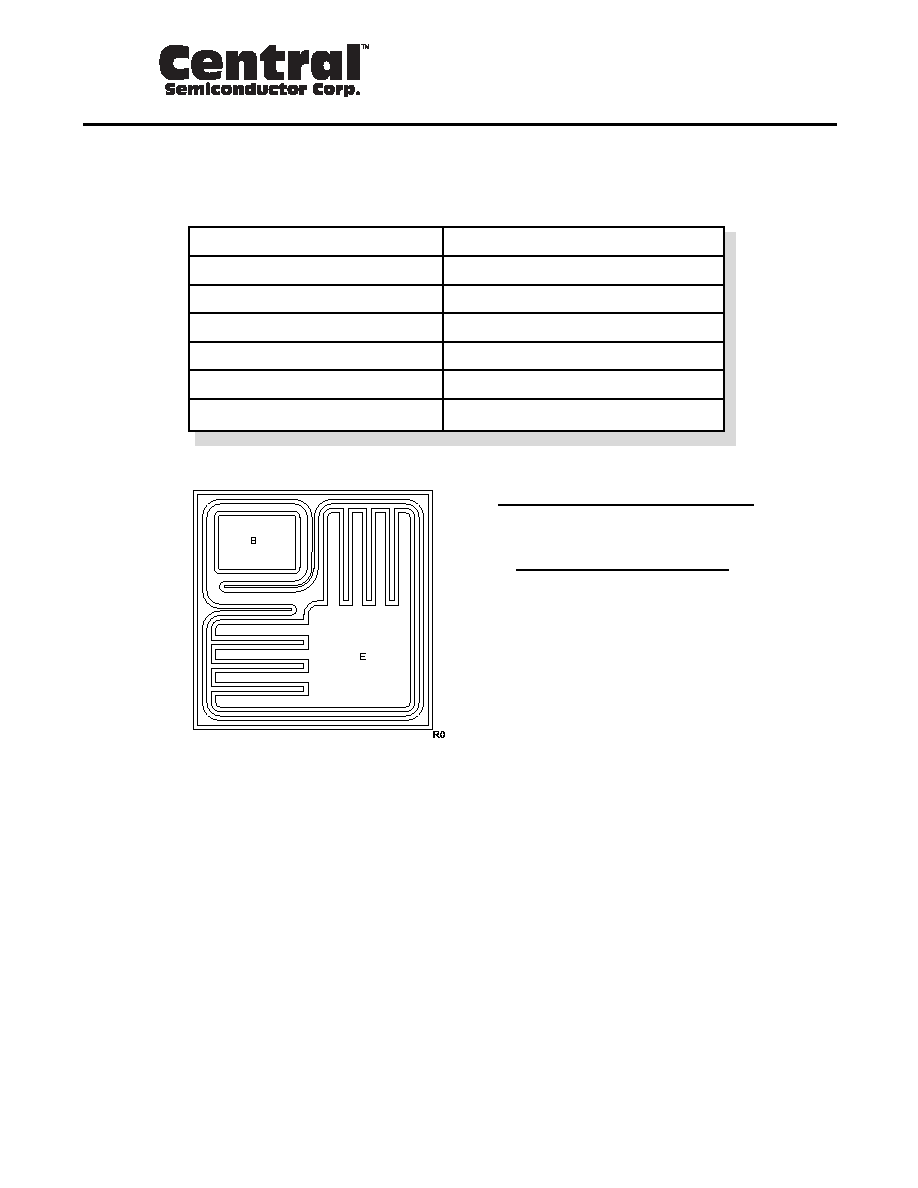

R0 (9 -May 2005)

GEOMETRY

145 Adams Avenue

Hauppauge, NY 11788 USA

Tel:

(631) 435-1110

Fax: (631) 435-1824

www.centralsemi.com

GROSS DIE PER 4 INCH WAFER

1,445

BACKSIDE COLLECTOR