LTC4056-4.2

1

405642i

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-

tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

The LTC

Æ

4056 is a low cost, single-cell, constant-current/

constant-voltage Li-Ion battery charger controller with a

programmable termination timer. When combined with a

few external components, the LTC4056 forms a very small

standalone charger for single cell lithium-ion batteries.

Charge current and charge time are set externally with a

single resistor and capacitor, respectively. The LTC4056

charges to a final float voltage accurate to

±

0.6%. Manual

shutdown is accomplished by grounding the TIMER/

SHDN pin, while removing input power automatically puts

the LTC4056 into a sleep mode. Both the shutdown and

sleep modes drain near zero current from the battery and

the shutdown mode reduces supply current to 40

µ

A.

The output driver is both current limited and thermally

protected to prevent operating outside of safe limits. No

external blocking diode or sense resistor is required. The

LTC4056 also includes low battery charge conditioning

(trickle charging), undervoltage charge current limiting,

automatic recharge and a charge status output.

The LTC4056 is available in a low profile (1mm) 8-lead

ThinSOT package.

s

Cellular Telephones

s

Handheld Computers

s

Digital Cameras

s

Charging Docks and Cradles

s

Low Cost and Small Size Chargers

, LTC and LT are registered trademarks of Linear Technology Corporation.

s

Standalone Li-Ion Charger with Termination

s

Programmable Termination Timer

s

No Sense Resistor or Blocking Diode Required

s

Suitable for USB-Powered Charging

s

Undervoltage Charge Current Limiting

s

Preset Charge Voltage with

±

0.6% Accuracy

s

Programmable Charge Current: 200mA to 700mA

s

Automatic Recharge

s

Self-Protection for Overcurrent/Overtemperature

s

40

µ

A Supply Current in Shutdown Mode

s

Negligible Battery Drain Current in Shutdown

s

Low Battery Charge Conditioning (Trickle Charging)

s

CHRG Status Output including AC Present Sense

s

Low Profile (1mm) ThinSOT

TM

Package

s

PCB Total Solution Area only 75mm

2

(700mA)

APPLICATIO S

U

FEATURES

DESCRIPTIO

U

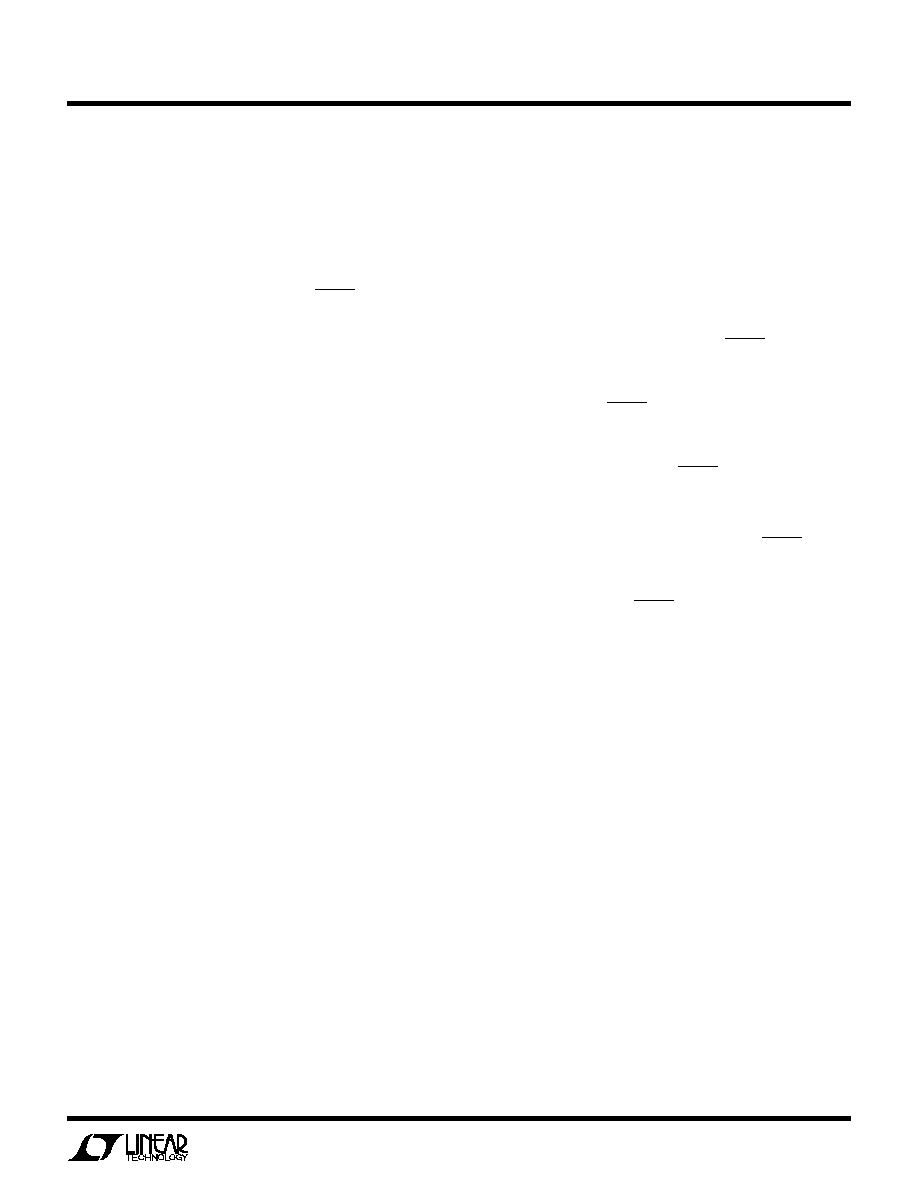

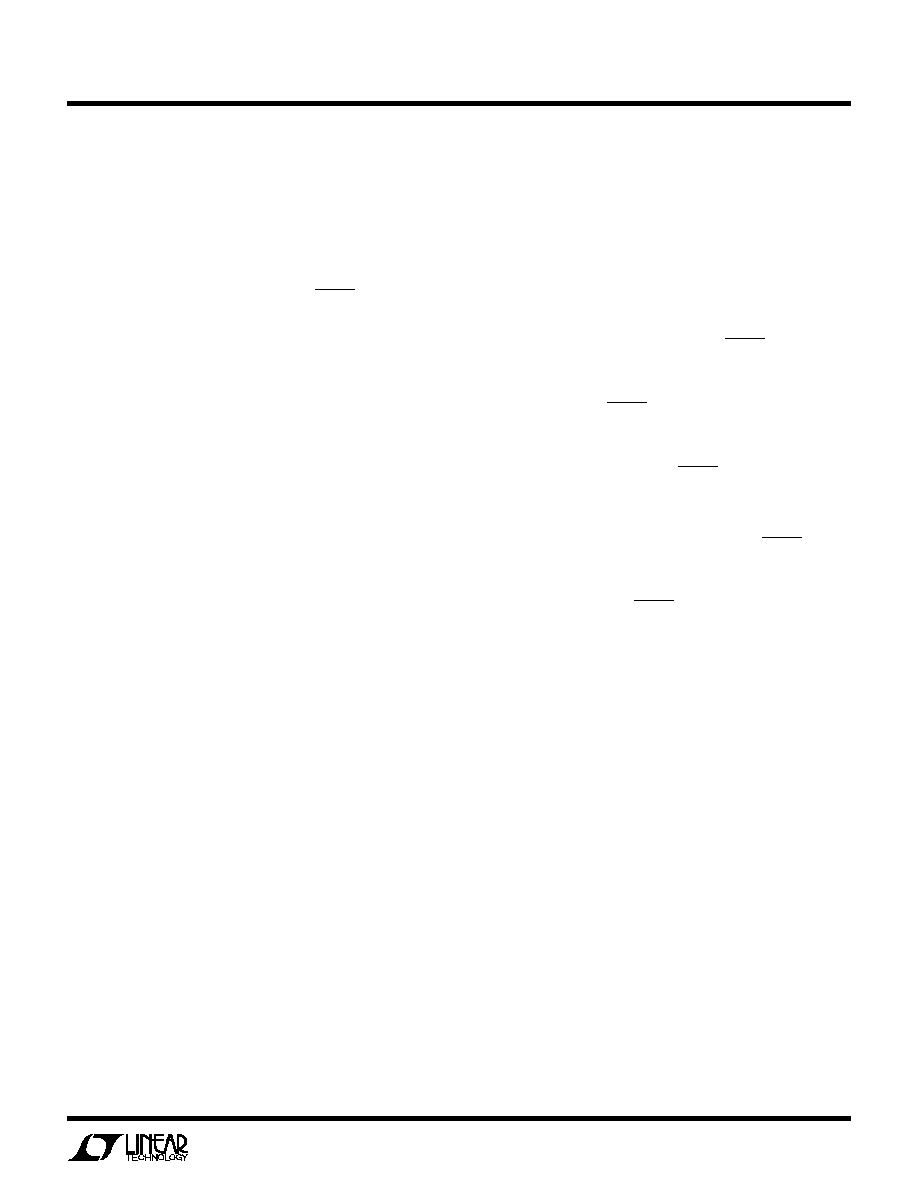

TYPICAL APPLICATIO

U

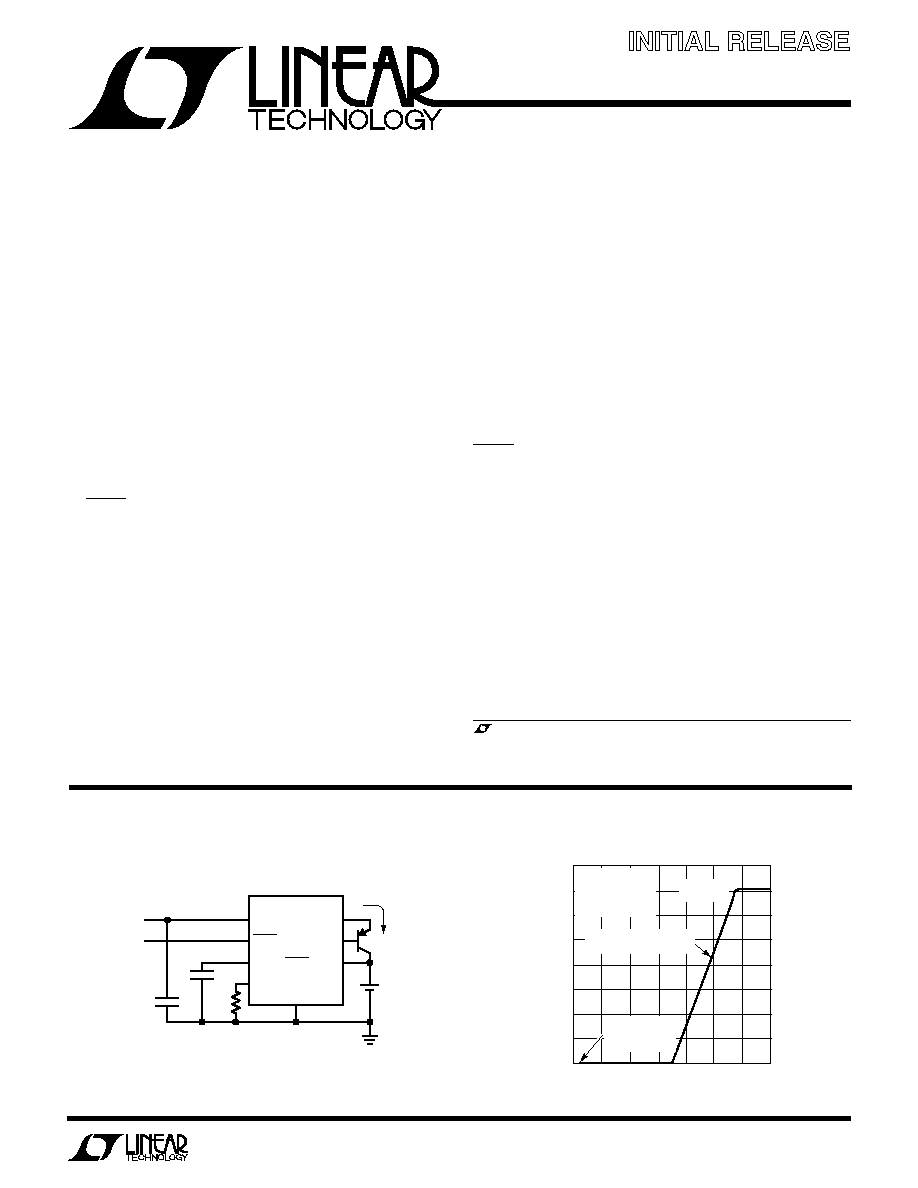

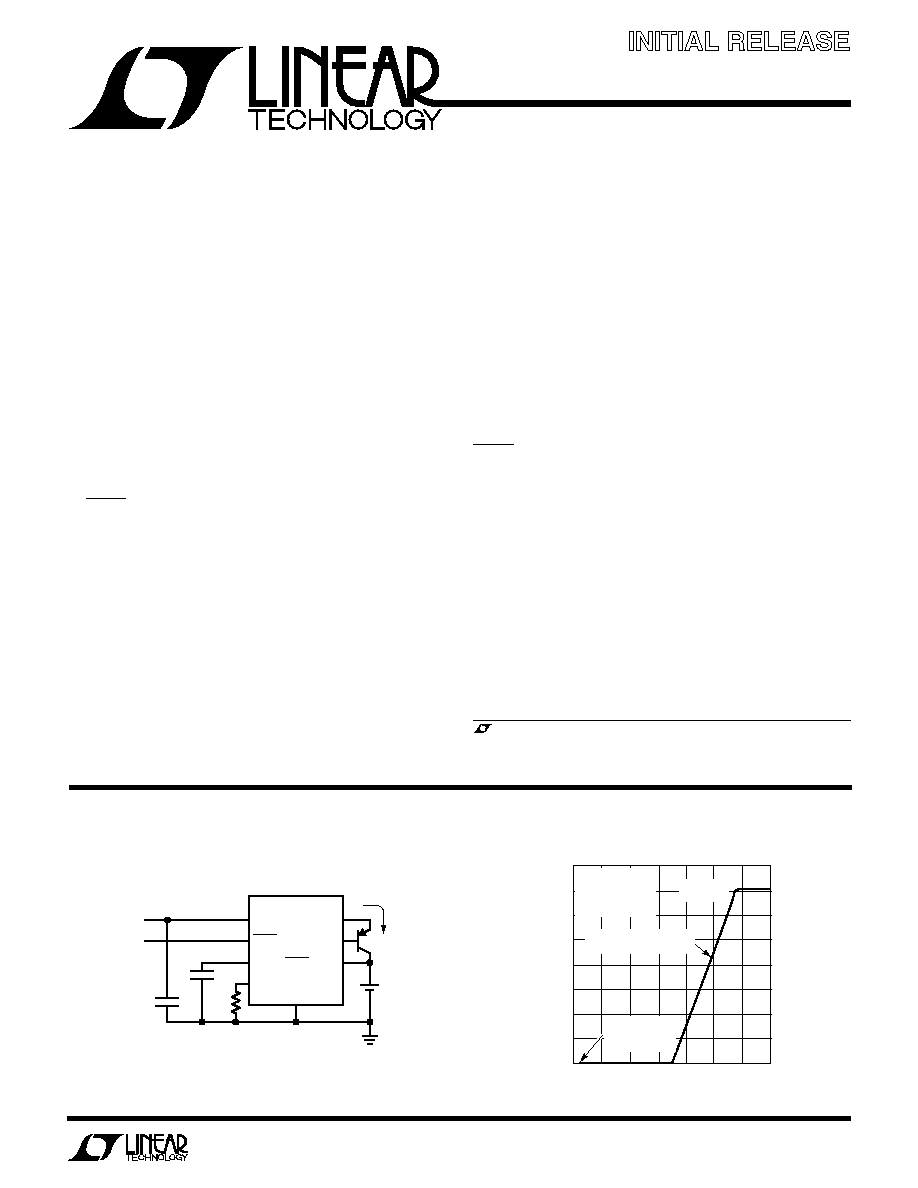

Linear Li-Ion Charger

with Termination in ThinSOT

February 2003

Final Electrical Specifications

V

CC

I

SENSE

CHRG

V

IN

4.5V TO 6.5V

CHARGE

STATUS

DRIVE

TIMER/SHDN

BAT

PROG

GND

4056-4.2 TA01

1-CELL

4.2V Li-Ion

1

µ

F

1

µ

F

700mA

ZXT1M322

1.3k

LTC4056

+

1

8

7

5

2

3

6

ThinSOT is a trademark of Linear Technology Corporation.

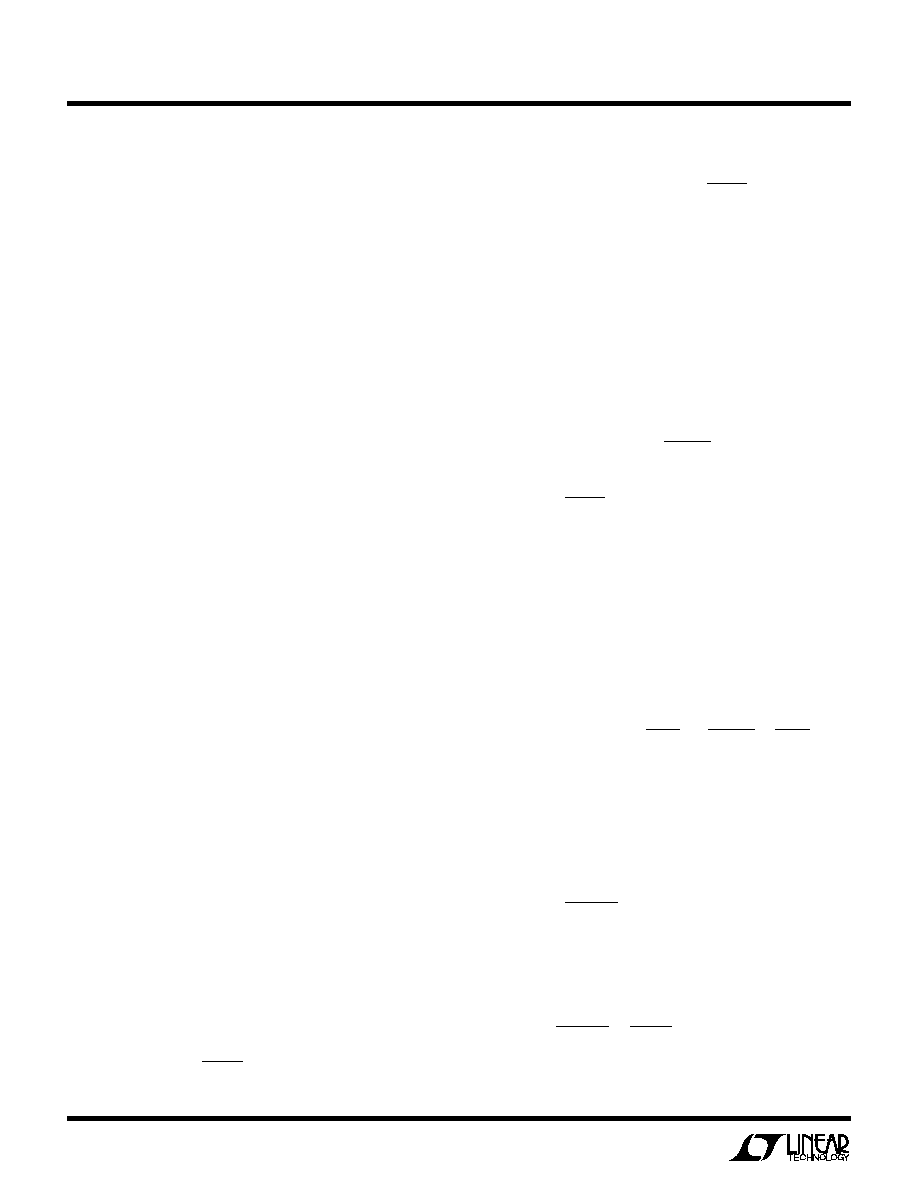

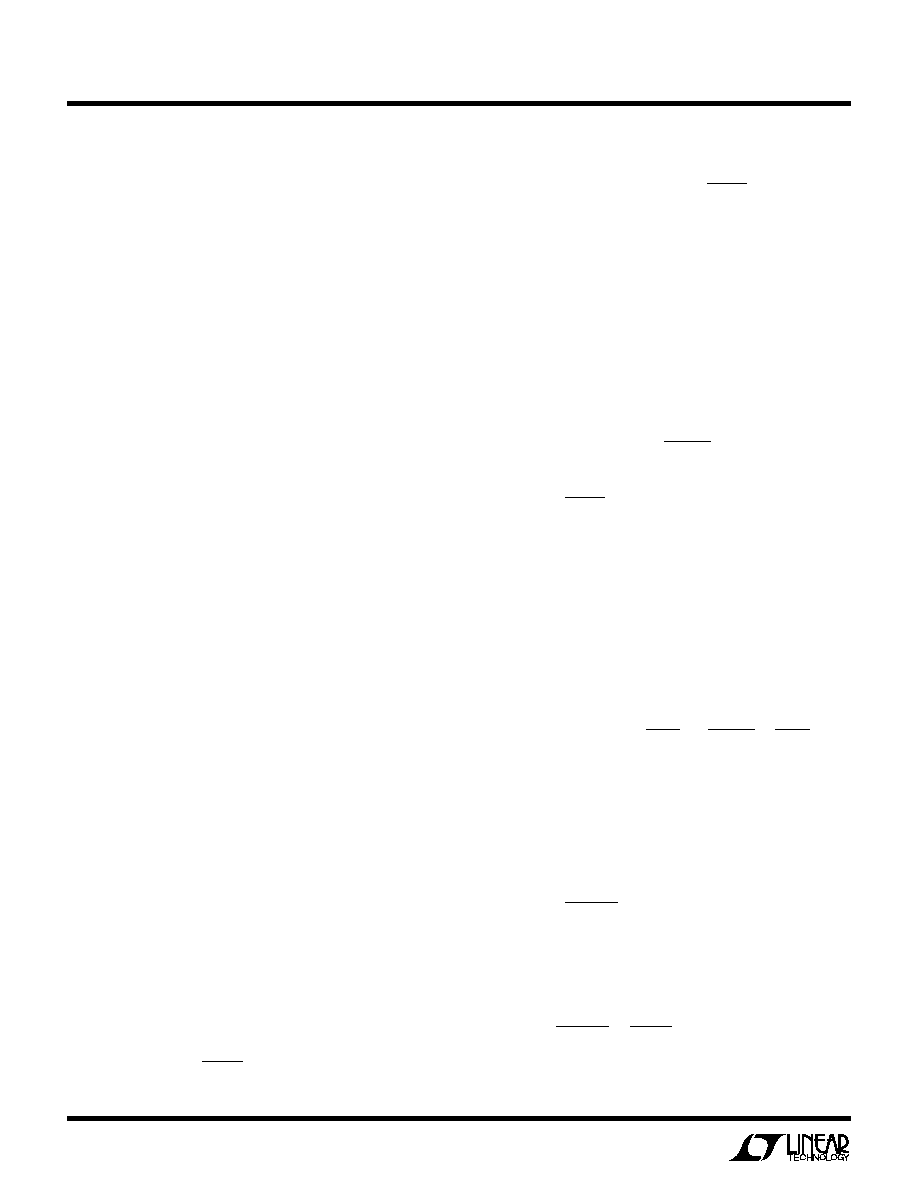

V

IN

(V)

4.40

I BAT

(mA)

4.70

4056 TA02

4.50

4.60

800

700

600

500

400

300

200

100

0

4.45

4.55

4.65

4.75

CONSTANT

CURRENT

UNDERVOLTAGE CHARGE

CURRENT LIMITING

UNDERVOLTAGE

LOCKOUT

AT 4.35V

V

BAT

= 4V

R

PROG

= 1.3k

I

CHRG

= 700mA

INPUT Z = 100m

V

IN

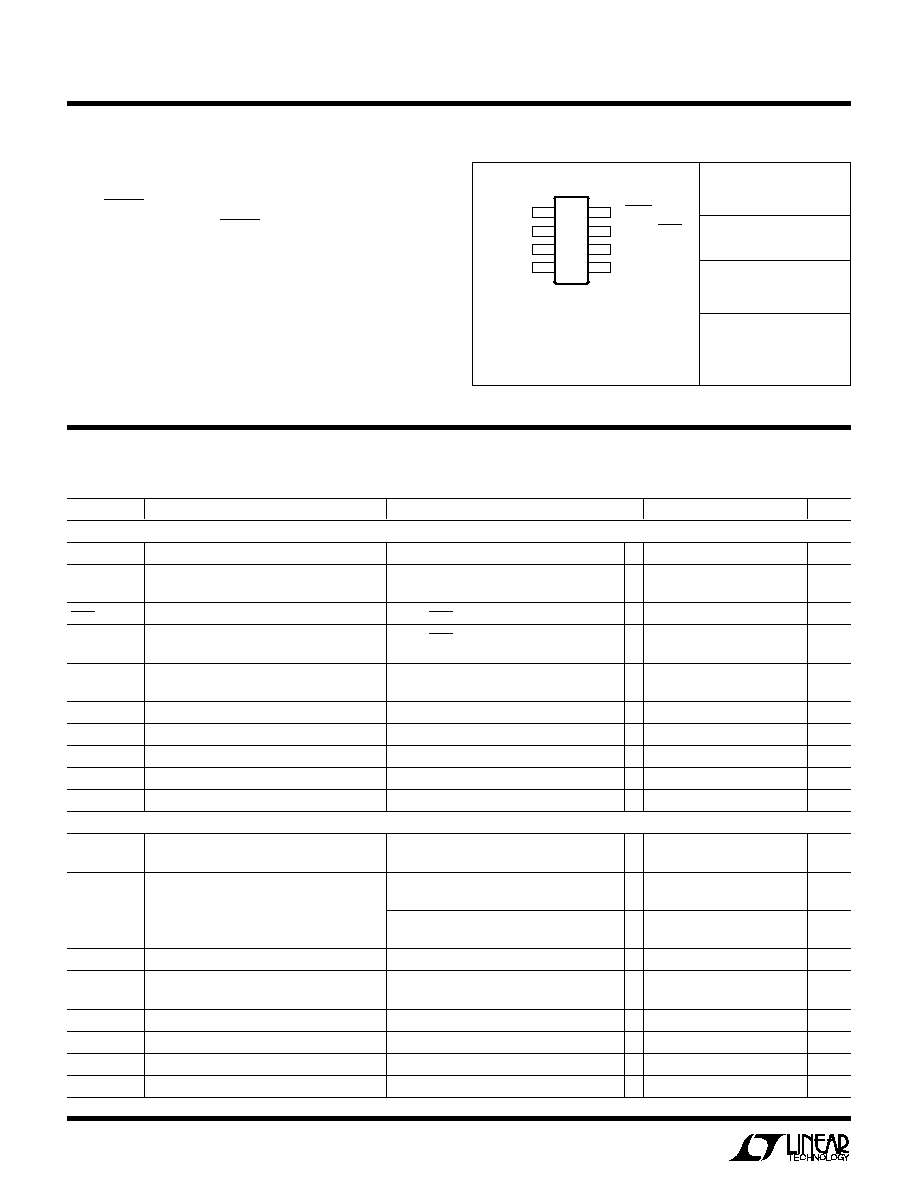

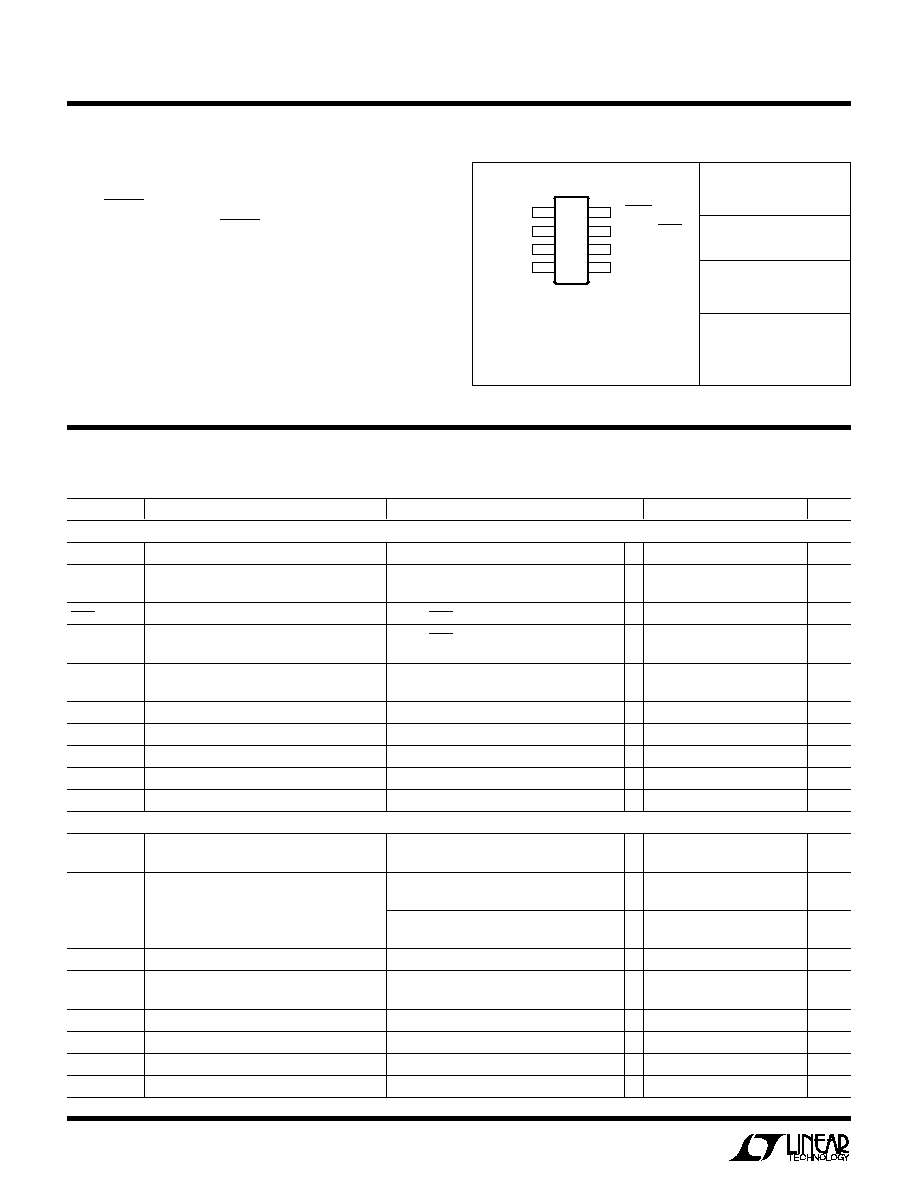

Undervoltage Charge

Current Limiting

LTC4056-4.2

2

405642i

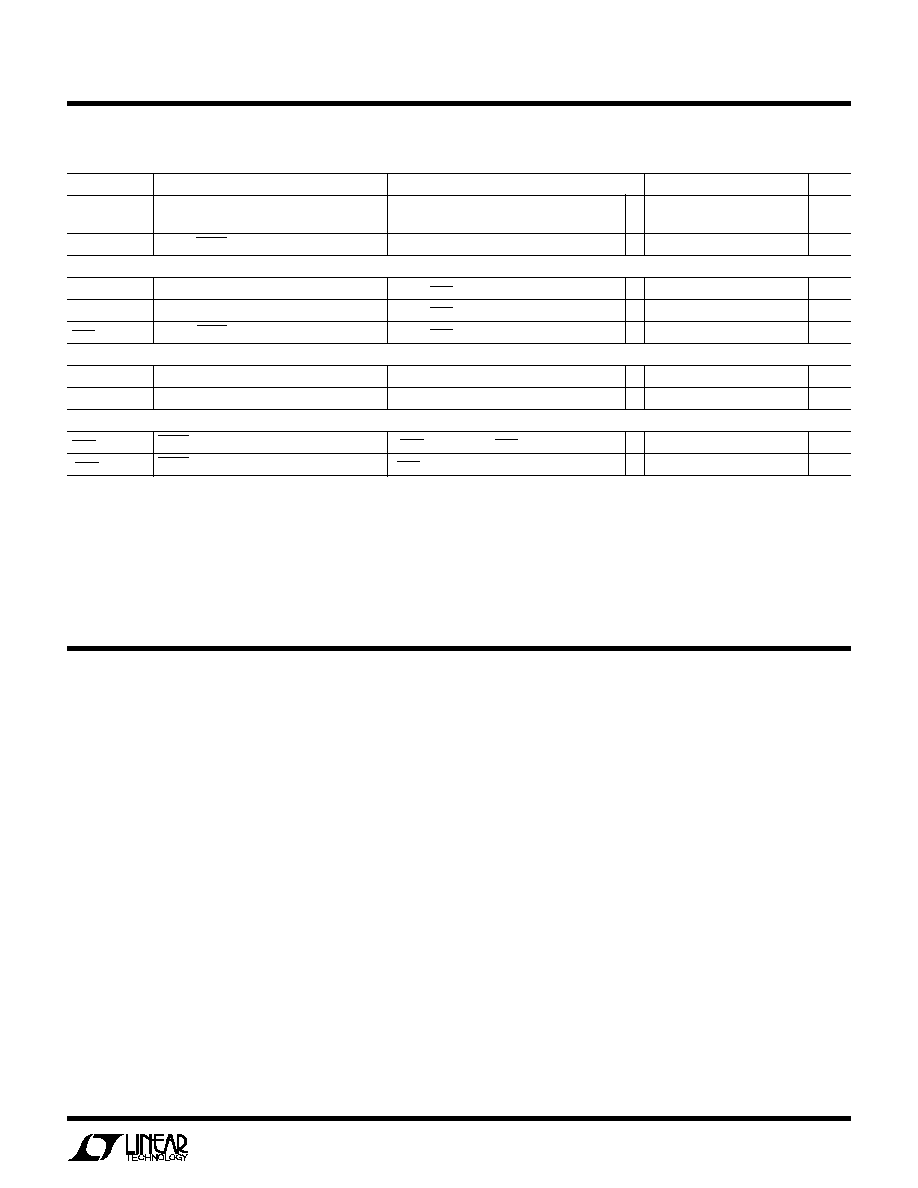

ORDER PART

NUMBER

TS8 PART

MARKING

T

JMAX

= 125

∞

C,

JA

= 120

∞

C/W TO 200

∞

C/W

DEPENDING ON PC BOARD LAYOUT

Consult LTC Marketing for parts specified with wider operating temperature ranges.

LTG5

LTC4056ETS8-4.2

ABSOLUTE AXI U

RATI GS

W

W

W

U

PACKAGE/ORDER I FOR ATIO

U

U

W

(Note 1)

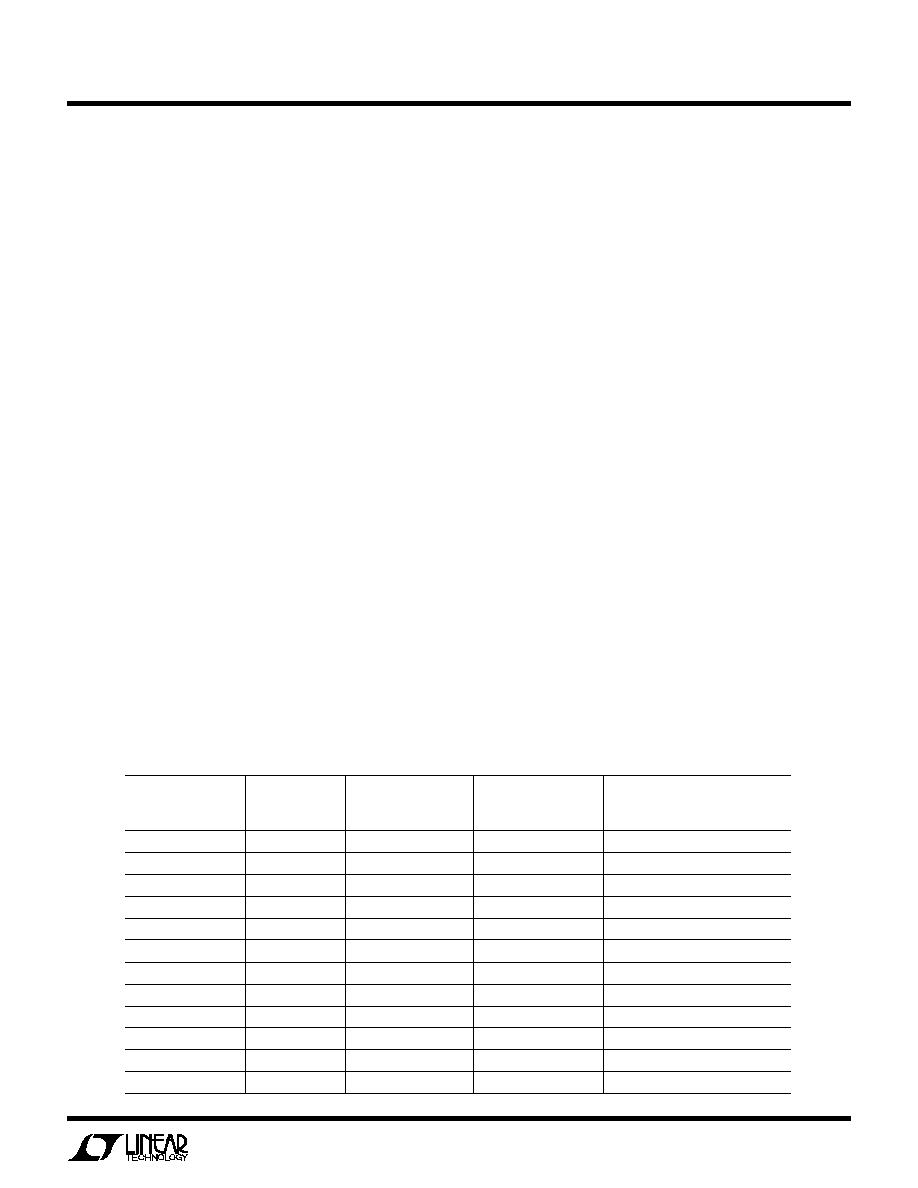

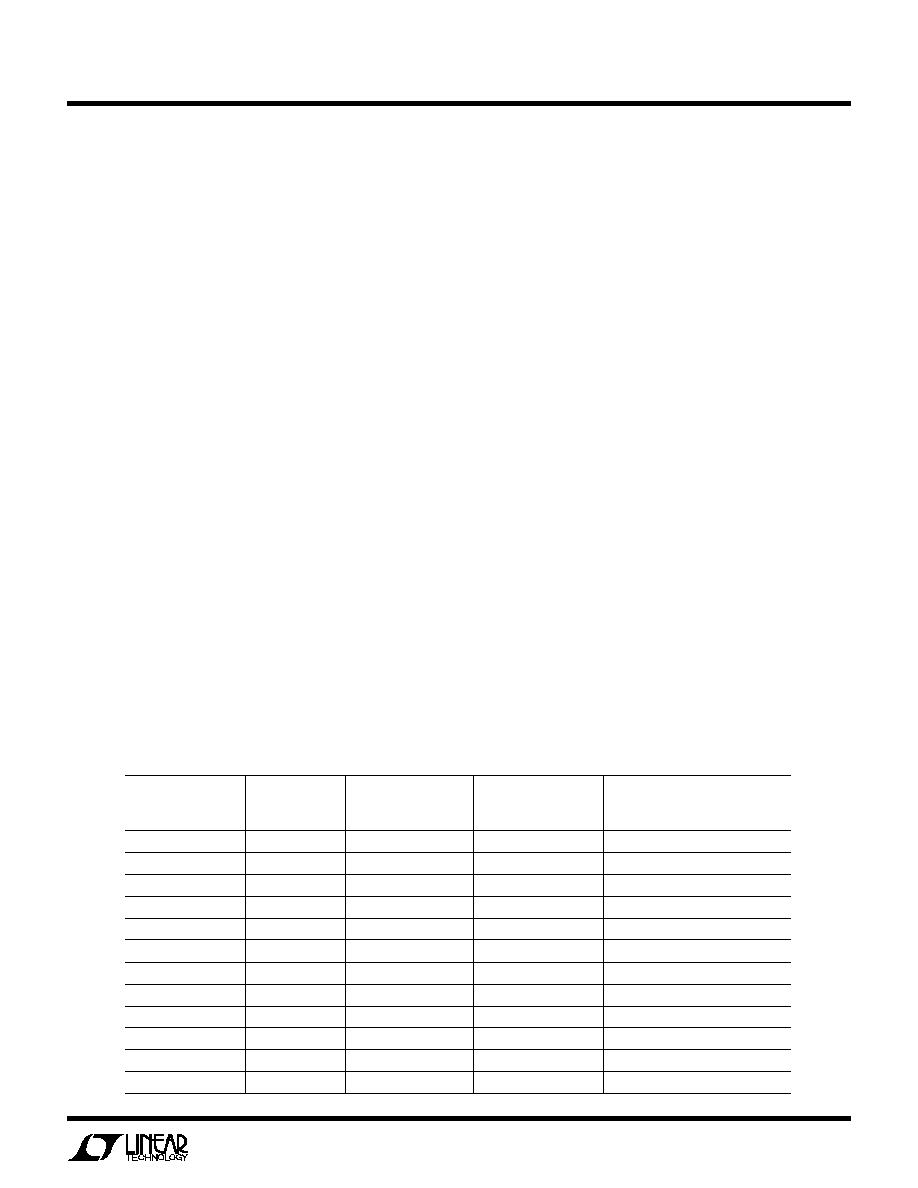

ELECTRICAL CHARACTERISTICS

The

q

denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at T

A

= 25

∞

C. V

CC

= 5V.

Input Supply Voltage (V

CC

) ........................≠ 0.3V to 10V

BAT, CHRG ................................................≠ 0.3V to 10V

DRIVE, PROG, TIMER/SHDN ....... ≠ 0.3V to (V

CC

+ 0.3V)

Output Current (I

SENSE

) ...................................... 900mA

Short-Circuit Duration (BAT, I

SENSE

) ............ Continuous

Junction Temperature ........................................... 125

∞

C

Operating Ambient Temperature Range

(Note 2) .............................................. ≠ 40

∞

C to 85

∞

C

Storage Temperature Range ................. ≠ 65

∞

C to 150

∞

C

Lead Temperature (Soldering, 10 sec).................. 300

∞

C

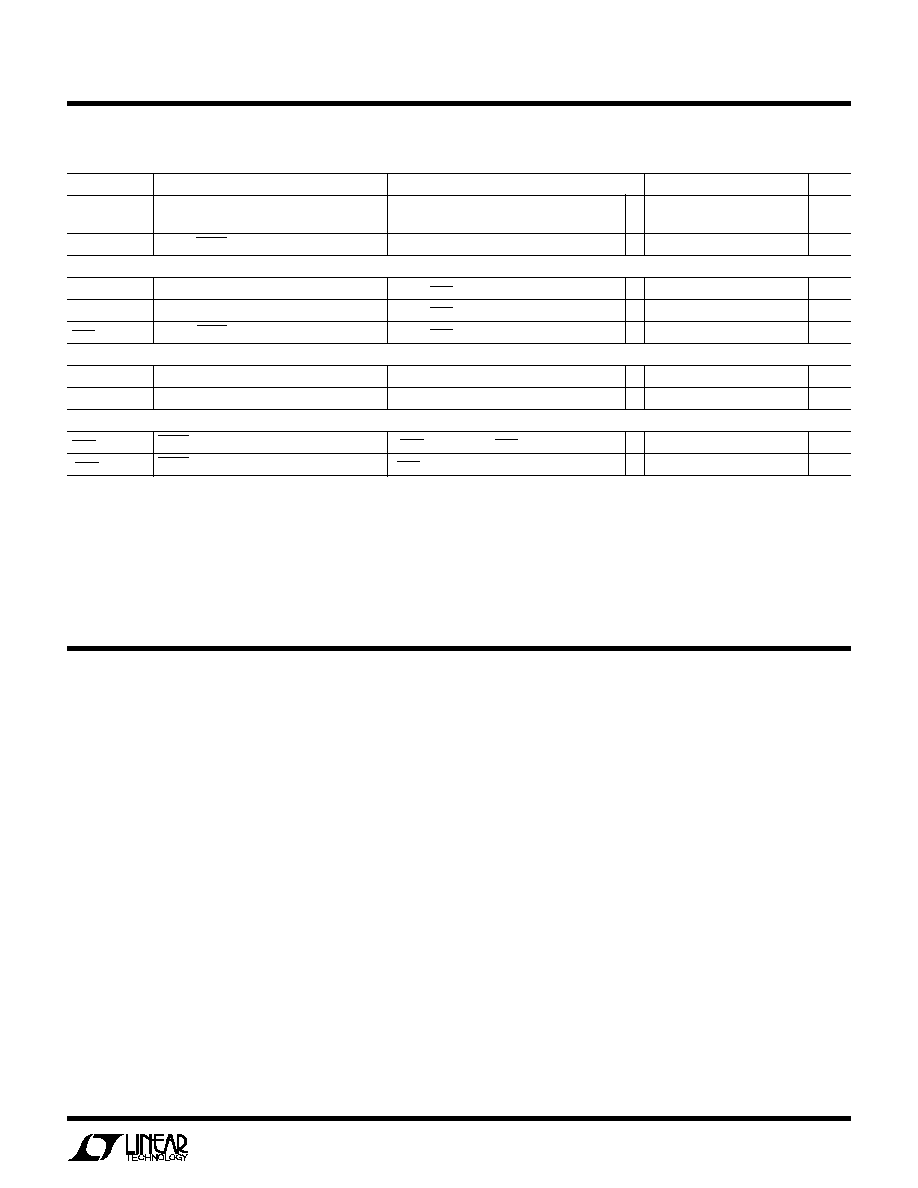

1

2

3

4

V

CC

I

SENSE

DRIVE

GND

8

7

6

5

CHRG

TIMER/SHDN

BAT

PROG

TOP VIEW

TS8 PACKAGE

8-LEAD PLASTIC SOT-23

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

CC

Supply

V

CC

Input Supply Voltage (Note 3)

q

4.5

6.5

V

I

CC

Quiescent V

CC

Supply Current

V

BAT

= 4.5V (Forces I

DRIVE

= 0)

I

PROG

= 200

µ

A (R

PROG

= 5k)

q

400

600

µ

A

I

SHDN

V

CC

Supply Current in Manual Shutdown

V

TIMER/SHDN

= 0V

40

60

µ

A

I

BMS

Battery Drain Current in

V

TIMER/SHDN

= 0V

q

≠1

0

1

µ

A

Manual Shutdown (Note 4)

I

BSL

Battery Drain Current in

V

CC

= 0V

q

≠1

0

1

µ

A

Sleep Mode (Note 5)

V

UVLOI

Undervoltage Rising Threshold

V

CC

Increasing

q

4.325

4.40

4.475

V

V

UVLOD

Undervoltage Falling Threshold

V

CC

Decreasing

q

4.275

4.35

4.425

V

V

UVHYS

Undervoltage Hysteresis

V

UVLOI

-V

UVLOD

50

mV

V

UVCL

Undervoltage Charge Current Limit Threshold

4.575

V

V

UVCL

-V

UVLOI

UV Charge Current to UVLO Threshold Margin

q

90

170

250

mV

Charging Performance

V

FLOAT

Output Float Voltage in

I

BAT

= 10mA

4.175

4.200

4.225

V

Constant Voltage Mode

I

BAT

= 10mA, 4.75V

V

CC

6.5V

q

4.158

4.200

4.242

V

I

BAT

Output Full-Scale Current in

R

PROG

= 5k, 4.75V

V

CC

6.5V,

137

183

228

mA

Constant Current Mode

Pass PNP Beta > 50, 0

∞

C

T

A

85

∞

C

R

PROG

= 1.43k, 4.75V

V

CC

6.5V,

590

640

690

mA

Pass PNP Beta > 50, 0

∞

C

T

A

85

∞

C

I

DSINK

Drive Output Current

V

DRIVE

= 3V

q

30

mA

I

TRIKL

Trickle Charge Current

V

BAT

= 2V, R

PROG

= 5k

5

7

10

mA

V

BAT

= 2V, R

PROG

= 1.43k

12

20

28

mA

V

TRIKL

Trickle Charge Threshold

V

BAT

Falling

q

2.73

2.80

2.87

V

V

TRIKL

Trickle Charge Hysteresis

45

70

95

mV

V

PROG1

PROG Pin Voltage

R

PROG

= 5k (I

PROG

= 200

µ

A)

q

0.98

1

1.02

V

V

PROG2

PROG Pin Voltage

R

PROG

= 1.43k (I

PROG

= 700

µ

A)

q

0.98

1

1.02

V

LTC4056-4.2

3

405642i

ELECTRICAL CHARACTERISTICS

The

q

denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at T

A

= 25

∞

C. V

CC

= 5V.

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

PI FU CTIO S

U

U

U

V

CC

(Pin 1): Positive Input Supply Voltage. This pin

supplies power to the internal control circuitry and exter-

nal PNP transistor through the internal current sense

resistor. This pin should be bypassed to ground with a

capacitor in the range of 1

µ

F to 10

µ

F.

I

SENSE

(Pin 2): Sense Node for Charge Current. Current

from V

CC

passes through the internal current sense resis-

tor and out of the I

SENSE

pin to supply current to the emitter

of the external PNP transistor. The collector of the PNP

provides charge current to the battery.

DRIVE (Pin 3): Base Drive Output for the External PNP

Pass Transistor. Provides a controlled sink current that

drives the base of the PNP. This pin has current limiting

protection.

GND (Pin 4): Ground. Provides a reference for the internal

voltage regulator and a return for all internal circuits.

When in the constant voltage mode, the LTC4056 will

precisely regulate the voltage between the BAT and GND

pins. The battery ground should connect close to the GND

pin to avoid voltage drop errors.

BAT (Pin 5): Battery Voltage Sense Input. A precision

internal resistor divider sets the final float voltage on this

pin. This divider is disconnected in the manual shutdown

or sleep mode. No bypass capacitance is needed on this

pin for stable operation when a battery is present. How-

ever, any low ESR capacitor exceeding 22

µ

F on this pin

should be decoupled with 0.2

to 1

resistor. Without a

battery, a minimum bypass capacitance of 4.7

µ

F with

0.5

series resistance is required.

PROG (Pin 6): Charge Current Programming Pin. Pro-

vides a virtual reference voltage of 1V for an external

resistor (R

PROG

) connected between this pin and ground

to program the battery charge current. The typical charge

current is 915 times the current through this resistor (I

BAT

= 915V/R

PROG

). Current is limited to approximately 1.4mA

(I

BAT

of approximately 1.4A).

V

RECHRG

Recharge Voltage Threshold

V

FLOAT

≠ V

RECHRG

, V

BAT

> V

TRIKL

,

100

150

200

mV

Charge Termination Timer Expired

T

TIMER

TIMER/SHDN Accuracy

C

TIMER

= 1

µ

F R

PROG

= 1.43k

q

10

12

%

Charger Manual Control

V

MSDT

Manual Shutdown Threshold

V

TIMER/SHDN

Increasing

q

0.6

0.82

1

V

V

MSHYS

Manual Shutdown Hysteresis

V

TIMER/SHDN

Decreasing

50

75

125

mV

I

SHDN

TIMER/SHDN Pin Pull-up Current

V

TIMER/SHDN

= 0V

≠ 10

≠ 7

≠ 4

µ

A

Protection

I

DSHRT

Drive Output Short-Circuit Current Limit

V

DRIVE

= V

CC

q

30

65

130

mA

I

PSHRT

PROG Pin Short-Circuit Current Limit

V

PROG

= 0V

1.4

mA

Status Output

I

CHRG

CHRG Pin Weak Pull-Down Current

V

CHRG

= 1V, V

TIMER/SHDN

= 0V

6

12

18

µ

A

V

CHRG

CHRG Output Low Voltage

I

CHRG

= 10mA

q

0.2

0.4

V

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: The LTC4056E is guaranteed to meet performance specifications

from 0

∞

C to 70

∞

C ambient temperature range. Specifications over the

≠ 40

∞

C to 85

∞

C operating ambient temperature range are assured by

design, characterization and correlation with statistical process controls.

Note 3: Although the LTC4056 will operate with input voltages as low as

4.5V, charging will not begin until V

CC

exceeds V

UVCL

.

Note 4: Assumes that the external PNP pass transistor has negligible B-C

reverse-leakage current when the collector is biased at 4.2V (V

BAT

) and the

base is biased at 5V (V

CC

).

Note 5: Assumes that the external PNP pass transistor has negligible B-E

reverse-leakage current when the emitter is biased at 0V (V

CC

) and the

base is biased at 4.2V (V

BAT

).

LTC4056-4.2

4

405642i

an internal N-channel MOSFET. When the timer has timed

out (terminating the charge cycle) or when the LTC4056 is

in shutdown, but power is applied to the IC (i.e., V

CC

>

V

UVLOI

), a 12

µ

A current source is connected from the

CHRG pin to ground. The CHRG pin is forced to a high

impedance state when input power is not present (i.e., V

CC

< V

UVLOD

).

TIMER/SHDN (Pin 7): Programmable Charge Termination

Timer and Shutdown Input. Pulling this pin below the

shutdown threshold voltage will shut down the charger

reducing the supply current to approximately 40

µ

A and

the battery drain current to near 0

µ

A. A capacitor on this

pin programs the charge termination timer.

CHRG (Pin 8): Open-Drain Charge Status Output. When

the battery is being charged, the CHRG pin is pulled low by

PI FU CTIO S

U

U

U

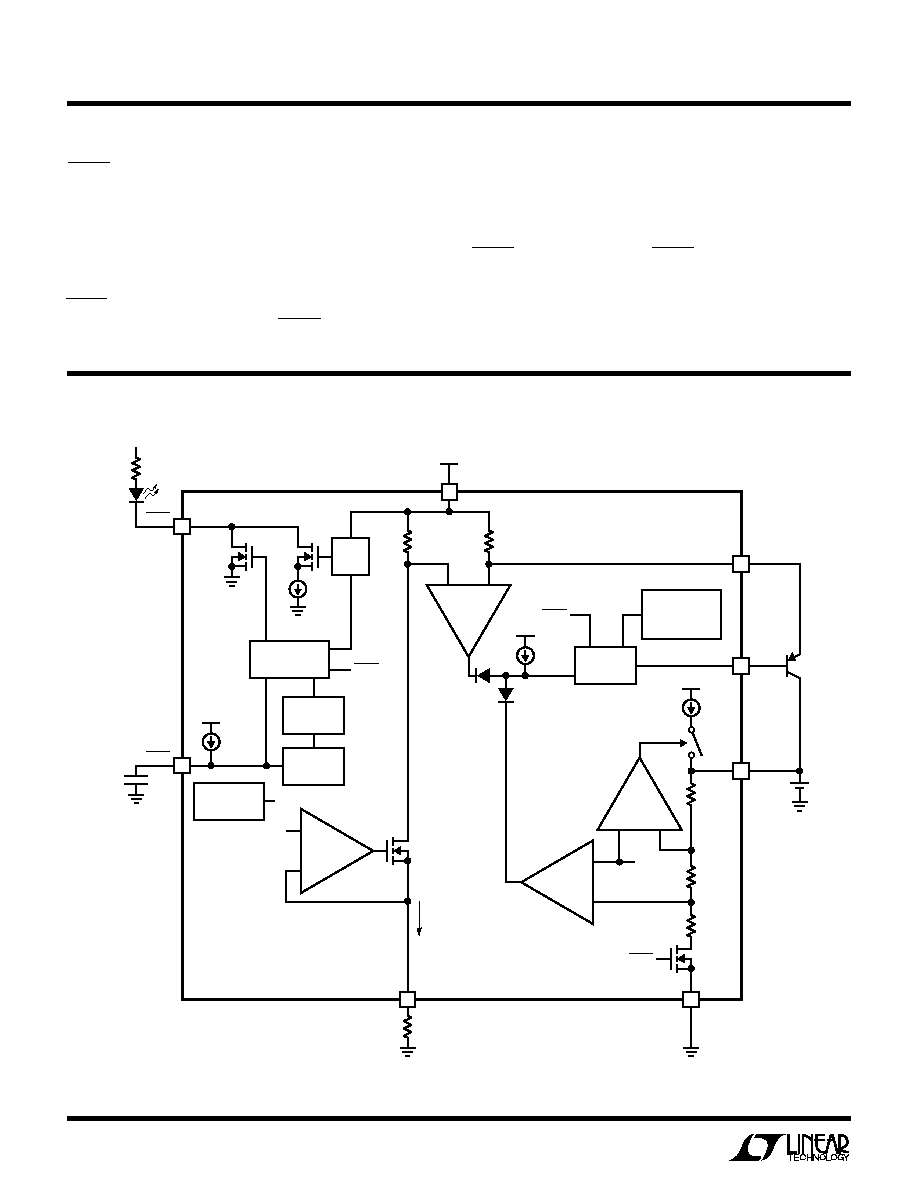

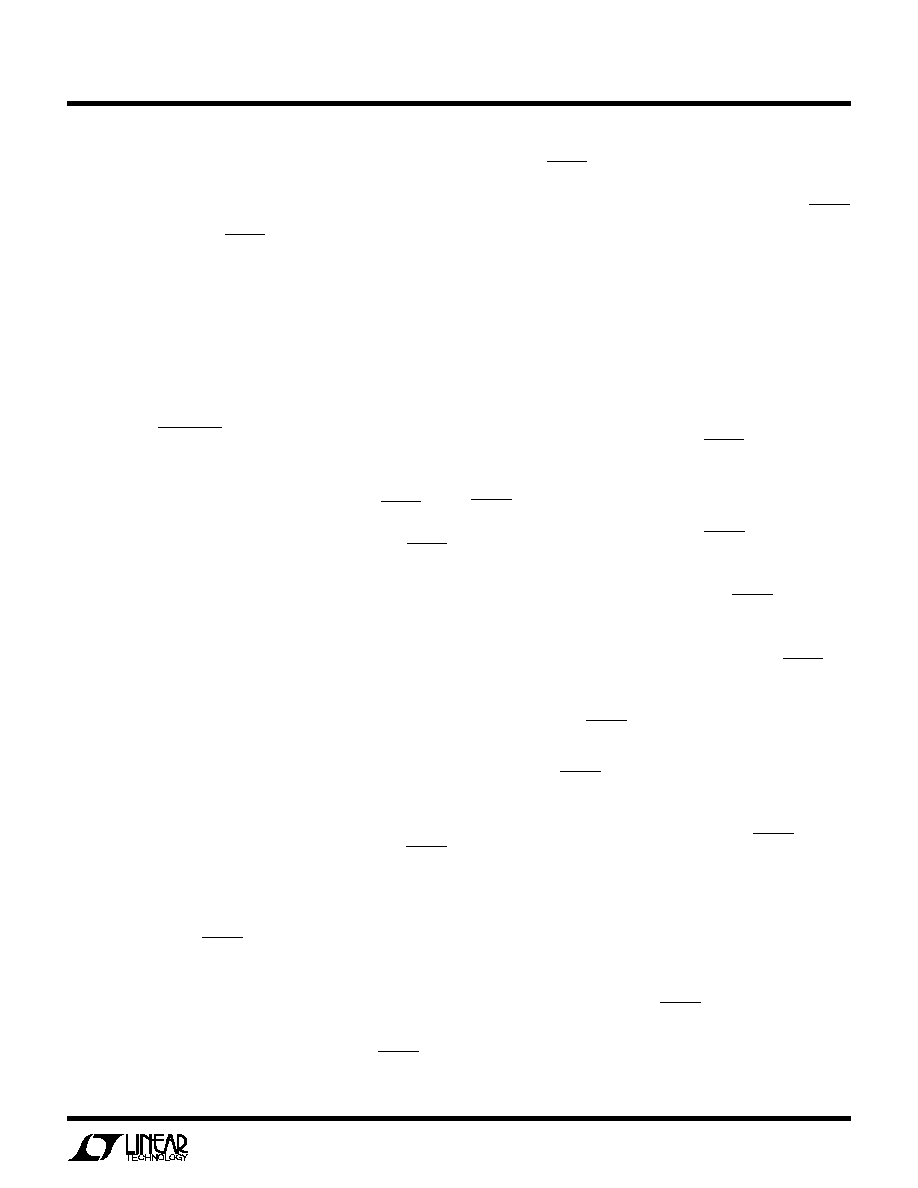

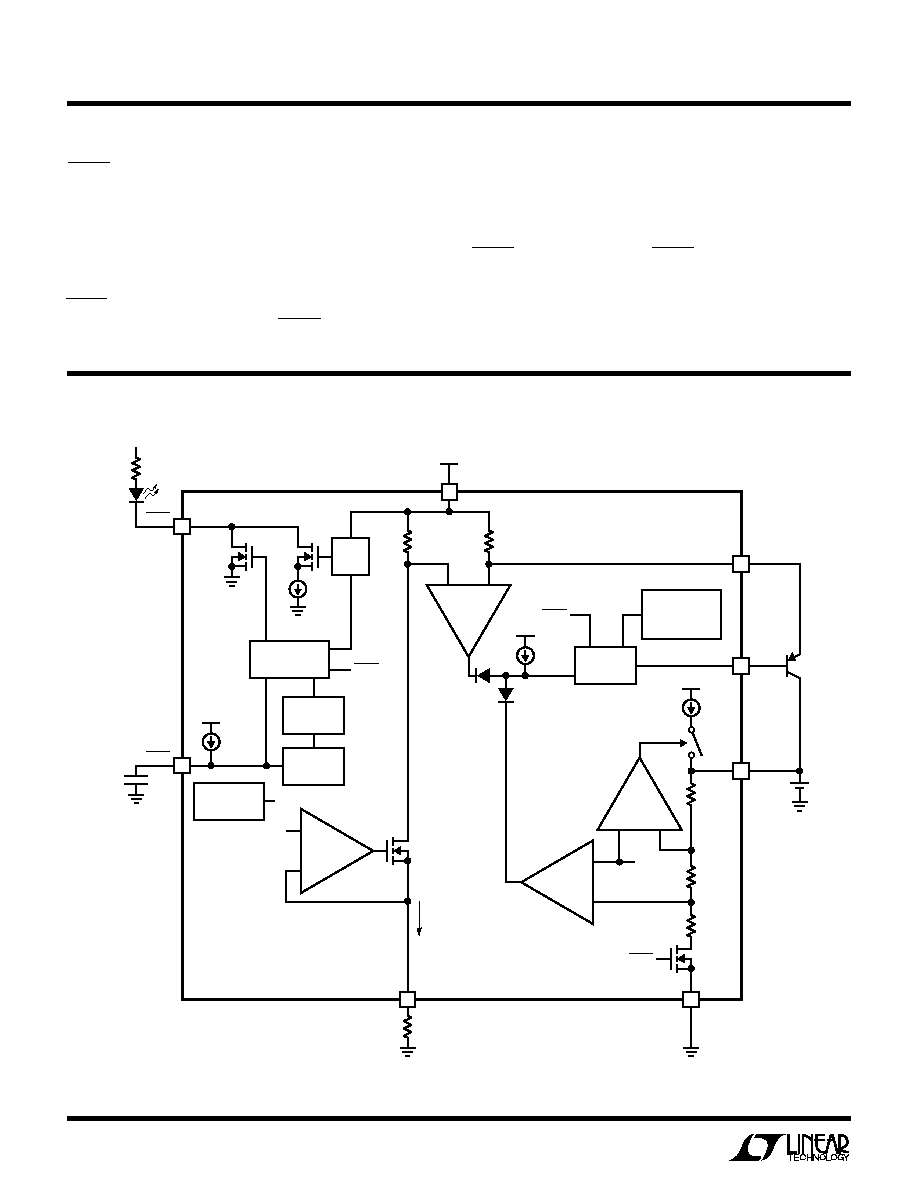

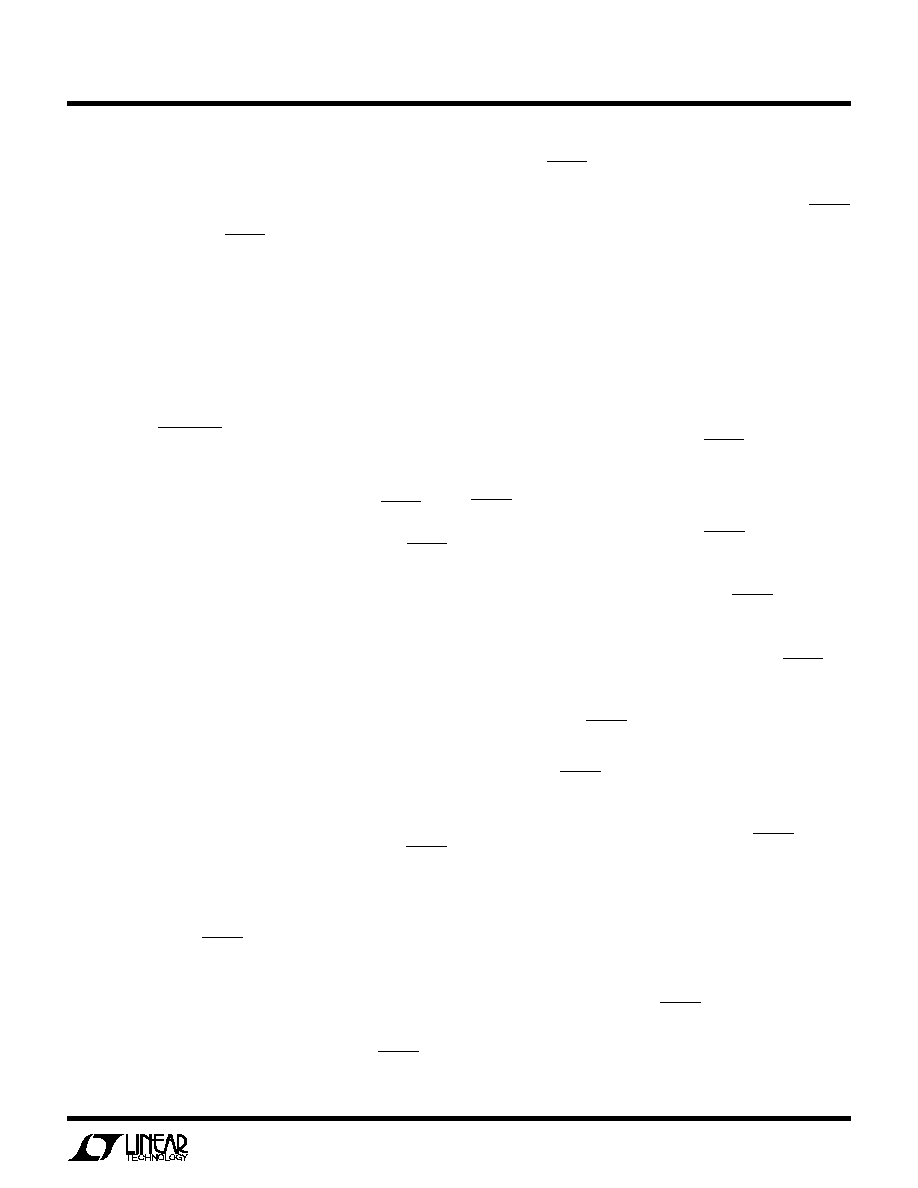

BLOCK DIAGRA

W

≠

+

≠

+

4056-4.2 BD

LTC4056-4.2

110m

V

CC

100

10

µ

A

CHRG

I

SENSE

R

PROG

1.2V

UVLO

COUNTER

OSCILLATOR

TIMER/SHDN

SHDN

LOGIC

CHRG

SHDN

SHDN

SHDN

UV

IA

CA

1V

REF

1.2V VOLTAGE

REFERENCE

OUTPUT

DRIVER

TEMPERATURE

AND

CURRENT LIMIT

DRIVE

BAT

≠

+

VA

+

≠

C1

I

TRIKL

20 ∑ I

PROG

I

PROG

5

µ

A

+

20

µ

A

PROG

GND

LTC4056-4.2

5

405642i

As the battery accepts charge, its voltage rises. When it

reaches the preset float voltage of 4.2V, a precisely divided

down version of this voltage (1.2V) is compared to the

1.2V internal reference voltage by amplifier VA. If the

battery voltage attempts to exceed 4.2V (1.2V at the input

of amplifier VA), the amplifier will divert current away from

the output driver thus limiting charge current to maintain

4.2V on the battery. This is the constant voltage mode.

An external capacitor on the TIMER/SHDN pin and the

resistance between the PROG pin and ground set the total

charge time. When this time elapses, the charge cycle

terminates and the CHRG pin transitions from a strong

pull-down to a weak 12

µ

A pull-down. To restart the charge

cycle, simply remove the input voltage and reapply it or

momentarily force the TIMER/SHDN pin to ground. The

charge cycle will also restart if the BAT pin voltage falls

below the recharge threshold (V

RECHRG

is nominally 4.05V).

When V

CC

is applied, pulling the TIMER/SHDN pin to

ground will manually shut down the charger and reset the

timer. When this pin is released an internal 7

µ

A current

source pulls the TIMER/SHDN pin above the 0.82V shut-

down threshold to resume charging.

Fault conditions such as overheating of the die or exces-

sive DRIVE pin or PROG pin current are monitored and

limited.

When input power is removed or manual shutdown is

entered, the charger will drain only tiny leakage currents

(<1

µ

A) from the battery, thus maximizing battery standby

time. With V

CC

removed the external PNP base is con-

nected to the battery by the charger. In manual shutdown

the base is connected to V

CC

by the charger.

OPERATIO

U

The LTC4056 is a linear battery charger controller with a

programmable charge termination timer. Operation can

be understood by referring to the Block Diagram. A charge

cycle begins when V

CC

rises above the UVLO (undervoltage

lockout) threshold V

UVLOI

(nominally 4.4V), an external

current programming resistor is connected between the

PROG pin and ground and the TIMER/SHDN pin is allowed

to rise above the shutdown threshold V

MSDT

(nominally

0.82V).

If the battery voltage is below V

TRIKL

(2.8V) at the begin-

ning of the charge cycle, the charger goes into trickle

charge mode to bring the cell voltage up to a safe level for

charging at full current. In this mode, an internal current

source provides approximately 2% of the programmed

charge current to the BAT pin. The charger goes into the

full charge constant current mode once the voltage on the

BAT pin rises above V

TRIKL

+

V

TRIKL

(2.9V).

During full current charging, the collector of the external

PNP provides the charge current. The PNP emitter current

flows through the I

SENSE

pin and through the internal

110m

current sense resistor. This current is close in

magnitude, but slightly more than the collector current

since it includes base current. Amplifier A1 forces 1V on

the PROG pin. Therefore, a current equal to 1V/R

PROG

will

flow through the internal 100

resistor. Amplifier CA will

force the same voltage that appears across the 100

resistor to appear across the internal 110m

resistor.

This amplifier ensures that the current flowing out of the

I

SENSE

pin is equal to 915 times the current flowing out of

the PROG pin. Therefore, neglecting base current, the

charge current will be 915V/R

PROG

. This region of opera-

tion is referred to as constant current mode.

LTC4056-4.2

6

405642i

APPLICATIO S I FOR ATIO

W

U

U

U

Undervoltage Lockout

An internal undervoltage lockout (UVLO) circuit monitors

the input voltage and keeps the charger in shutdown mode

until V

CC

rises above the UVLO threshold (V

UVLOI

is

typically 4.4V). Approximately 50mV of hysteresis is built

in to prevent oscillation around the threshold level. In

undervoltage lockout, battery drain current is very low

(<1

µ

A) and supply current is approximately 40

µ

A.

Undervoltage Charge Current Limiting

The LTC4056 includes undervoltage charge current limit-

ing that prevents full charge current until the input supply

voltage reaches a threshold value (V

UVCL

). This feature is

particularly useful if the LTC4056 is powered from a

supply with long leads (or any relatively high output

impedance).

For example, USB powered systems tend to have highly

variable source impedances (due primarily to cable quality

and length). A transient load combined with such an

impedance can easily trip the UVLO threshold and turn the

charger off unless undervoltage charge current limiting is

implemented.

Consider a situation where the LTC4056 is operating

under normal conditions and the input supply voltage

begins to sag (e.g. an external load drags the input supply

down). If the input voltage reaches V

UVCL

(approximately

170mV above the rising undervoltage lockout threshold,

V

UVLOI

), undervoltage charge current limiting will begin to

reduce the charge current in an attempt to maintain V

UVCL

at the V

CC

input of the IC. The LTC4056 will continue to

operate at the reduced charge current until the input

supply voltage is increased or voltage mode reduces the

charge current further.

Trickle Charge and Defective Battery Detection

At the beginning of a charge cycle, if the battery voltage is

low (below V

TRIKL

of about 2.8V) the charger goes into

trickle charge mode reducing the charge current to ap-

proximately 2% of the full-scale current. If the low battery

voltage persists for one quarter of the total charge time,

the battery is assumed to be defective, the charge cycle is

terminated and the CHRG pin output transitions from a

strong pull-down to a 12

µ

A pull-down. To restart the

charge cycle, simply remove the input voltage and reapply

it or momentarily force the TIMER/SHDN pin to ground.

Programming Charge Current

When in the constant current mode, the full-scale charge

current is programmed using a single external resistor

between the PROG pin and ground, R

PROG

. The current

delivered to the I

SENSE

pin (flowing from V

CC

through the

internal 110m

sense resistor) will be 915 times the

current in R

PROG

. Because the LTC4056 provides a virtual

1V source at the PROG pin, the charge current is given by:

I

I

V

R

or

R

V

I

CHRG

PROG

PROG

PROG

CHRG

=

( )

=

=

∑

∑

∑

915

1

915

1

915

Under trickle charge conditions, this current is reduced to

approximately 2% of the full-scale value. The actual bat-

tery charge current (I

BAT

) is slightly lower than the ex-

pected charge current because the charger forces the

emitter current and the battery charge current will be

reduced by the base current. In terms of

(I

C

/I

B

), I

BAT

can

be calculated as follows:

I

A

I

V

R

BAT

PROG

PROG

( )

=

+

=

+

915

1

915

1

∑

∑

If

= 50, then I

BAT

is 2% low. If desired, reducing R

PROG

by 2% can compensate for the 2% loss.

For example, if 700mA charge current is required, calcu-

late:

R

V

mA

k

PROG

=

=

1

700

915

1 3

∑

.

If a low

needs to be compensated for, say

= 50,

calculate:

R

V

mA

k

PROG

=

+

=

915

700

50

50 1

1 27

∑

.

For best stability over temperature and time, 1% metal-

film resistors are recommended.

LTC4056-4.2

7

405642i

APPLICATIO S I FOR ATIO

W

U

U

U

Termination Timer

The programmable timer is used to terminate the charge

cycle. The timer duration is programmed by an external

capacitor at the TIMER/SHDN pin and the external PROG

resistor. The total charge time is:

Time(Hours) = 2.1 ∑ R

PROG

(k) ∑ C

TIMER

(

µ

F) or

C

TIMER

(

µ

F) = Time(Hours)/2.1 ∑ R

PROG

(k)

For example, to program a three hour timer with a 640mA

charge current (i.e., R

PROG

= 1.43k), calculate:

C

F

TIMER

=

= µ

3

2 1 1 43

1

. ∑ .

The timer starts when an input voltage greater than the

undervoltage lockout threshold level is applied, a program

resistor is connected to ground and the TIMER/SHDN pin

is allowed to rise above the shutdown threshold. After a

time-out occurs, the charge current stops and the CHRG

output transitions from a strong pull-down to a 12

µ

A pull-

down to indicate charging has stopped. As long as the

input supply remains above V

UVLOD

and the battery volt-

age remains above V

RECHRG

the charger will remain in this

standby mode.

If the battery voltage remains below V

TRIKL

for 25% of the

programmed time, the charger will enter standby mode.

Furthermore, if the battery voltage is above the recharge

threshold (V

RECHRG

is typically 4.05V) at the beginning of

a charge cycle or if a falling battery voltage triggers a

recharge cycle (following a previous time-out), the charger

will enter standby mode after 50% of the programmed

time. This feature reduces the charge time for batteries

that are near full capacity. Connecting the TIMER/SHDN

pin to V

CC

disables the timer function.

Manual Shutdown

Pulling the TIMER/SHDN pin below V

MSDT

≠ V

MSHYS

(typically 0.745V) will put the charger into shutdown

mode. In this mode, the LTC4056 consumes 40

µ

A of

supply current and drains a negligible leakage current

from the battery (I

BMS

).

A 7

µ

A current source pulls up on the TIMER/SHDN pin

while in shutdown to ensure that the IC will start up once

the TIMER/SHDN pin is released. Given the low magnitude

of this current, it is a simple matter for an external open-

drain (or open-collector) output to pull the TIMER/SHDN

pin to ground for shutdown and release the pin for normal

operation.

Sleep Mode

When the input supply is disconnected, the IC enters the

sleep mode. In this mode, the battery drain current (I

BSL

)

is a negligible leakage current, allowing the battery to

remain connected to the charger for an extended period of

time without discharging the battery. The leakage current

is due to the reverse-biased B-E junction of the external

PNP transistor. Furthermore, the CHRG pin assumes a

high impedance state.

CHRG Status Output Pin

When the charge cycle starts, the CHRG pin is pulled to

ground by an internal N-channel MOSFET capable of

driving an LED. Upon termination, the strong pull-down

transitions to a 12

µ

A pull-down on the CHRG pin as long

as the input supply remains above the UVLO threshold

(V

UVLOD

) and the battery voltage remains above V

RECHRG

.

If the input supply falls below V

UVLOD

, the CHRG pin

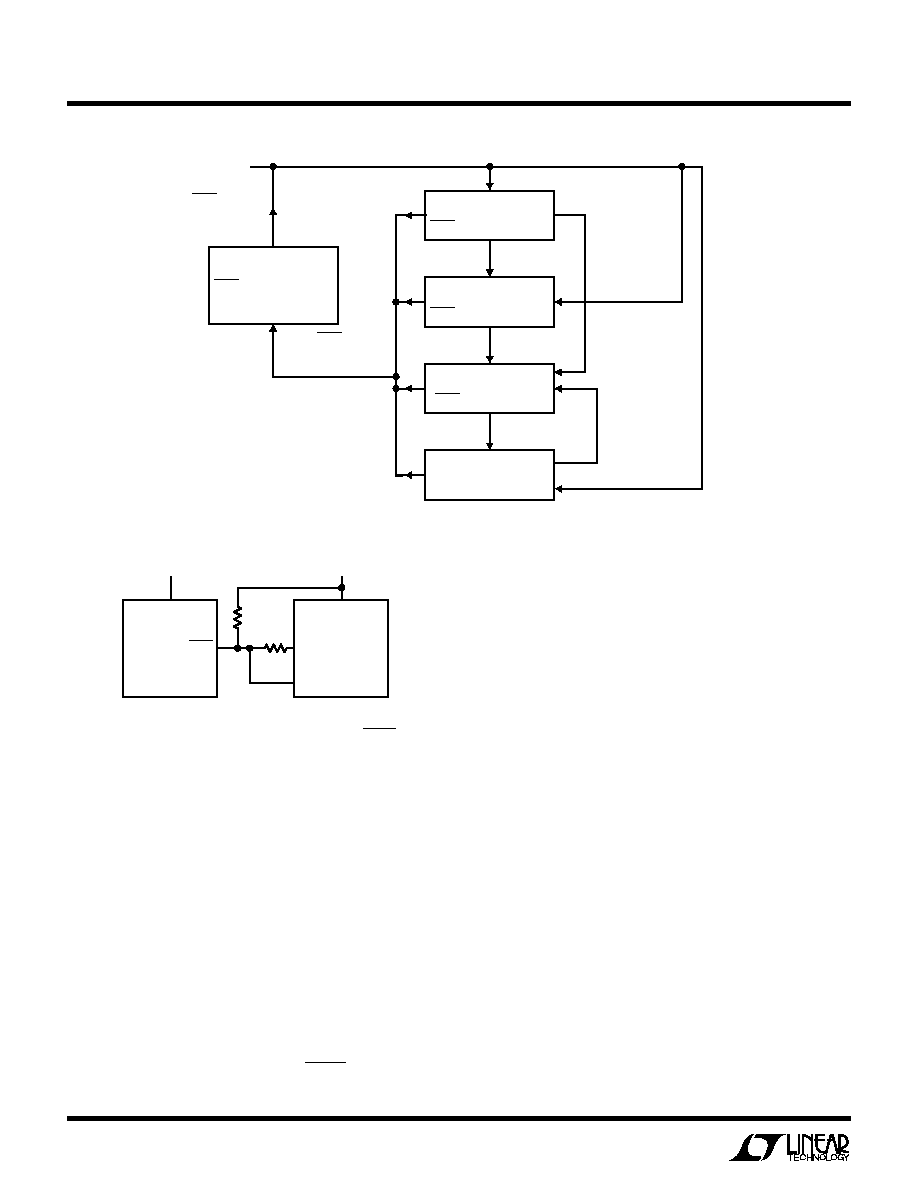

assumes a high impedance state. Figure 1 shows a flow

diagram for a typical charge cycle. This diagram indicates

the status of the CHRG pin in each charger state.

A microprocessor can be used to distinguish the three

states of the CHRG pin (see Figure 2). To detect whether

the LTC4056 is in trickle charge, charge, or short charge

mode (i.e., strong pull-down), force the digital output pin

(OUT) high and measure the voltage at the CHRG pin. The

internal N-channel MOSFET will pull the pin voltage low

even with the 2k pull-up resistor. Once the charge cycle

terminates, the strong pull-down transitions to a 12

µ

A

pull-down. The IN pin will then be pulled high by the 2k

pull-up resistor. To determine whether sufficient input

voltage is present for charging (i.e., high impedance), the

OUT pin should be forced to a high impedance state. If

V

CC

> V

UVLOI

then the 12

µ

A CHRG pull-down will pull the

IN pin low through the 800k resistor; otherwise, the 800k

resistor will pull the IN pin high, indicating that

V

CC

< V

UVLOD

.

LTC4056-4.2

8

405642i

CHRG

8

2k

800k

V

CC

1

LTC4056

V

+

4056-4.2 F02

OUT

IN

µ

PROCESSOR

V

DD

Figure 2. Using a Microprocessor to Determine CHRG State

Recharge

If the battery voltage drops below V

RECHRG

(typically

4.05V) after a charge cycle has terminated, a new charge

cycle will begin. The recharge circuit integrates the BAT

pin voltage for approximately a millisecond to prevent a

transient from restarting the charge cycle. During a re-

charge cycle the timer will terminate the charge cycle after

one-half of the programmed time has elapsed.

If the battery voltage remains below V

TRIKL

(typically 2.8V)

during trickle charge for one-fourth of the programmed

time, the battery may be defective and the charge cycle will

end. In addition, the recharge comparator is disabled and

a new charge cycle will not begin unless the input voltage

is toggled off then on, or the TIMER/SHDN pin is momen-

tarily pulled to ground.

External PNP Transistor

The external PNP pass transistor must have adequate

beta, low saturation voltage and sufficient power dissipa-

tion capability (including any heat sinking, if required).

To provide 700mA of charge current with the minimum

available base drive of approximately 30mA requires a

PNP beta greater than 23. If lower beta PNP transistors are

used, more base current is required from the LTC4056.

This can result in the output drive current limit being

reached, or thermal shutdown due to excessive power

dissipation.

With low supply voltages, the PNP saturation voltage

(V

CESAT

) becomes important. The V

CESAT

must be less

than the minimum supply voltage minus the maximum

voltage drop across the internal sense resistor and bond

wires (0.20

) and battery float voltage. If the PNP transis-

tor cannot achieve the low saturation voltage required,

base current will dramatically increase. This is to be

avoided for a number of reasons: output drive may reach

current limit resulting in the charger characteristics to go

out of specifications, excessive power dissipation may

force the IC into thermal shutdown, or the battery could

become discharged because some of the current from the

APPLICATIO S I FOR ATIO

W

U

U

U

TRICKLE CHARGE MODE

2% FULL CURRENT

CHRG: STRONG PULLDOWN

BAT > 2.9V

2.8V < BAT < 4.05V

BAT > 4.05V

BAT < 2.8V

CHARGE MODE

FULL CURRENT

CHRG: STRONG PULLDOWN

PROGRAMMED

TIME ELAPSES

25% PROGRAMMED

TIME ELAPSES

50%

PROGRAMMED

TIME ELAPSES

STANDBY MODE

NO CHARGE CURRENT

CHRG: WEAK PULLDOWN

2.8V < BAT < 4.05V

4056-4.2 F01

RECHARGE/SHORT

CHARGE MODE

CHRG: STRONG PULLDOWN

SHUTDOWN MODE

I

CC

DROPS TO < 40

µ

A

CHRG: Hi-Z if V

CC

< V

UVLOD

WEAK PULLDOWN

OTHERWISE

TIMER/SHDN GROUNDED

OR

V

CC

< V

UVLOD

TIMER/SHDN RELEASED

OR

V

CC

> V

UVLOI

POWER ON

Figure 1. State Diagram for a Typical Charge Cycle

LTC4056-4.2

9

405642i

DRIVE pin could be pulled from the battery through the

forward biased collector base junction.

For example, to program a charge current of 500mA with

a minimum supply voltage of 4.75V, the minimum operat-

ing V

CE

is:

V

CE(MIN)

(V) = 4.75 ≠ (0.5) ∑ (0.2) ≠ 4.2 = 0.45V

Another important factor to consider when choosing the

PNP pass transistor is the power handling capability. The

transistor data sheet will usually give the maximum rated

power dissipation at a given ambient temperature with a

power derating for elevated temperature operation. The

maximum power dissipation of the PNP when charging is:

P

D(MAX)

(W) = I

BAT

∑ (V

CC(MAX)

≠ V

BAT(MIN)

)

V

CC(MAX)

is the maximum supply voltage and V

BAT(MIN)

is

the minimum battery voltage when discharged.

Once the maximum power dissipation and V

CE(MIN)

are

known, Table 1 can be used as a guide in selecting some

PNPs to consider. In the table, very low V

CESAT

is less than

0.25V, low V

CESAT

is 0.25V to 0.5V and the others are 0.5V

to 0.8V all depending on the current. See the manufacturer

data sheet for details. All of the transistors are rated to

carry at least 1A continuously as long as the power

dissipation is within limits. In addition, the maximum

supply voltage, minimum battery voltage and chosen

APPLICATIO S I FOR ATIO

W

U

U

U

charge current should be checked against the

manufacturer's data sheet to ensure that the PNP transis-

tor is operating within its safe operating area. The Stability

section addresses caution in the use of very high beta

PNPs.

Should overheating of the PNP transistor be a concern,

protection can be achieved with a positive temperature

coefficient (PTC) thermistor wired in series with the

current programming resistor and thermally coupled to

the transistor. The PTH9C chip series from Murata has a

steep resistance increase at temperature thresholds from

85

∞

C to 145

∞

C making it behave somewhat like a thermo-

stat switch. For example, the model PTH9C16TBA471Q

thermistor is 470

at 25

∞

C but abruptly increases its

resistance to 4.7k at 125

∞

C. Below 125

∞

C, the device

exhibits a small negative TC. The 470

thermistor can be

added in series with a 976

resistor to form the current

programming resistor for a 640mA charger. Should the

thermistor reach 125

∞

C, the charge current will drop to

160mA and inhibit any further increase in temperature.

Stability

The LTC4056 contains two control loops: constant volt-

age and constant current. The constant voltage loop is

stable without any compensation when a battery is con-

nected with low impedance leads. Excessive lead length,

Table 1. PNP Pass Transistor Selection Guide

MAXIMUM P

D

(W)

MOUNTED ON BOARD

AT T

A

= 25

∞

C

PACKAGE STYLE

ZETEX PART NUMBER

ROHM PART NUMBER

COMMENTS

3

2 x 2MLP

ZXT1M322

Very Low V

CESAT

0.5

SOT-23

FMMT549

Low V

CESAT

0.625

SOT-23

FMMT720

Very Low V

CESAT

, High Beta

1

SOT-89

FCX589 or BCX69

1.1

SOT-23-6

ZXT13P12DE6

Very Low V

CESAT

, High Beta, Small

1 to 2

SOT-89

FCX717

Very Low V

CESAT

, High Beta

2

SOT-223

FZT589

Low V

CESAT

2

SOT-223

BCP69 or FZT549

0.75

FTR

2SB822

Low V

CESAT

1

ATV

2SB1443

Low V

CESAT

2

SOT-89

2SA1797

Low V

CESAT

10 (T

C

= 25

∞

C)

TO-252

2SB1182

Low V

CESAT

, High Beta

LTC4056-4.2

10

405642i

however, may add enough series inductance to require a

bypass capacitor of at least 1

µ

F from BAT to ground.

Furthermore, a 4.7

µ

F capacitor with a 0.2

to 1

series

resistor from BAT to ground is required to keep ripple

voltage low when the battery is disconnected.

High value capacitors with very low ESRs (especially

ceramic) reduce the constant voltage loop phase margin,

possibly resulting in instability. Ceramic capacitors up to

22

µ

F may be used in parallel with a battery, but larger

ceramics should be decoupled with 0.2

to 1

of series

resistance.

In the constant current mode, the PROG pin is in the

feedback loop, not the battery. Because of the additional

pole created by PROG capacitance, capacitance on this pin

must be limited. Although higher charge current applica-

tions (i.e., lower program resistance) can tolerate more

PROG capacitance, a good rule of thumb is to keep the

capacitive loading on the PROG pin to less than 660pF.

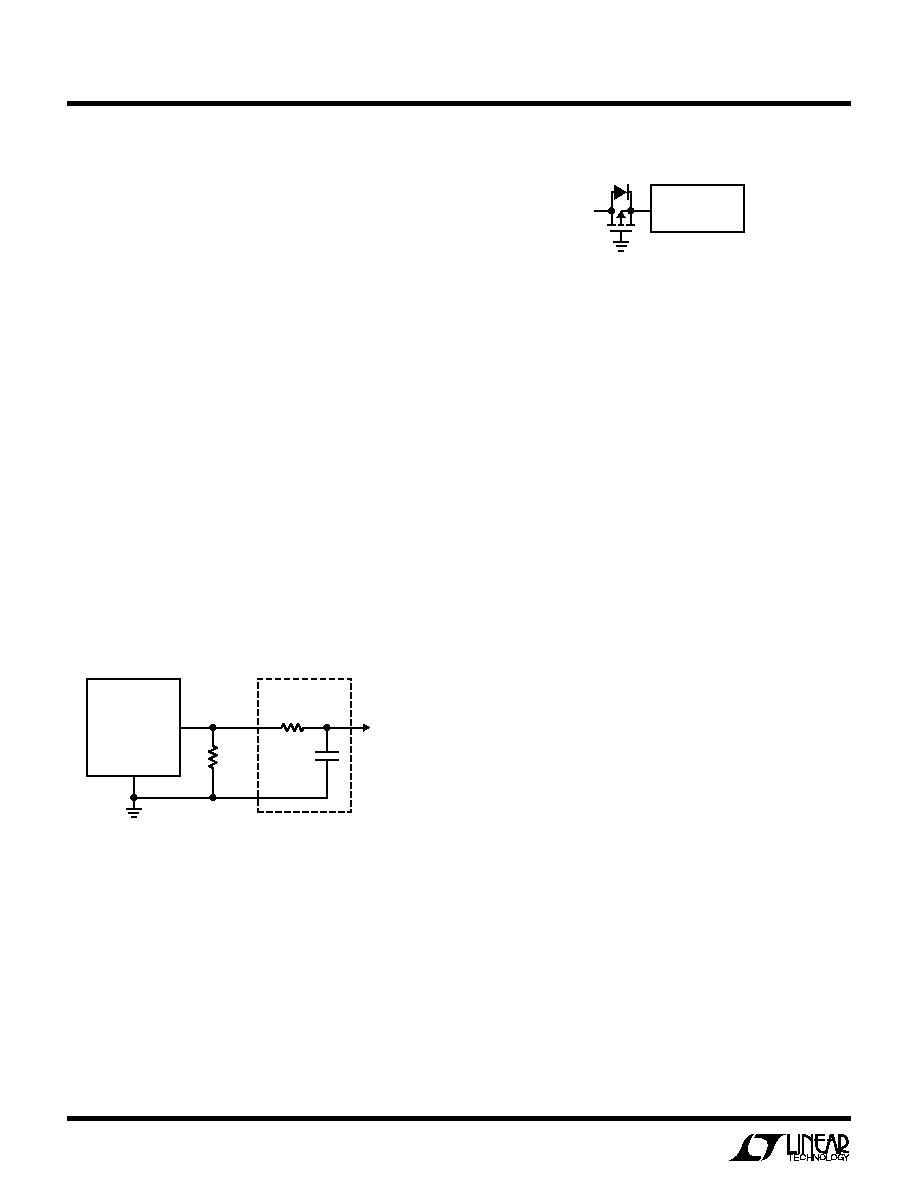

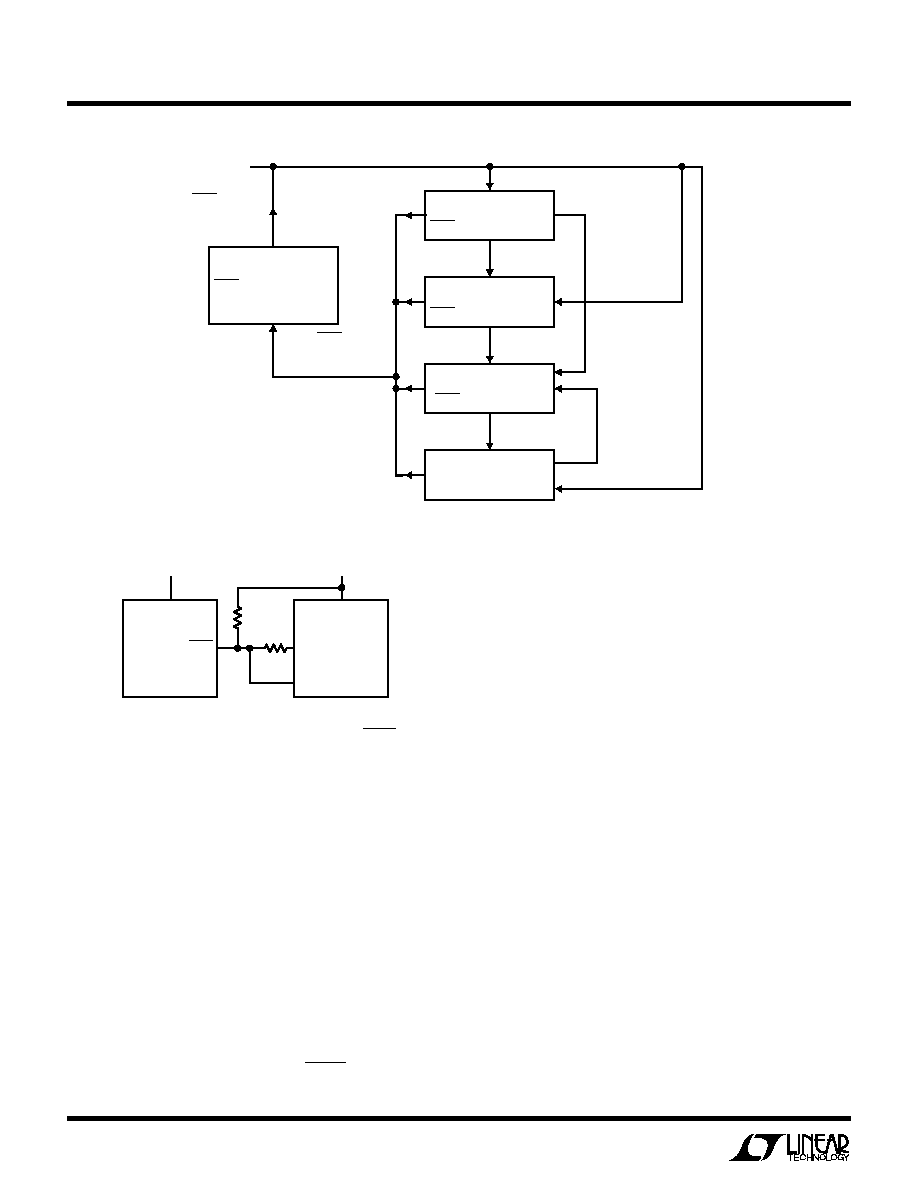

If additional capacitance on this pin is required (e.g., to

provide an accurate, filtered low current 1V reference to

external circuitry) a 1k to 10k decoupling resistor may be

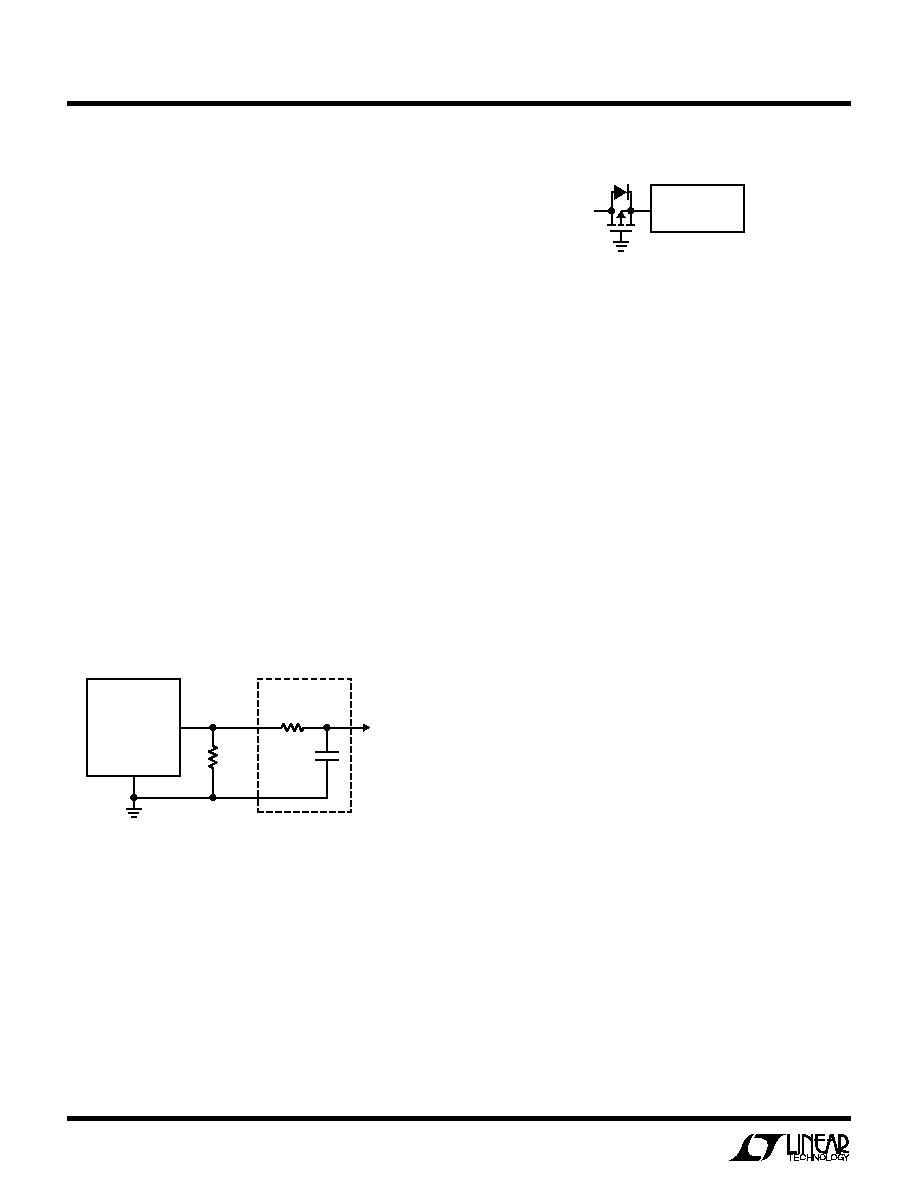

needed (see Figure 3).

PROG

6

4

GND

LTC4056

4056-4.2 F03

10k

C

FILTER

R

PROG

ACCURATE,

FILTERED 1V

REFERENCE

Figure 3. Isolating Capacitive Load on PROG Pin and Filtering

Reverse Polarity Input Voltage Protection

In some applications, protection from reverse polarity

voltage on V

CC

is desired. If the supply voltage is high

enough, a series blocking diode can be used. In other

cases, where the voltage drop must be kept low, a P-channel

MOSFET can be used (as shown in Figure 4).

V

CC

V

IN

LTC4056

4056-4.2 F04

*

*DRAIN-BULK DIODE OF FET

Figure 4. Low Loss Input Reverse Polarity Voltage Protection

V

CC

Bypass Capacitor

Many types of capacitors with values ranging from 1

µ

F to

10

µ

F located close to the LTC4056 will provide adequate

input bypassing. However, caution must be exercised

when using multilayer ceramic capacitors. Because of the

self-resonant and high Q characteristics of some types of

ceramic capacitors, high voltage transients can be gener-

ated under some start-up conditions, such as connecting

the charger input to a hot power source. For more informa-

tion refer to Application Note 88.

Internal Protection

Internal protection is provided to prevent excessive PROG

pin currents (I

PSHRT

), excessive DRIVE pin currents

(I

DSHRT

) and excessive self-heating of the LTC4056 during

a fault condition. The faults can be generated from a

shorted PROG pin, a shorted DRIVE pin or from excessive

DRIVE pin current to the base of the external PNP transis-

tor when it is in deep saturation from a very low V

CE

. This

protection is not designed to prevent overheating of the

external pass transistor. However, thermal coupling be-

tween the external PNP and the LTC4056 will allow the

internal thermal limit to deprive the PNP of base current

when the junction temperature of the IC rises above about

135

∞

C. The temperature of the PNP at that point, however,

will be well in excess of 135

∞

C. The exact temperature of

the PNP depends on the thermal coupling between the

LTC4056 and the PNP and on the

JA

of the transistor. See

the section titled "External PNP Transistor" for informa-

tion on protecting the transistor from overheating.

APPLICATIO S I FOR ATIO

W

U

U

U

LTC4056-4.2

11

405642i

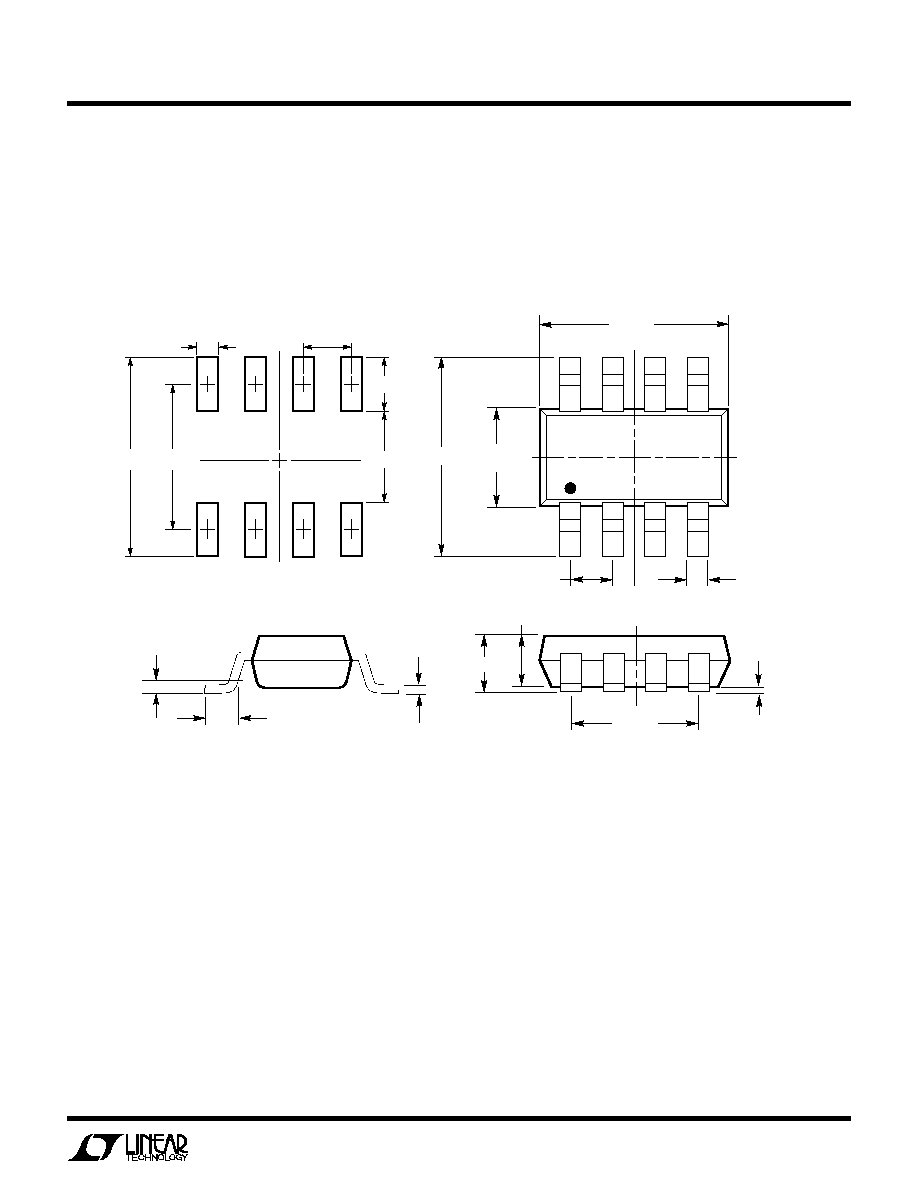

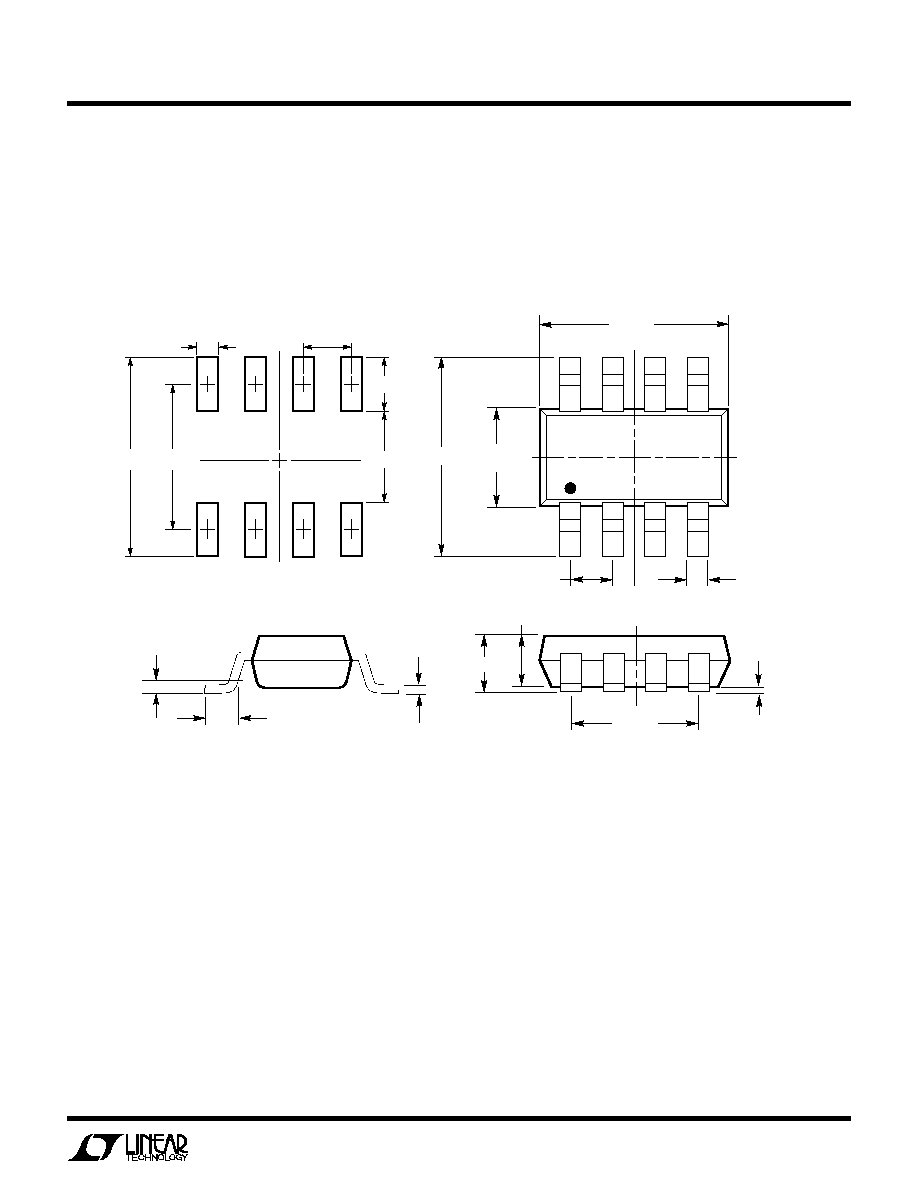

PACKAGE DESCRIPTIO

U

TS8 Package

8-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1637)

1.50 ≠ 1.75

(NOTE 4)

2.80 BSC

0.22 ≠ 0.36

8 PLCS (NOTE 3)

DATUM `A'

0.09 ≠ 0.20

(NOTE 3)

TS8 TSOT-23 0302

2.90 BSC

(NOTE 4)

0.65 BSC

1.95 BSC

0.80 ≠ 0.90

1.00 MAX

0.01 ≠ 0.10

0.20 BSC

0.30 ≠ 0.50 REF

PIN ONE ID

NOTE:

1. DIMENSIONS ARE IN MILLIMETERS

2. DRAWING NOT TO SCALE

3. DIMENSIONS ARE INCLUSIVE OF PLATING

4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

5. MOLD FLASH SHALL NOT EXCEED 0.254mm

6. JEDEC PACKAGE REFERENCE IS MO-193

3.85 MAX

0.52

MAX

0.65

REF

RECOMMENDED SOLDER PAD LAYOUT

PER IPC CALCULATOR

1.4 MIN

2.62 REF

1.22 REF

LTC4056-4.2

12

405642i

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900

q

FAX: (408) 434-0507

q

www.linear.com

©

LINEAR TECHNOLOGY CORPORATION 2003

LT/TP 0203 1.5K ∑ PRINTED IN USA

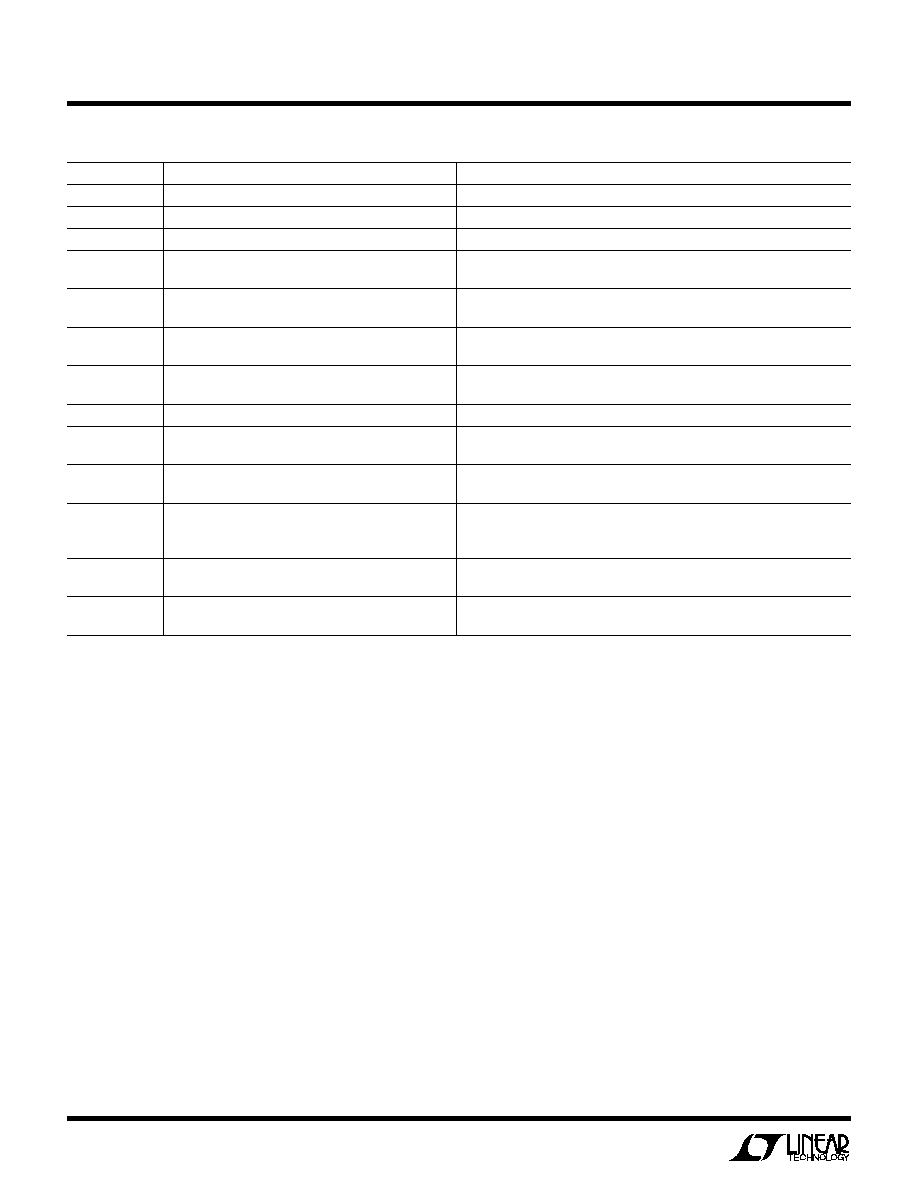

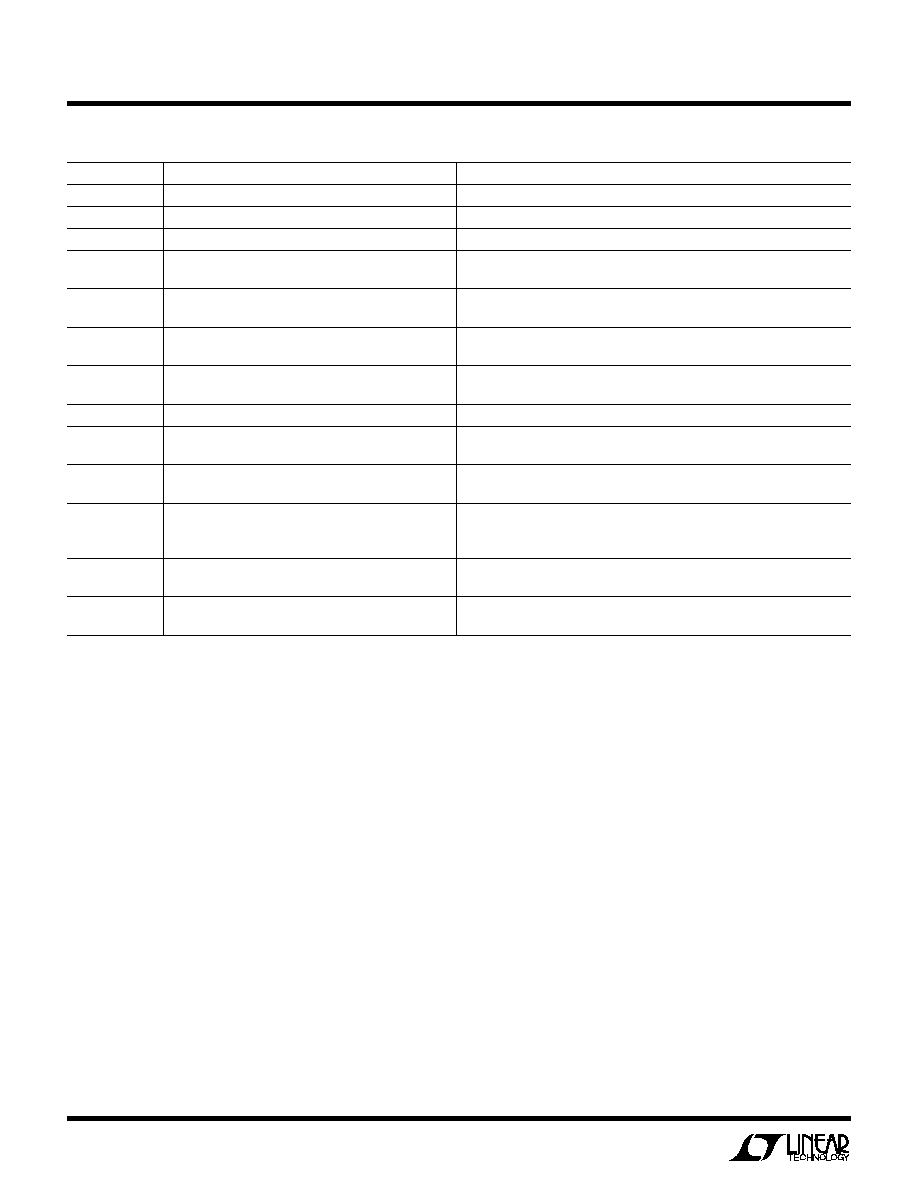

RELATED PARTS

PART NUMBER

DESCRIPTION

COMMENTS

LT1571

200kHz/500kHz Switching Battery Charger

Up to 1.5A Charge Current; Preset and Adjustable Battery Voltages

LTC1729

Lithium-Ion Battery Charger Termination Controllers

Time or Charge Current Termination, Preconditioning 8-Lead MSOP

LTC1730

Lithium-Ion Battery Pulse Charger

No Blocking Diode Required, Current Limit for Maximum Safety

LTC1731

Lithium-Ion Linear Battery Charger Controller

Simple Charger uses External FET, Features Preset Voltages, C/10

Charger Detection and Programmable Timer

LTC1732

Lithium-Ion Linear Battery Charger Controller

Simple Charger uses External FET, Features Preset Voltages, C/10

Charger Detection and Programmable Timer, Input Power Good Indication

LTC1733

Monolithic Lithium-Ion Linear Battery Charger

Standalone charger with Programmable Timer, Up to 1.5A Charge Current,

Thermal Regulation Prevents Overheating

LTC1734

Lithium-Ion Linear Battery Charger in ThinSOT

200mA to 700mA, Simple ThinSOT Charger, No Blocking Diode,

No Sense Resistor Needed

LTC1734L

Lithium-Ion Linear Battery Charger Controller

50mA to 180mA, No Blocking Diode, No Sense Resistor Needed

LTC4050

Lithium-Ion Linear Battery Charger Controller

Simple Charger uses External FET, Thermistor Input for

Battery Temperature Sensing

LTC4052

Lithium-Ion Linear Battery Pulse Charger

Fully Integrated, Standalone Pulse Charger, Minimal Heat Dissipation,

Over Current Protection

LTC4053

USB Compatible Lithium-Ion Battery

Fully Integrated, Standalone Charger, 10-Lead MSOP, Thermal Regulation

Linear Monolithic Charger

Prevents Overheating when Powered from Wall Adapter and

1A Charge Current

LTC4054

Standalone Lithium-Ion Linear Battery Charger

Programmable Charge Current Up to 800mA; C/10 Charge Termination,

in ThinSOT

Complete Charger; No External MOSFET, Diode or Sense Resistor

LTC4410

USB Power Manager

Manages Total Power Between a USB Peripheral and Battery Charger;

Ensures Simultaneous Charging and use of Peripheral, ThinSOT Package