1

M

e

m

o

r

y

All data sheets are subject to change without notice

(858) 503-3300- Fax: (858) 503-3301- www.maxwell.com

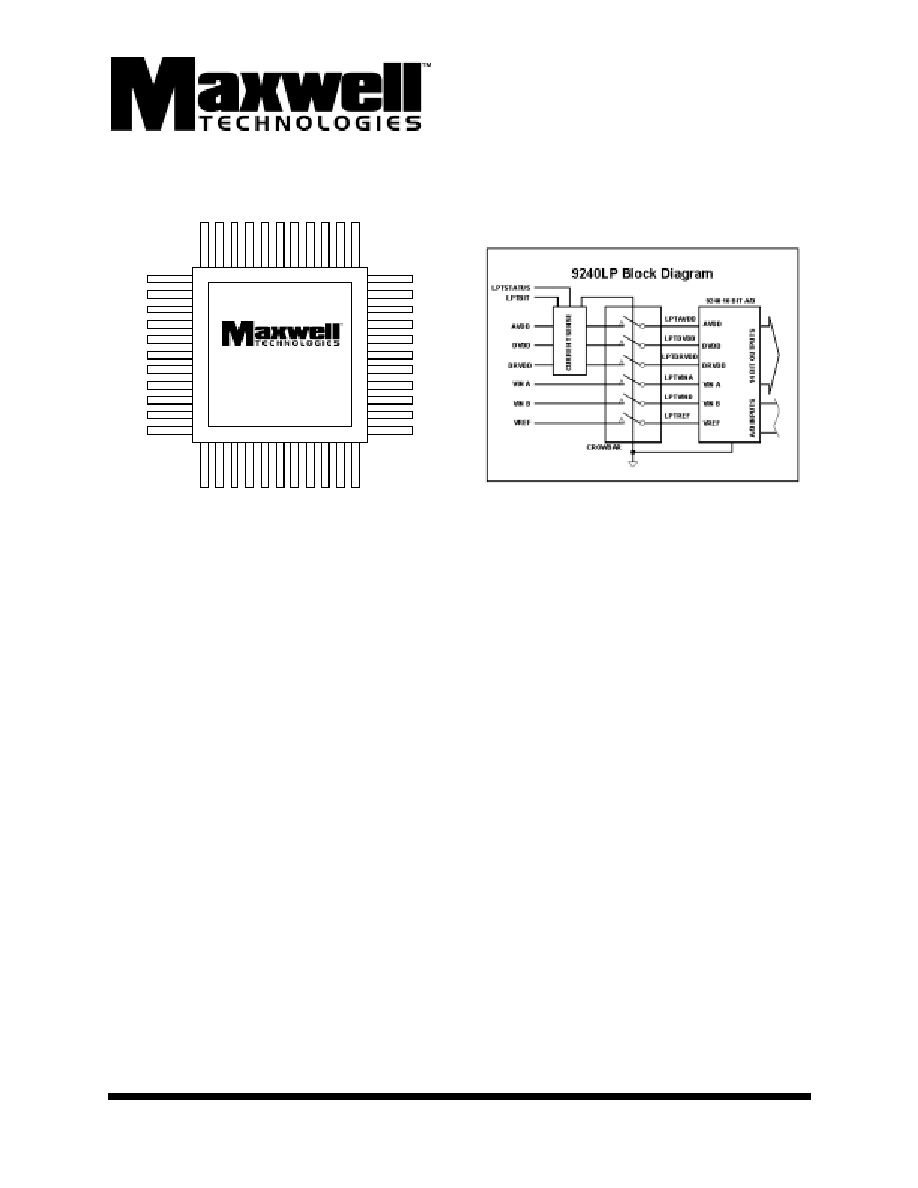

14-Bit, 10 MSPS Monolithic A/D

9240LP

©2002 Maxwell Technologies

All rights reserved.

Converter with LPT ASIC

06.13.02 Rev 5

F

EATURES

:

∑ R

AD

-P

AK

Æ radiation-hardened against natural space radia-

tion

∑ Low power dissipation: 285 mW

∑ Single 5 V supply

∑ Integral nonlinearity error: 2.5 LSB

∑ Differential nonlinearity error: 0.6 LSB

∑ Input referred noise: 0.36 LSB

∑ Complete: On-chip sample-and-hold amplifier and voltage

reference

∑ Signal-to-noise and distortion ratio: 77.5 dB

∑ Spurious-free dynamic range: 90 dB

∑ Out-of-range indicator

∑ Straight binary output data

∑ Total dose hardened to 100 Krads (Si), dependent on orbit

and mission duration

∑ Single Event Latchup (SEL) protected

D

ESCRIPTION

:

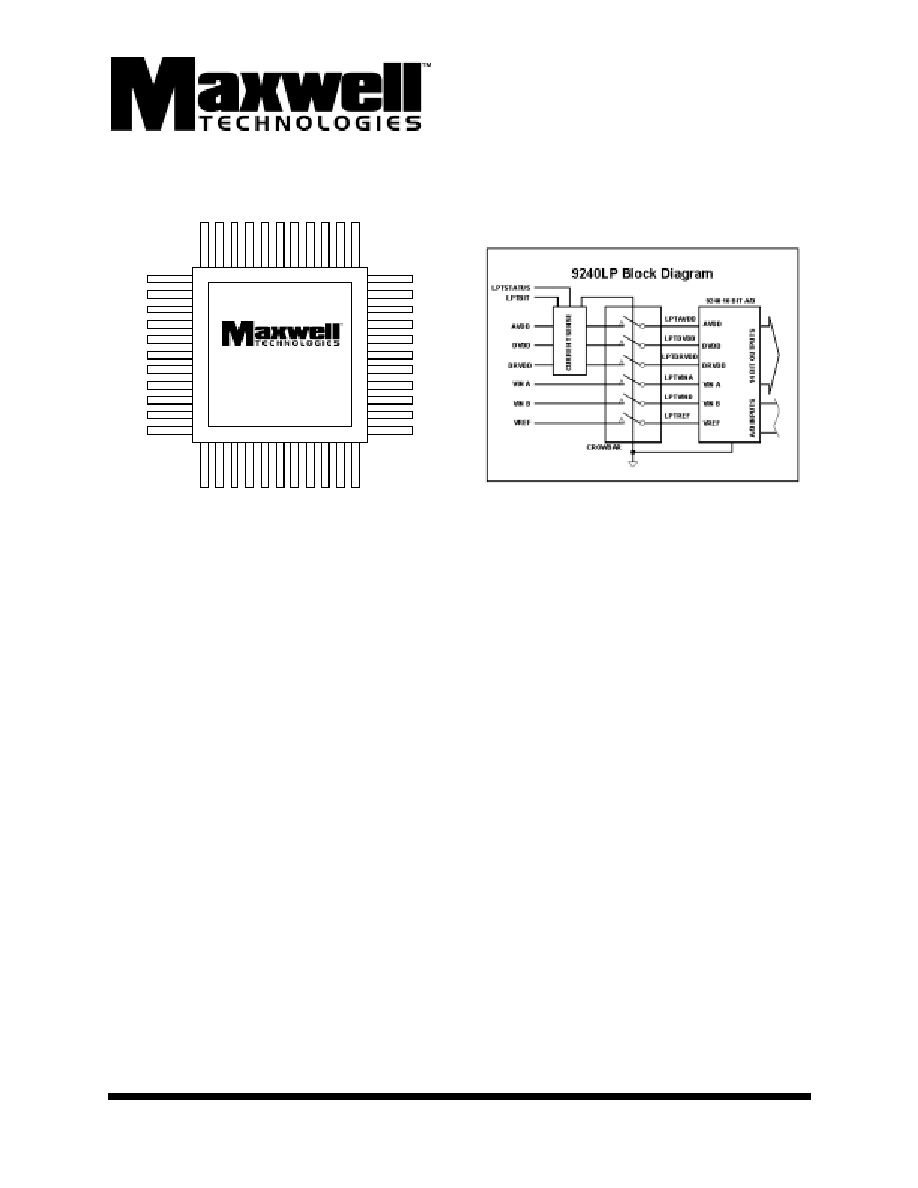

Maxwell Technologies' 9240LP is a 14-bit, analog-to-digital

converter that operates at a 10 MSPS rate. Manufactured with

a high speed CMOS process, this ADC contains an on-chip,

high performance, low noise, sample-and-hold amplifier and

programmable voltage reference.

The 9240LP offers single supply operation and dissipates only

480 mW with a 5 volt supply. This device provides no missing

codes and excellent temperature drift performance over the

full operating temperature range.

The 9240LP utilizes Maxwell's LPTTM Latchup Protection Cir-

cuit.

Maxwell Technologies' patented R

AD

-P

AK

Æ packaging technol-

ogy incorporates radiation shielding in the microcircuit pack-

age. It eliminates the need for box shielding while providing

the required radiation shielding for a lifetime in orbit or space

mission. In a GEO orbit, R

AD

-P

AK

provides protection to 100

krad (Si) radiation dose tolerance. This product is available

with screening up to Class K.

DVSS

A

VSS

DVDD

AV

D

D

NC

DR

V

D

D

CL

K

LPT

S

T

A

TU

S

LP

TB

I

T

NC

BIT

1

4

BIT 3

BIT 4

BIT 5

BIT 6

BIT 7

BIT 8

BIT 9

BIT 10

BIT 11

BIT 12

BIT 13

REF

C

OM

Vr

e

f

SENSE

NC

A

VSS

AV

D

D

NC

NC

OT

C

BIT

1

BI

T

2

NC

BIAS

CAPB

CAPT

CML

LPTref

VinA

LPTAVDD

LPTDVDD

VinB

NC

.

9240LP

M

e

m

o

r

y

2

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

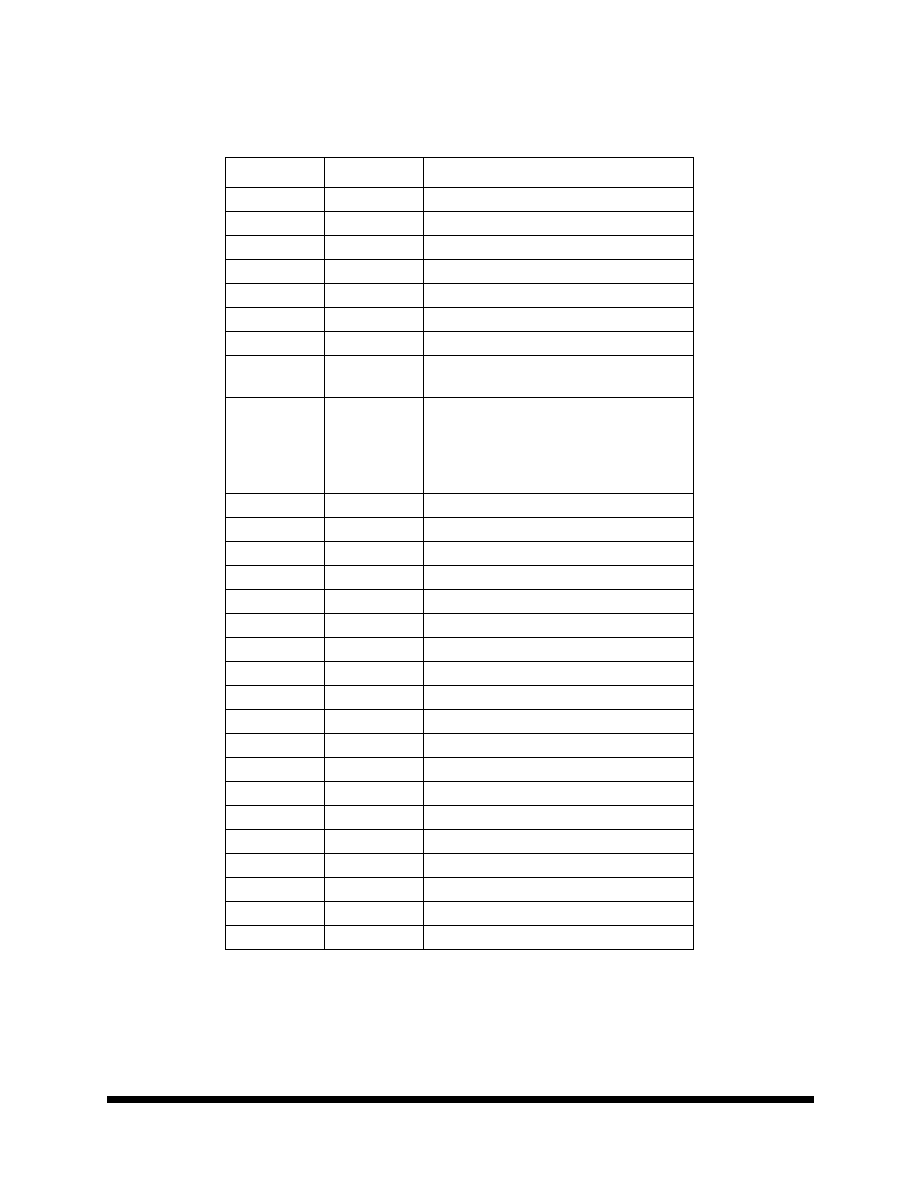

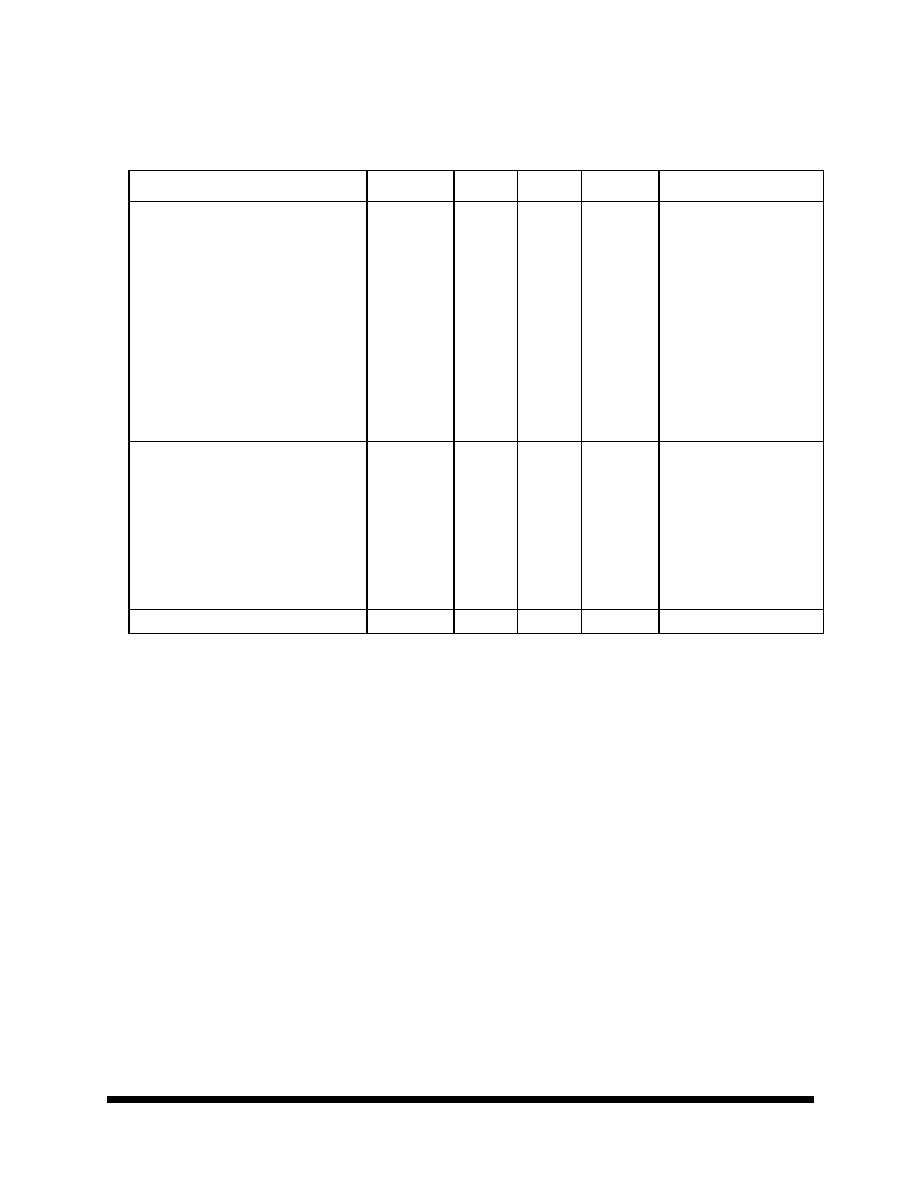

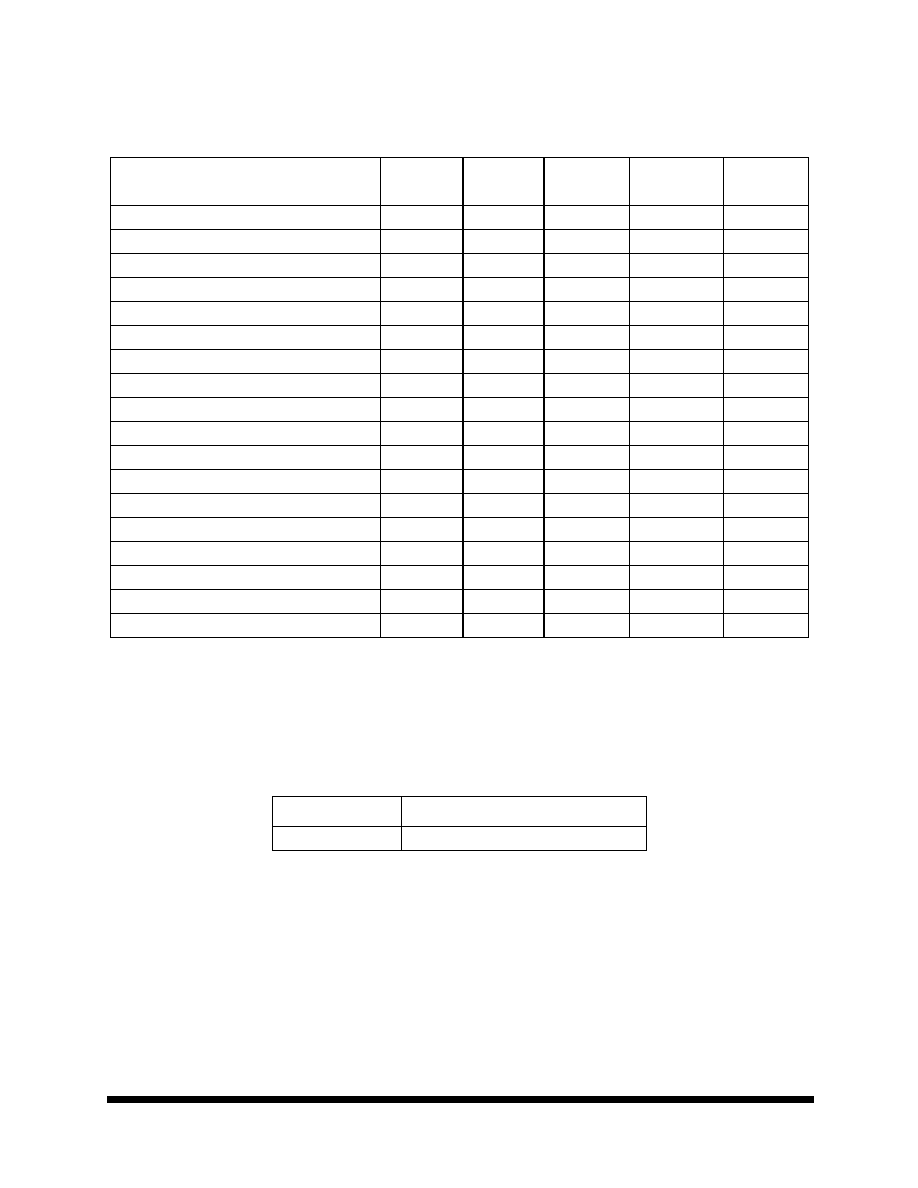

T

ABLE

1. 9240LP P

IN

D

ESCRIPTION

P

IN

N

UMBER

N

AME

D

ESCRIPTION

1

DVSS

Digital Ground

2, 29

AVSS

Analog Ground

3

DVDD

5V Digital Supply

4, 28

AVDD

5V Analog Supply

5

NC

No Connect

6

DRVDD

Digital Output Driver Supply

7

CLK

Clock Input Pin

8

LPTSTATUS

A 0 to 5V pulse is output during the decision

time and protect time. Normally low.

9

LPTBIT

The LPT circuit will crowbar the power supplies

to the 9240LP for as long as a logic high is

applied. Used to verify operation of the LPT.

Normally a logical low or ground is applied to

this input.

10

NC

No Connect

11

BIT 14

Least Significant Data Bit (LSB)

12-23

BIT 13-BIT 2

Data Output Bits

24

BIT 1

Most Significant Data Bits (MSB)

25

OTR

Out of Range

26, 27, 30

NC

No Connect

31

SENSE

Reference Select

32

V

REF

Reference I/O

33

REFCOM

Reference Common

34, 38

NC

No Connect

35

BIAS

1

1. See Speed/Power programmability section.

Power/Speed Programming

36

CAPB

Noise Reduction Pin

37

CAPT

Noise Reduction Pin

39

CML

Common-Mod Level (Midsupply)

40

LPTV

REF

Protected Reference I/O

41

V

IN

A

Analog Input Pin (+)

42

V

IN

B

Analog Input Pin (-)

43

LPTDVDD

Protected 5V Digital Supply

44

LPTAVDD

Protected 5V Analog Supply

M

e

m

o

r

y

3

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

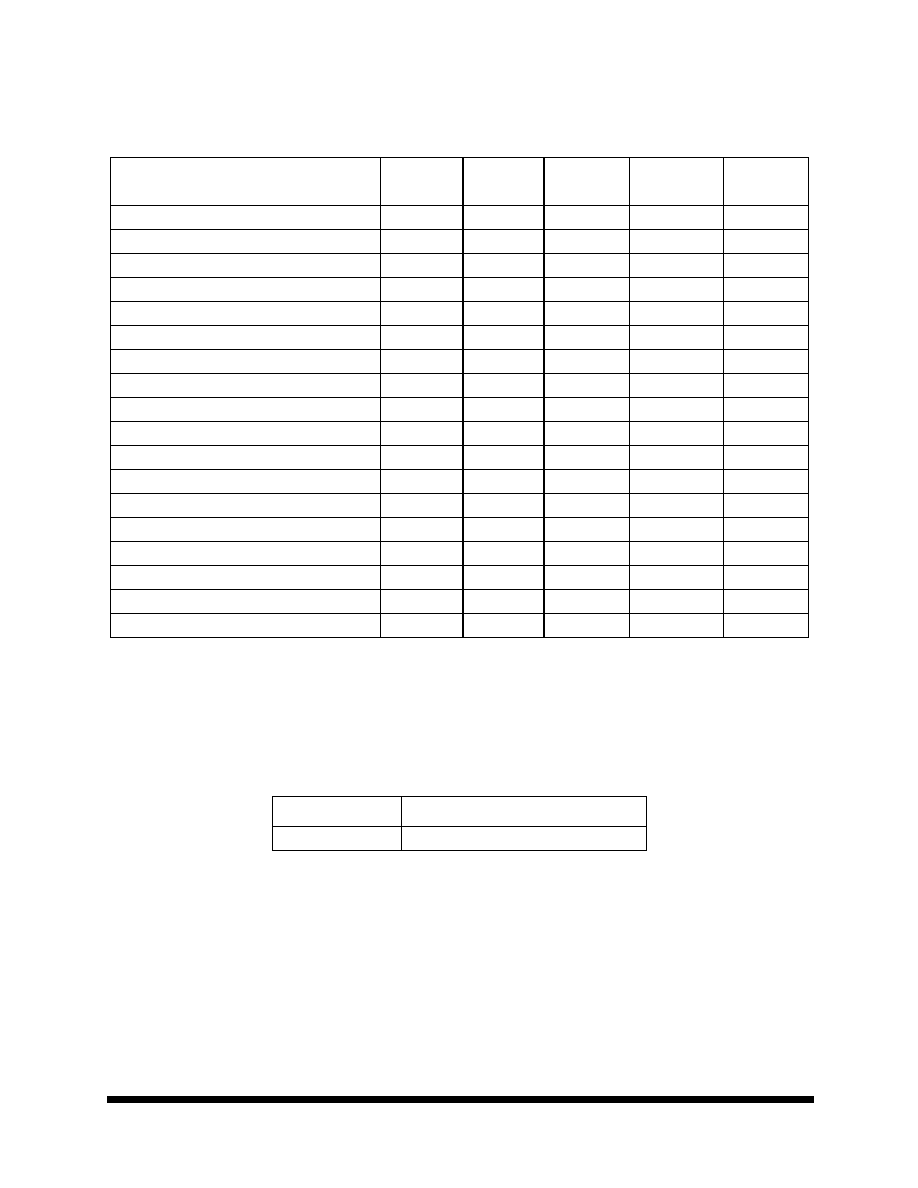

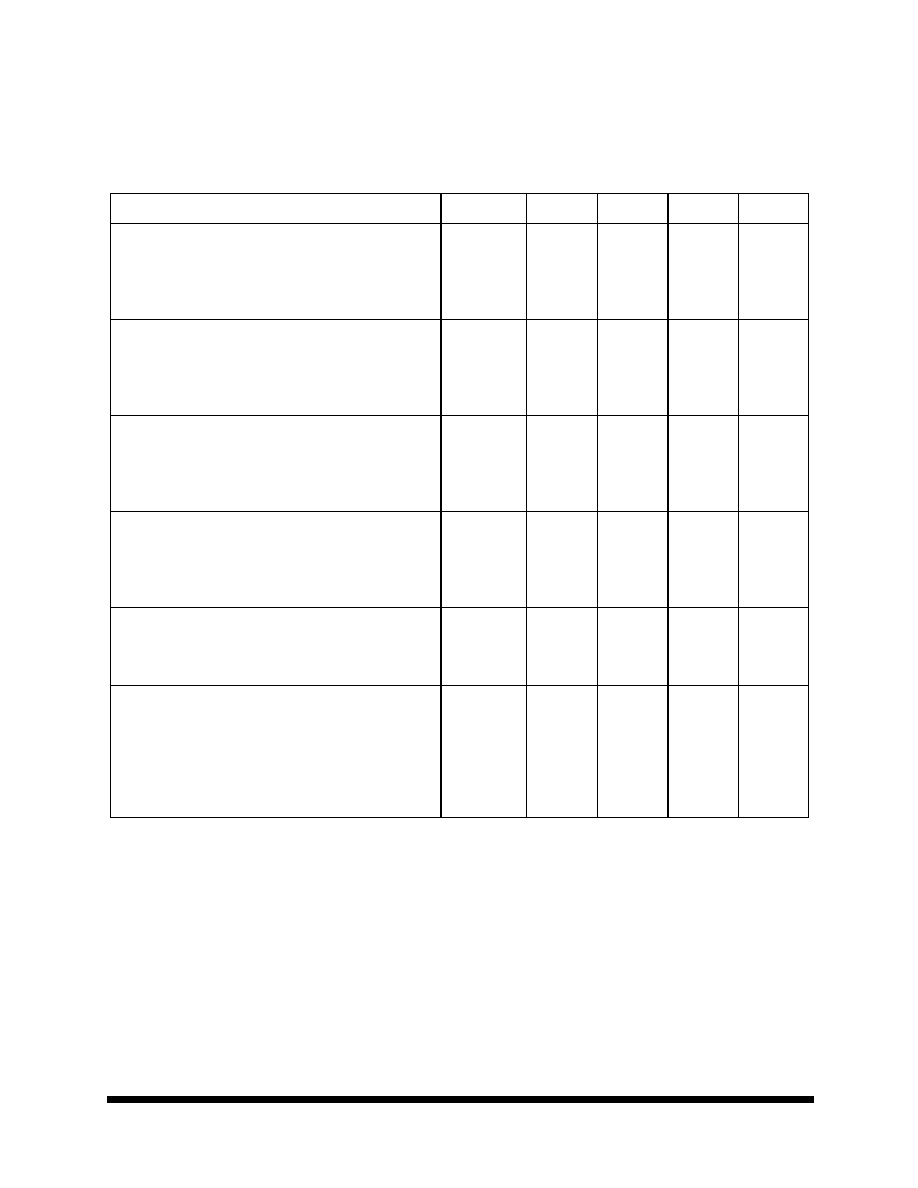

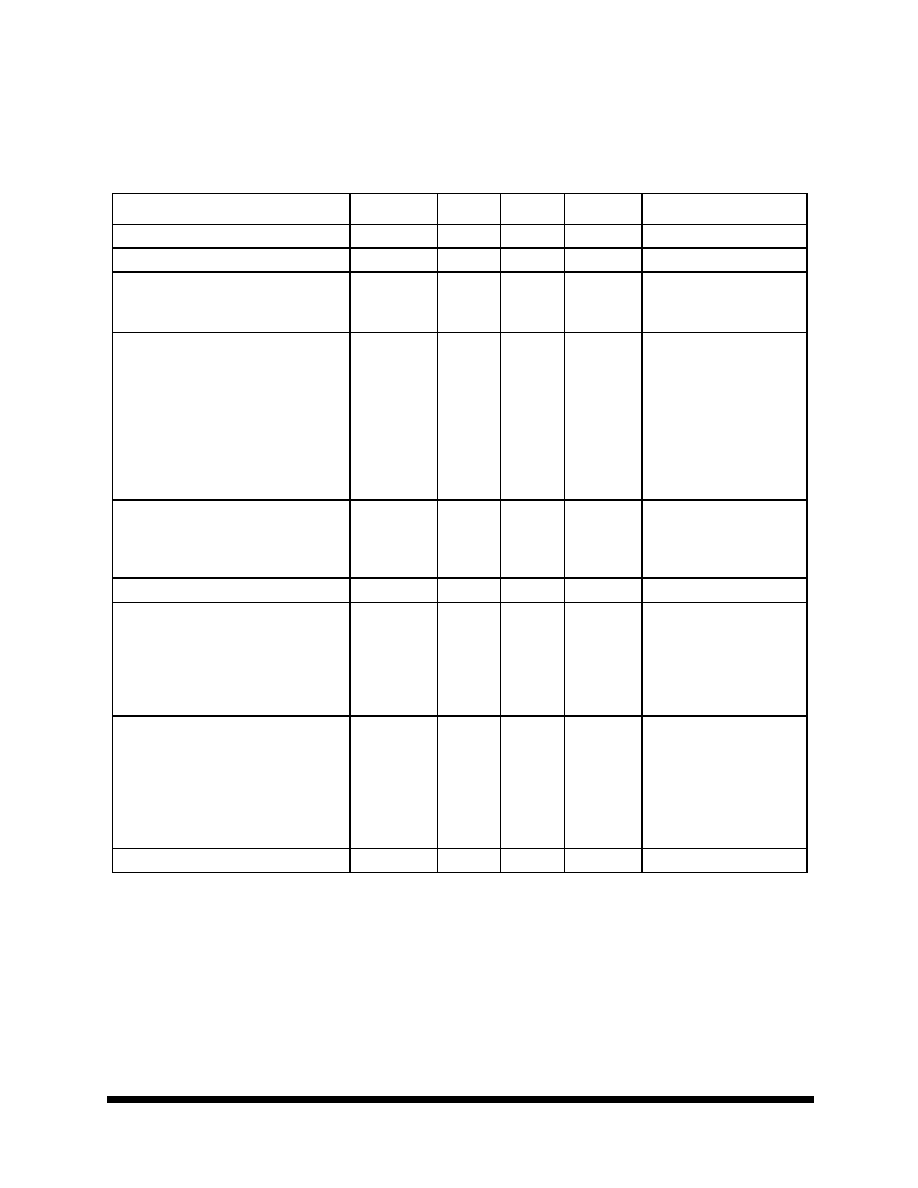

T

ABLE

2. 9240LP A

BSOLUTE

M

AXIMUM

R

ATINGS

1

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any other conditions above those indicated in the operational sec-

tions of this specification are not implied. Exposure to absolute maximum ratings for extended periods may effect device reli-

ability.

P

ARAMETER

S

YMBOL

W

ITH

R

ESPECT

T

O

M

IN

M

AX

U

NIT

+5 V Analog Supply

AVDD

AVSS

-0.3

6.5

V

+5 V Digital Supply

DVDD

DVSS

-0.3

6.5

V

Analog Ground

AVSS

DVSS

-0.3

0.3

V

+5 V Analog Supply

AVDD

DVDD

-6.5

6.5

V

Digital Output Driver Supply

DRVDD

DRVSS

-0.3

6.5

V

Digital Output Driver Ground

DRVSS

AVSS

-0.3

0.3

V

Reference Common

REFCOM

AVSS

-0.3

0.3

V

Clock Input Pin

CLK

AVSS

-0.3

AVDD

V

Digital Outputs

Data Out Bits

DRVSS

-0.3

DRVDD + 0.3

V

Analog Inputs

V

IN

A, V

IN

B

AVSS

-0.3

AVDD

V

Reference I/O

V

REF

AVSS

-0.3

AVDD

V

Reference Select

Sense

AVSS

-0.3

AVDD

V

Noise Reduction Pins

CAPB, CAPT

AVSS

-0.3

AVDD

V

Power/Speed Programming

BIAS

AVSS

-0.3

AVDD + 0.6

V

Junction Temperature

T

J

--

150

∞

C

Operating Temperature

T

A

-55

125

∞C

Storage Temperature

T

STG

-65

150

∞

C

Lead Temperature (10 sec)

T

L

--

300

∞

C

T

ABLE

3. D

ELTA

L

IMITS

P

ARAMETER

V

ARIATION

I

CC

±10%

OF

SPECIFIED

VALUE

IN

T

ABLE

4

M

e

m

o

r

y

4

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

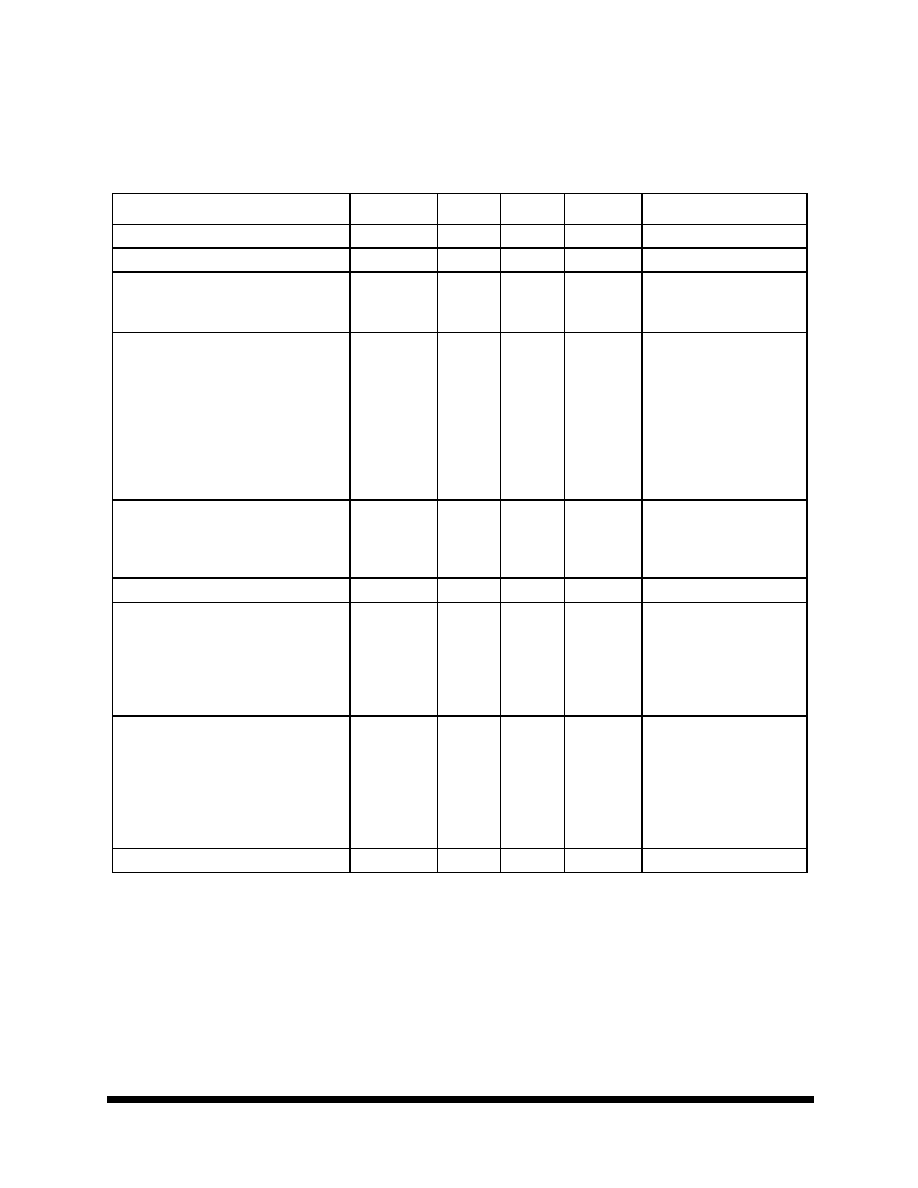

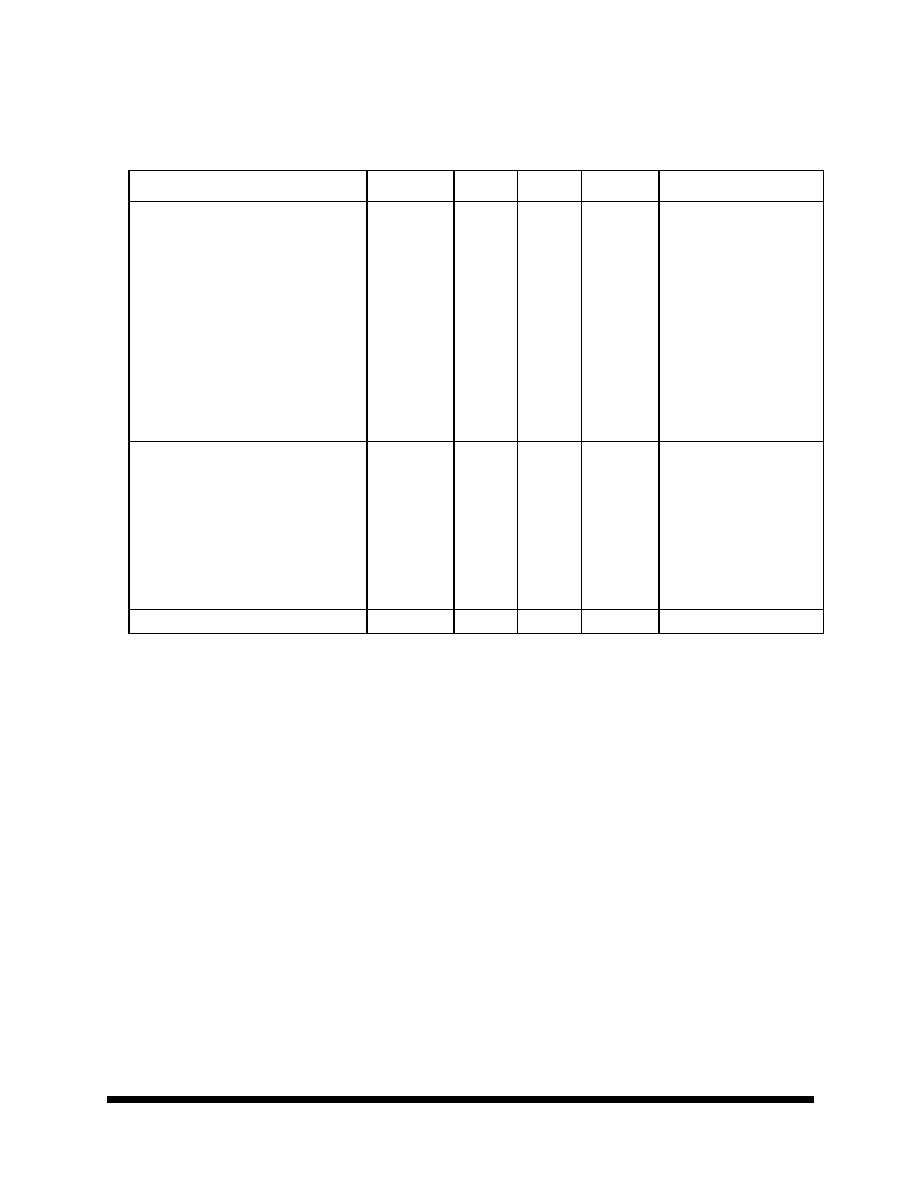

T

ABLE

4. 9240LP DC S

PECIFICATIONS

(AVDD = 5V, DVDD = 5V, DRVDD = 5V, R

BIAS

= 2

K

, V

REF

= 2.5V,V

IN

A = V

IN

B =± 2.5V D

IFFERENTIAL

I

NPUT

C

ENTERED

ON

V

REF

(1.25V

TO

3.75V A

BSOLUTE

), T

A

= -55

TO

+125∞C,

UNLESS

OTHERWISE

SPECIFIED

)

P

ARAMETER

S

UBGROUPS

M

IN

T

YP1

M

AX

U

NIT

RESOLUTION

1

14

--

--

Bits

MAX CONVERSION RATE

9, 10, 11

10

--

--

MHz

MAX REFERRED NOISE

1

V

REF

= 1 V

V

REF

= 2.5V

--

--

0.9

0.36

--

--

LSB rms

LSB rms

ACCURACY

2

Integral Nonlinearity (INL)

Differential Nonlinearity (DNL)

INL

3

DNL

3

No Missing Codes

Zero Error (@ 25 ∞C)

Gain Error (@ 25 ∞C)

4,1

Gain Error (@ 25 ∞C)

5

1, 2, 3

1, 2, 3

1, 2, 3

1

1

--

1

--3.0

--

--

--

--

--3

--1.5

--0.75

±2.5

±0.6

±2.5

±0.7

--

--

--

+3.0

±1.0

--

--

14

+3

1.5

0.75

LSB

LSB

LSB

LSB

Bits Guaranteed

% FSR

% FSR

% FSR

TEMPERATURE DRIFT

Zero Error

Gain Error

4

Gain Error

5

1, 2, 3

--

--

--

3.0

20.0

5.0

--

--

--

ppm/∞C

ppm/∞C

ppm/∞C

POWER SUPPLY REJECTION

1, 2, 3

--

--

0.1

% FSR

ANALOG INPUT

1

Input Span (with V

REF

= 1.0 V)

1

(with V

REF

= 2.5 V)

Input (V

IN

A or V

IN

B) Range

Input Capacitance

1

1, 2, 3

--

2

--

0

--

--

--

--

--

--

16

--

5

--

AVDD +.25

--

V p-p

V p-p

V

V

pF

INTERNAL VOLTAGE REFERENCE

1

Output Voltage (1V mode)

Output Voltage Tolerance (1 V Mode)

Output Voltage (2.5 V Mode)

Output Voltage Tolerance (2.5 V Mode)

Load Regulation V

REF

6

Load Regulation LPTV

REF

1, 6, 7

--

--

--

--

--

--

--

1

--

2.5

--

10

--

--

±14

--

±35

--

10.0

Volts

mV

Volts

mV

mV

mV

REFERENCE INPUT RESISTANCE

1, 2, 3

--

5

--

k

M

e

m

o

r

y

5

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

LPT ASIC

RDS ON

- V

REF

- V

IN

A

- V

IN

B

LATCHUP PROTECTION

- Decision Time

- Protect Time

- AVDD Trip Current

- AVDD Trip Current Tolerance

- DVDD Trip Current

- DVDD Trip Current Tolerance

1, 2, 3

--

--

--

--

--

--

--

--

--

8

8

105

105

10

70

75

±15

28

±5

15

--

--

--

--

--

--

--

--

--

ohm

ohm

ohm

ohm

µ s

µ s

mA

mA

mA

mA

POWER SUPPLIES

Supply Voltages

- AVDD

- DVDD

- DRVDD

Supply Current

- IAVDD

- IDVDD

1, 2, 3

1, 2, 3

--

--

--

--

--

5

5

5

43

3

--

--

--

55

16

V (±5% AVDD Operating)

V (±5% DVDD Operating)

V (±5% DRVDD Operating)

mA

mA

POWER CONSUMPTION

8

1, 2, 3

295

355

mW

1. Guaranteed by design.

2. Tested using external V

REF

with servo control

3. V

REF

= 1V

4. Including internal reference.

5. Excluding internal reference.

6. Load regulation with 1 mA load current.

7. LPTV

REF

should not be capacitively loaded above 0.1 µ F.

8. Calculated from I

DD

T

ABLE

4. 9240LP DC S

PECIFICATIONS

(AVDD = 5V, DVDD = 5V, DRVDD = 5V, R

BIAS

= 2

K

, V

REF

= 2.5V,V

IN

A = V

IN

B =± 2.5V D

IFFERENTIAL

I

NPUT

C

ENTERED

ON

V

REF

(1.25V

TO

3.75V A

BSOLUTE

), T

A

= -55

TO

+125∞C,

UNLESS

OTHERWISE

SPECIFIED

)

P

ARAMETER

S

UBGROUPS

M

IN

T

YP1

M

AX

U

NIT

M

e

m

o

r

y

6

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

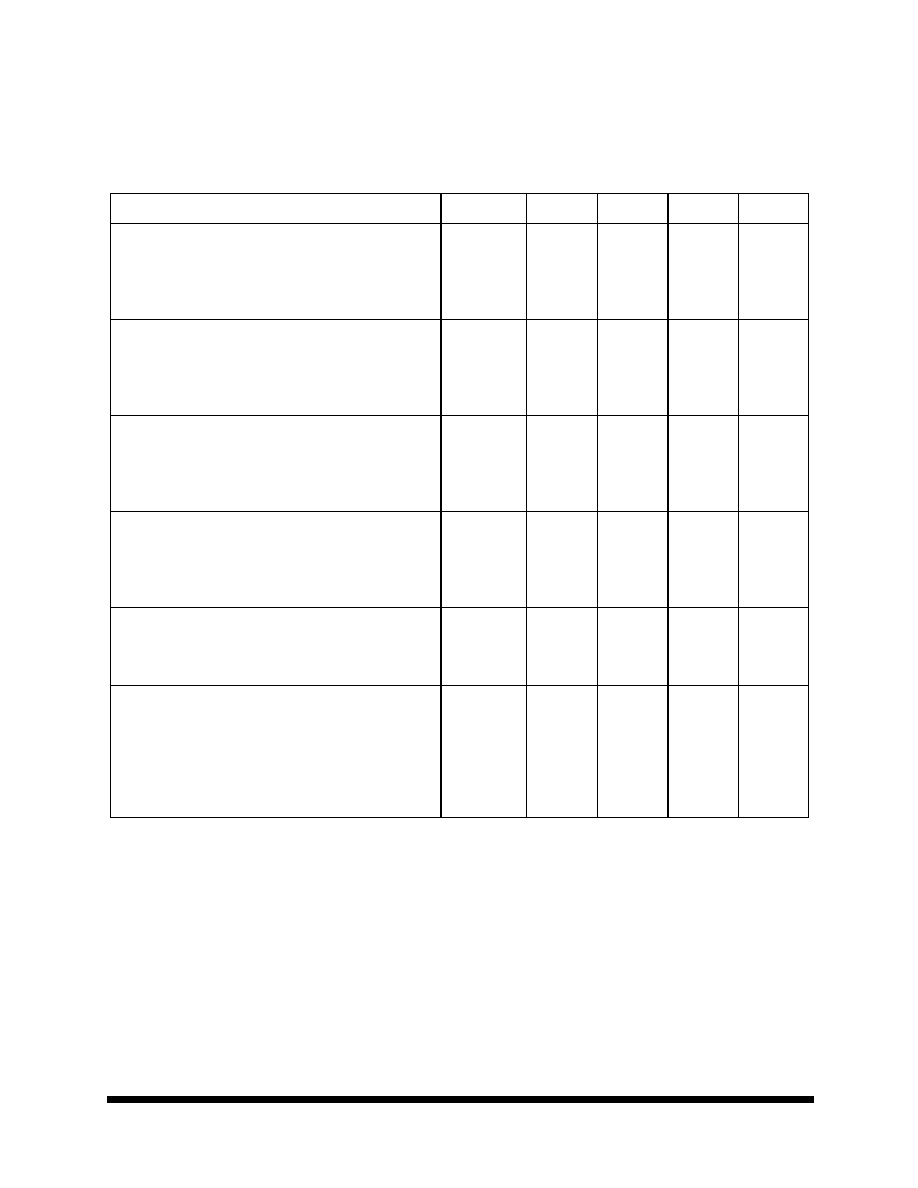

T

ABLE

5. 9240LP AC S

PECIFICATIONS

(AVDD = 5V, DVDD = 5V, DRVDD = 5V, f

SAMPLE

= 10 MSPS, R

BIAS

= 2

K

, V

REF

= 2.5V, A

IN

= -0.5 dBFS, AC C

OUPLED

/D

IFFERENTIAL

I

NPUT

, T

A

= -55

TO

+125∞C,

UNLESS

OTHERWISE

SPECIFIED

)

P

ARAMETER

S

UBGROUPS

M

IN

T

YP

M

AX

U

NIT

SIGNAL-TO-NOISE AND DISTORTION RATIO (S/N+D)

f

INPUT

= 500 KHz

f

INPUT

= 1.0 MHz

f

INPUT

= 5.0 MHz

--

--

--

76.0

76

75.5

--

--

--

dB

dB

dB

dB

EFFECTIVE NUMBER OF BITS (ENOB)

1

f

INPUT

= 500 KHz

f

INPUT

= 1.0 MHz

f

INPUT

= 5.0 MHz

1. ENOB calculated from SNR.

12

--

--

--

--

12.5

12.3

11.9

--

--

--

--

Bits

Bits

Bits

Bits

SIGNAL-TO-NOISE RATIO (SNR)

f

INPUT

= 500 KHz

f

INPUT

= 1.0 MHz

f

INPUT

= 5.0 MHz

4, 5, 6

74.5

--

--

--

77

77

77

77

--

--

--

--

dB

dB

dB

dB

TOTAL HARMONIC DISTORTION (THD)

f

INPUT

= 500 KHz

f

INPUT

= 1.0 MHz

f

INPUT

= 5.0 MHz

--

--

--

--

-76.0

-83.0

-75.0

--

--

--

--

dB

dB

dB

dB

SPURIOUS FREE DYNAMIC RANGE

f

INPUT

= 500 KHz

f

INPUT

= 1.0 MHz

f

INPUT

= 5.0 MHz

4, 5, 6

--

--

--

90.0

90.0

80.0

--

--

--

dB

dB

dB

DYNAMIC PERFORMANCE

2

Full Power Bandwidth

Small Signal Bandwidth

Aperture Delay

Aperture Jitter

Acquisition to Full-Scale Step (0.0025%)

Overvoltage Recovery Time

2. Guaranteed by design.

--

--

--

--

--

--

70

70

1

4

45

167

--

--

--

--

--

--

MHz

MHz

ns

ps rms

ns

ns

M

e

m

o

r

y

7

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

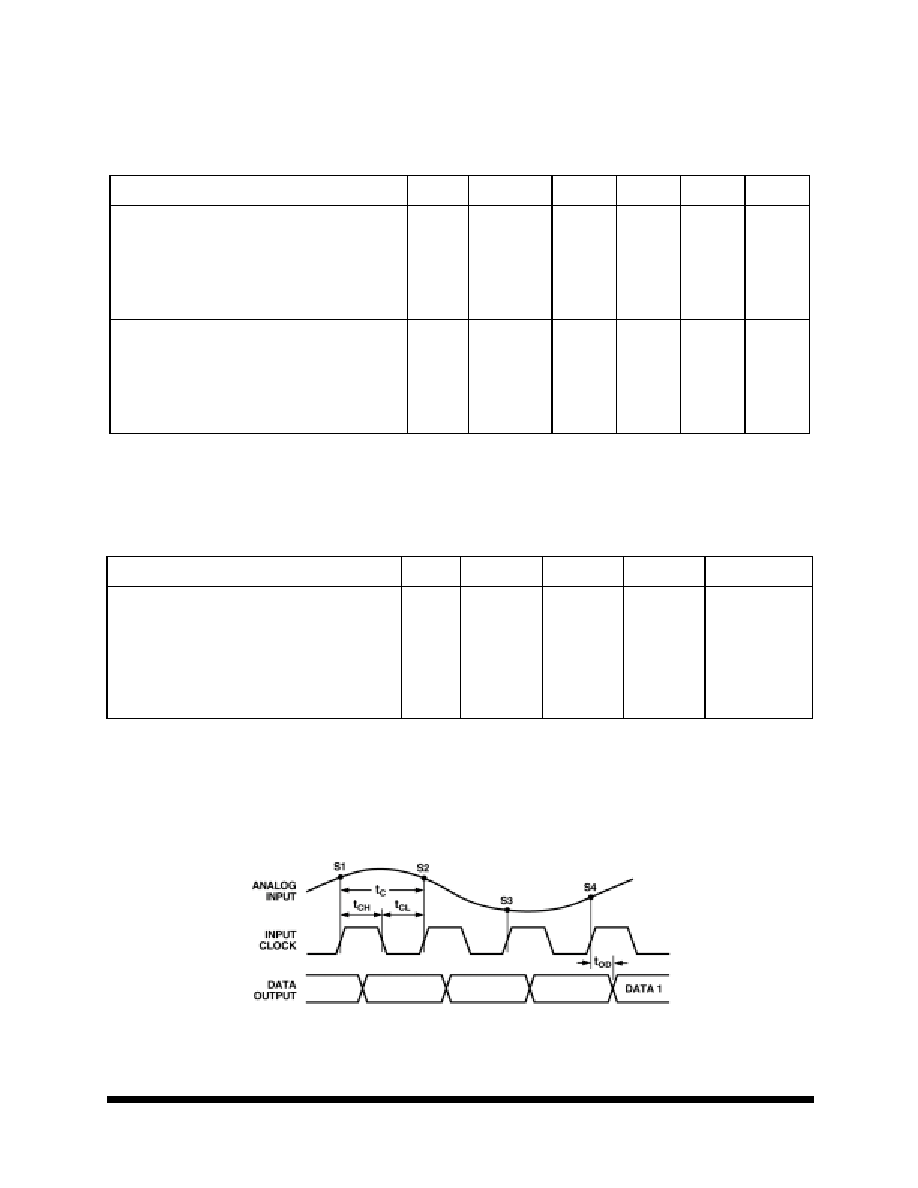

T

ABLE

6. 9240LP D

IGITAL

S

PECIFICATIONS

(AVDD = 5V, DVDD = 5V, T

A

= -55

TO

+125∞C,

UNLESS

OTHERWISE

SPECIFIED

)

P

ARAMETER

S

YMBOL

S

UBGROUPS

M

IN

T

YP

M

AX

U

NIT

CLOCK INPUT

High Level Input Voltage

1

Low Level Input Voltage

1

High Level Input Current (V

IN

= DVDD)

Low Level Input Current (V

IN

= 0V)

Input Capacitance

1. Guaranteed by design.

V

IH

V

IL

I

IH

I

IL

C

IN

1, 2, 3

--

--

--

--

--

--

--

--

--

5

3.5

1.0

±10

±10

--

V

V

µ A

µ A

pF

LOGIC OUTPUTS (with DRVDD = 5V)

High Level Output Voltage (I

OH

= 50 µ A)

High Level Output Voltage (I

OH

= 0.5 mA)

Low Level Output Voltage (I

OL

= 1.6 mA)

Low Level Output Voltage (I

OL

= 50 µ A)

Output Capacitance

1

V

OH

V

OH

V

OL

V

OL

C

OUT

1, 2, 3

4.5

2.4

--

--

--

--

--

--

--

5

--

--

0.4

0.1

5

V

V

V

V

pF

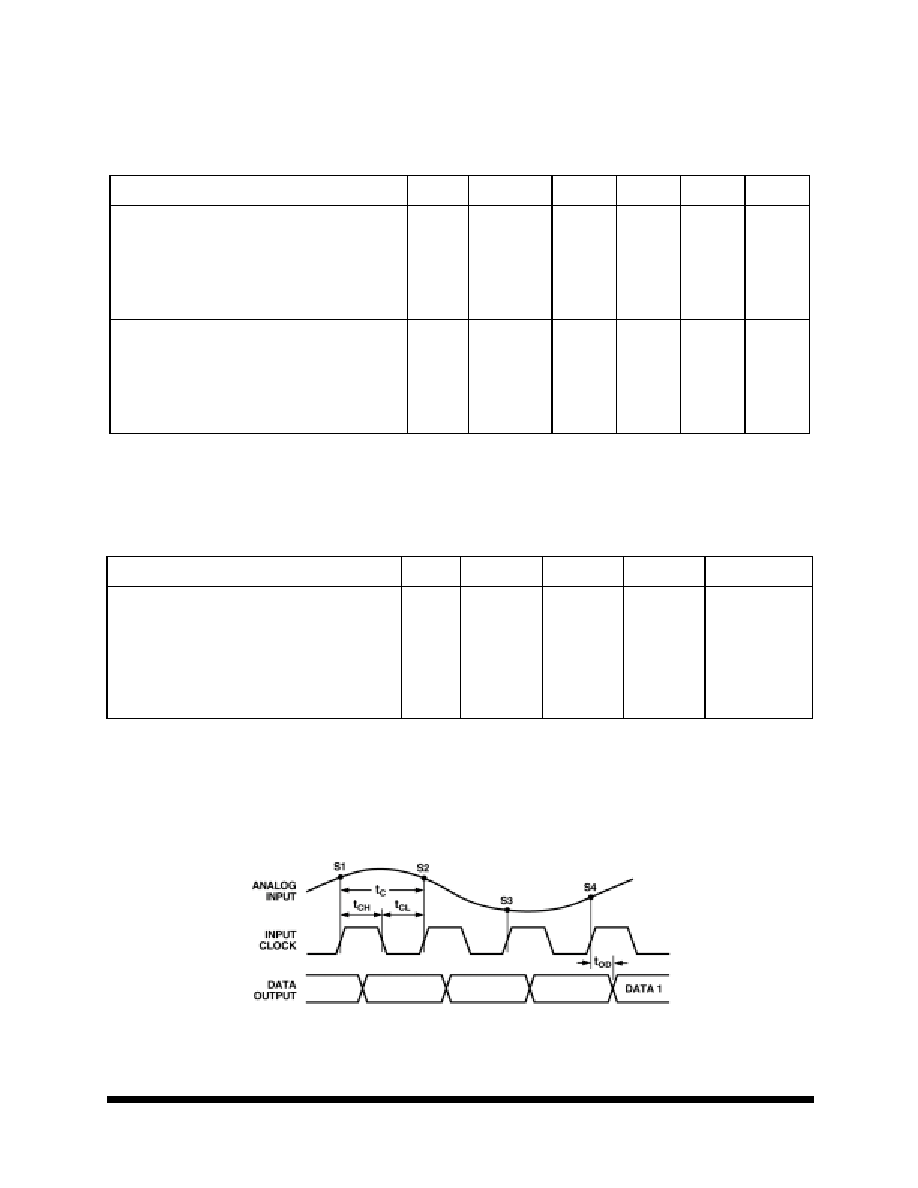

T

ABLE

7. 9240LP S

WITCHING

C

HARACTERISTICS1

(T

A

= -55

TO

+125∞C

WITH

AVDD = 5V, DVDD = 5V, DRVDD = 5V, R

BIAS

= 2

K

W, C

L

= 20

P

F)

1. Guaranteed by design.

T

IMING

D

IAGRAM

P

ARAMETER

S

YMBOL

M

IN

T

YP

M

AX

U

NITS

Clock Period

CLOCK Pulse width High

CLOCK Pulse width Low

Output Delay

Pipeline Delay (Latency)

t

C

t

CH

t

CL

t

OD

100

45

45

8

--

--

--

--

--

--

--

13

--

--

--

--

--

--

--

19

--

ns

ns

ns

ns

ns

ns

Clock Cycles

M

e

m

o

r

y

8

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

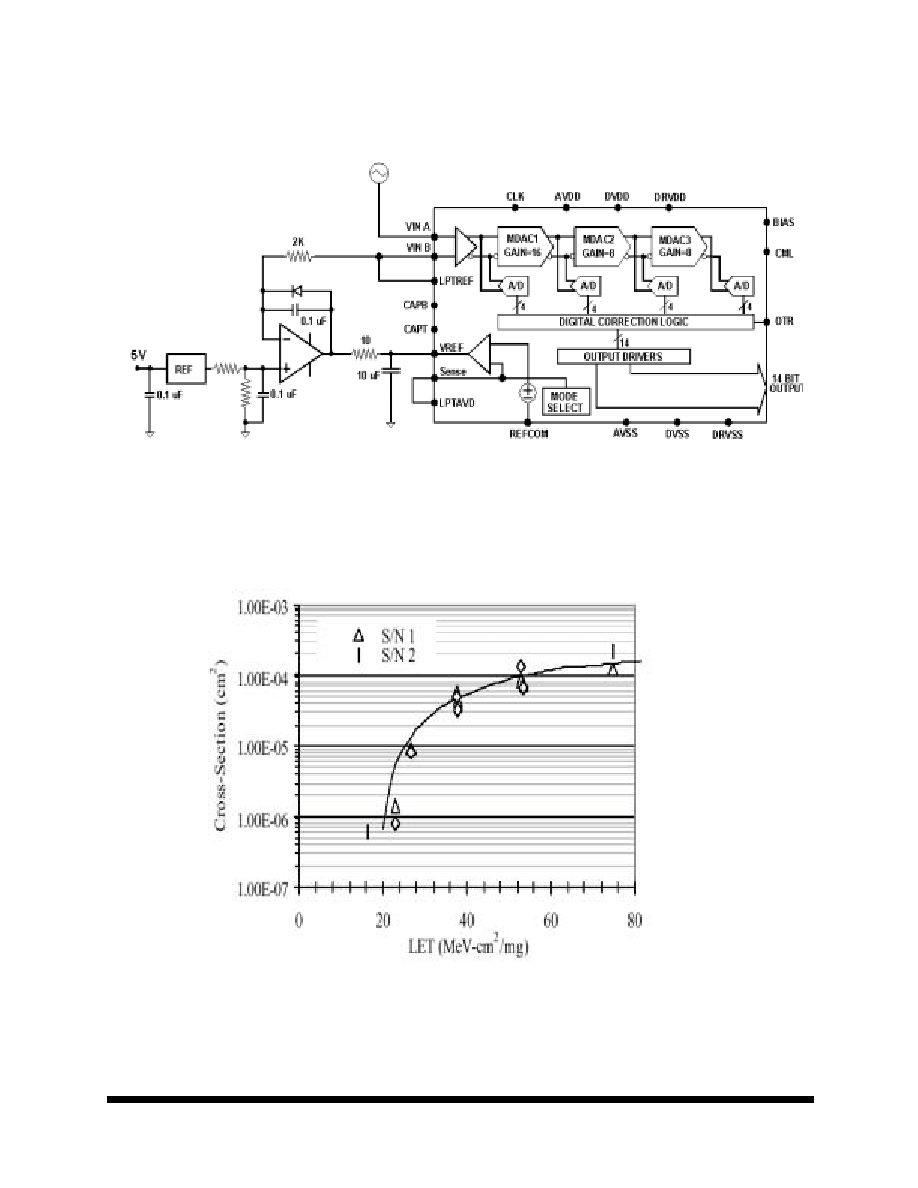

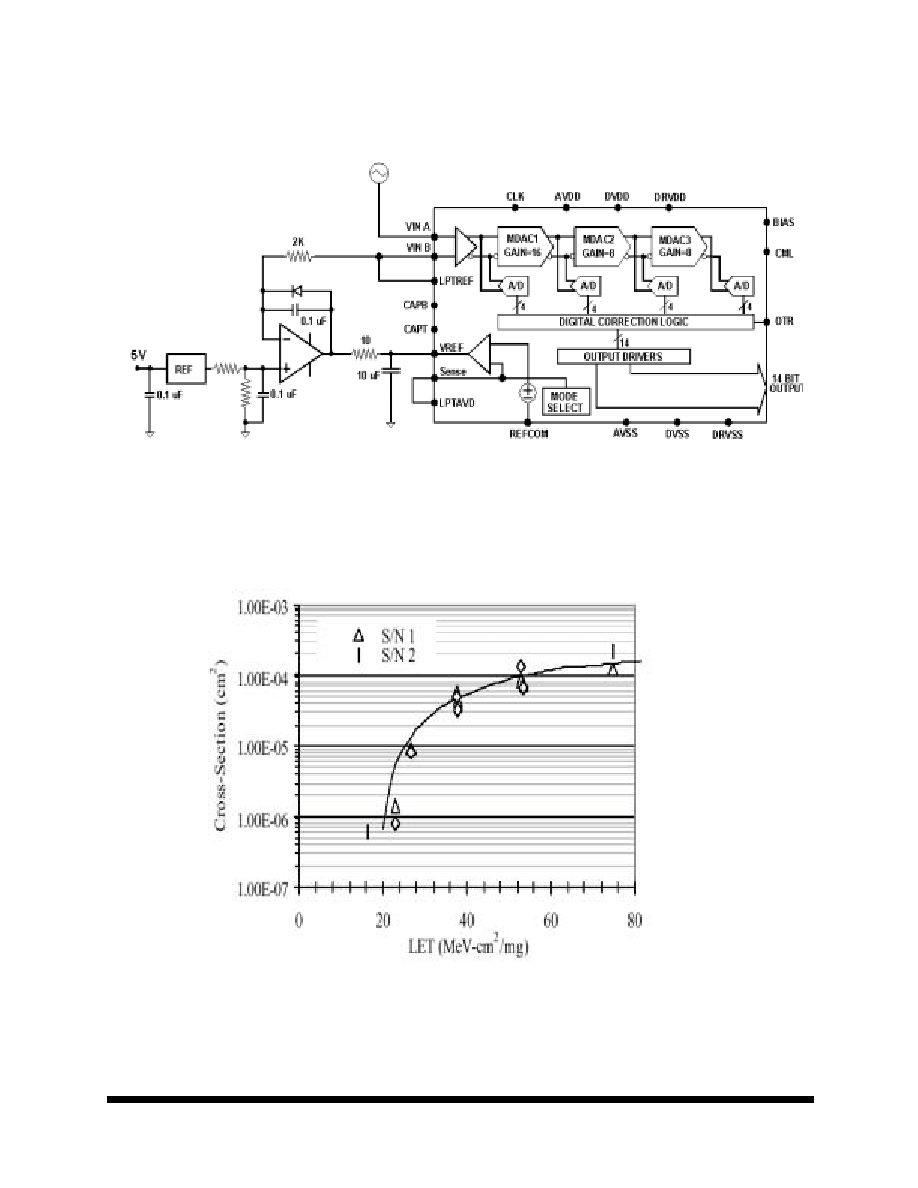

R

ECOMMENDED

E

XTERNAL

R

EFERENCE

M

e

m

o

r

y

9

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

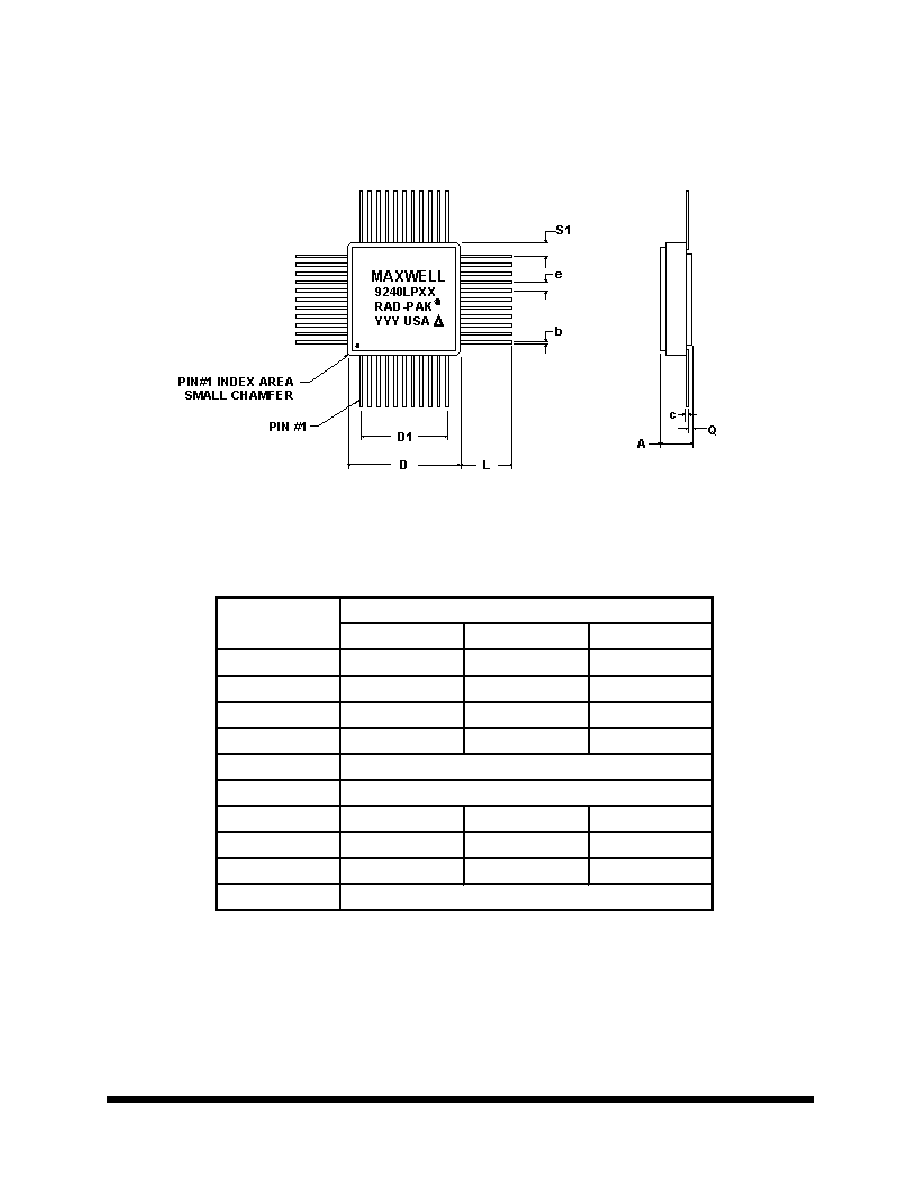

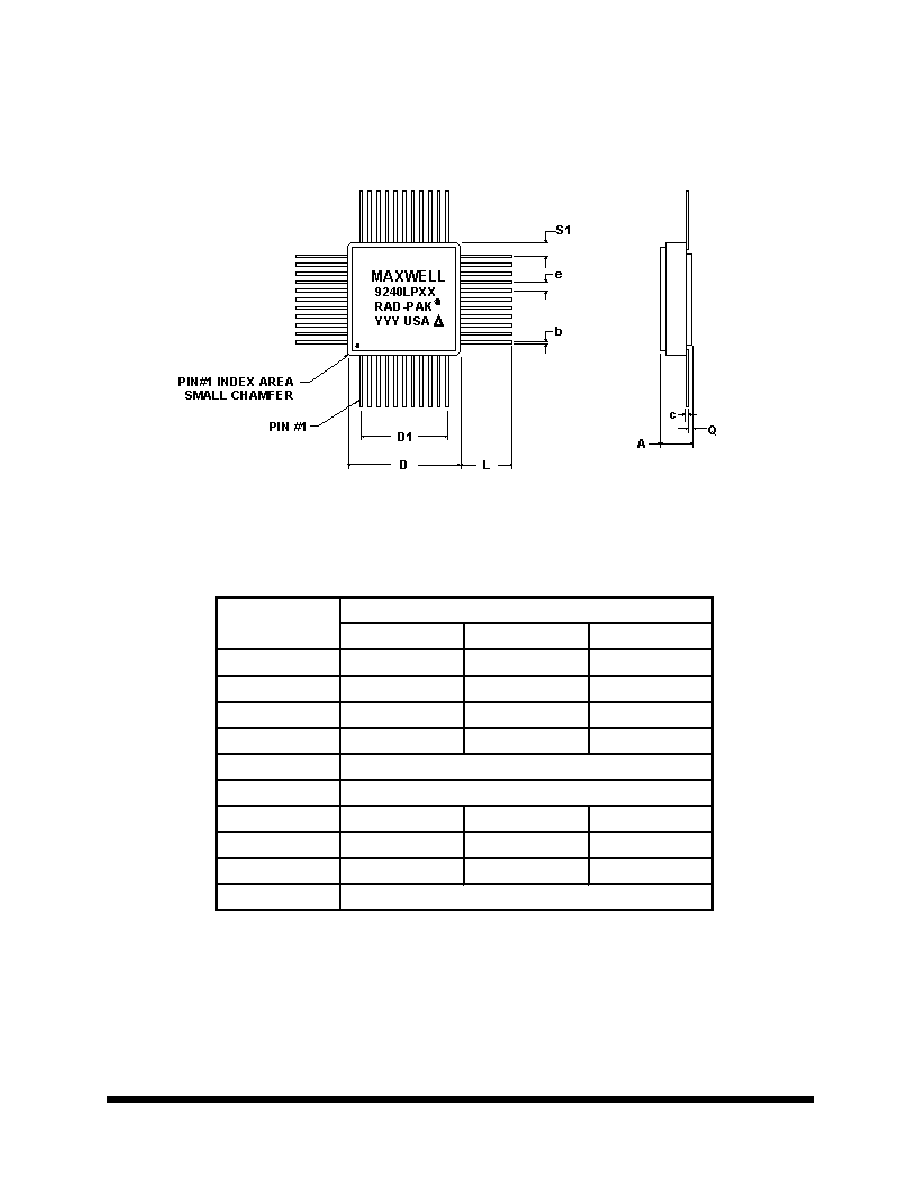

DIMENSIONS

SYMBOL

MIN

NOM

MAX

A

0.185

0.205

0.225

b

0.015

0.017

0.019

c

0.008

0.010

0.012

D

0.643

0.650

0.657

D1

0.050BSC

e

0.050

S1

0.005

0.067

--

L

0.260

0.270

0.280

Q

0.020

0.025

0.030

N

44.000

44 PIN RAD-PAK

Æ

QUAD FLAT PACKAGE

Q44-06

NOTE: ALL DIMENSIONS ARE IN INCHES

M

e

m

o

r

y

10

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

Important Notice:

These data sheets are created using the chip manufacturer's published specifications. Maxwell Technologies verifies

functionality by testing key parameters either by 100% testing, sample testing or characterization.

The specifications presented within these data sheets represent the latest and most accurate information available to

date. However, these specifications are subject to change without notice and Maxwell Technologies assumes no

responsibility for the use of this information.

Maxwell Technologies' products are not authorized for use as critical components in life support devices or systems

without express written approval from Maxwell Technologies.

Any claim against Maxwell Technologies must be made within 90 days from the date of shipment from Maxwell Tech-

nologies. Maxwell Technologies' liability shall be limited to replacement of defective parts.

M

e

m

o

r

y

11

All data sheets are subject to change without notice

©2002 Maxwell Technologies

All rights reserved.

14-Bit, 10 MSPS Monolithic A/D Converter with LPT ASIC

9240LP

06.13.02 Rev 5

Product Ordering Options

Model Number

Feature

Option Details

9240LP

RP

Q

X

Screening Flow

Package

Radiation Feature

Base Product

Nomenclature

MCM

K= Maxwell Class K

H= Maxwell Class H

I = Industrial (testing @ -55∞C,

+25∞C, +125∞C)

E = Engineering (testing @ +25∞C)

Q = Quad Flat Pack

RP = R

AD

-P

AK

Æ package

14-Bit, 10MSPS Monolithic A/D

Converter with LPT ASIC